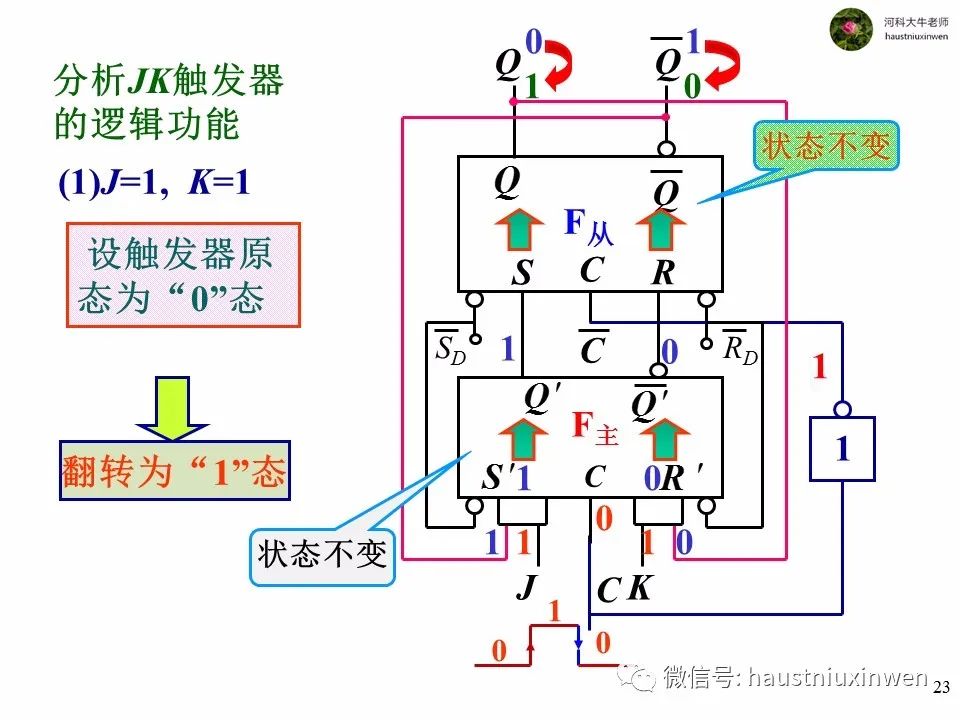

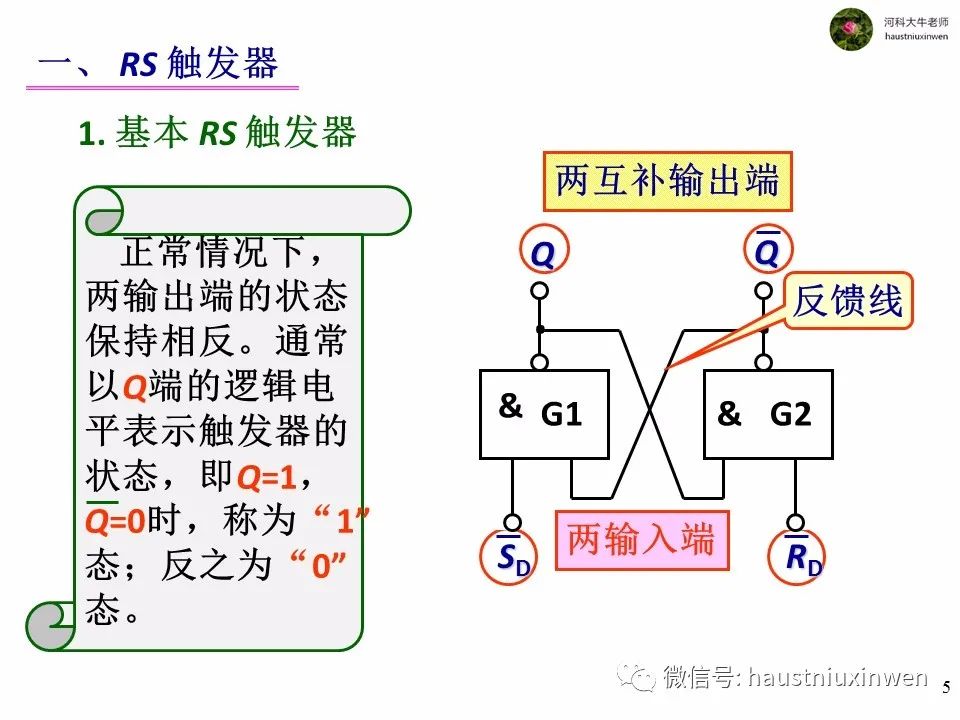

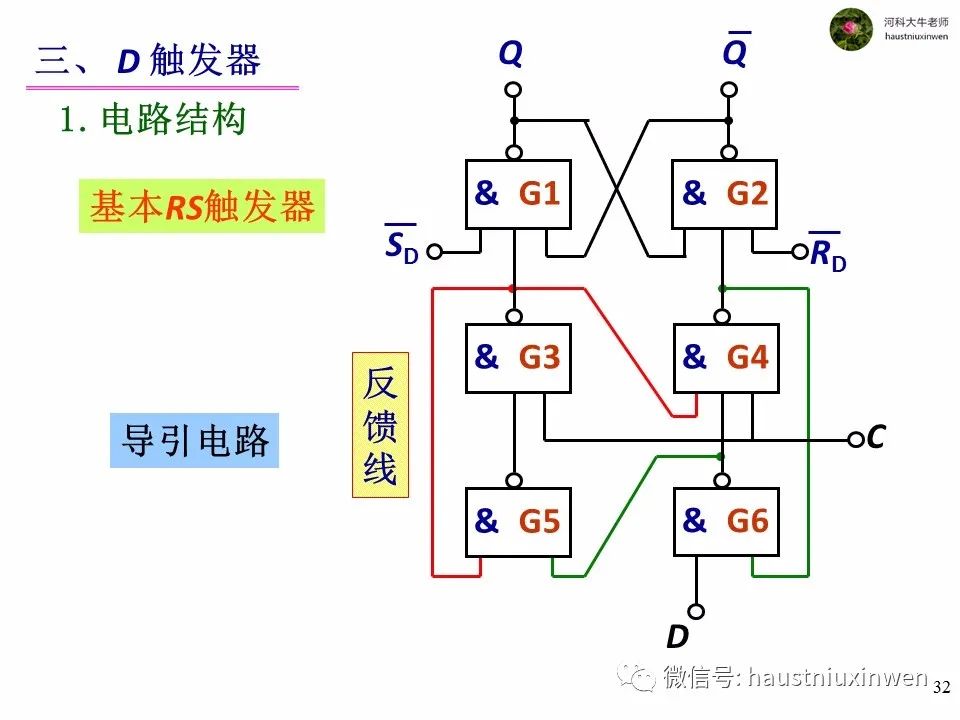

時(shí)序邏輯電路與組合邏輯電路的區(qū)別在于,時(shí)序邏輯電路的輸出并不僅僅由輸入條件決定,還由輸出的前一個(gè)狀態(tài)有關(guān)。也就是說,當(dāng)輸入改變時(shí),不能唯一確定輸出是什么,還要看輸入改變前輸出是什么狀態(tài),一起決定后面的輸出狀態(tài)。簡(jiǎn)而言之,這是一個(gè)有反饋的電路。

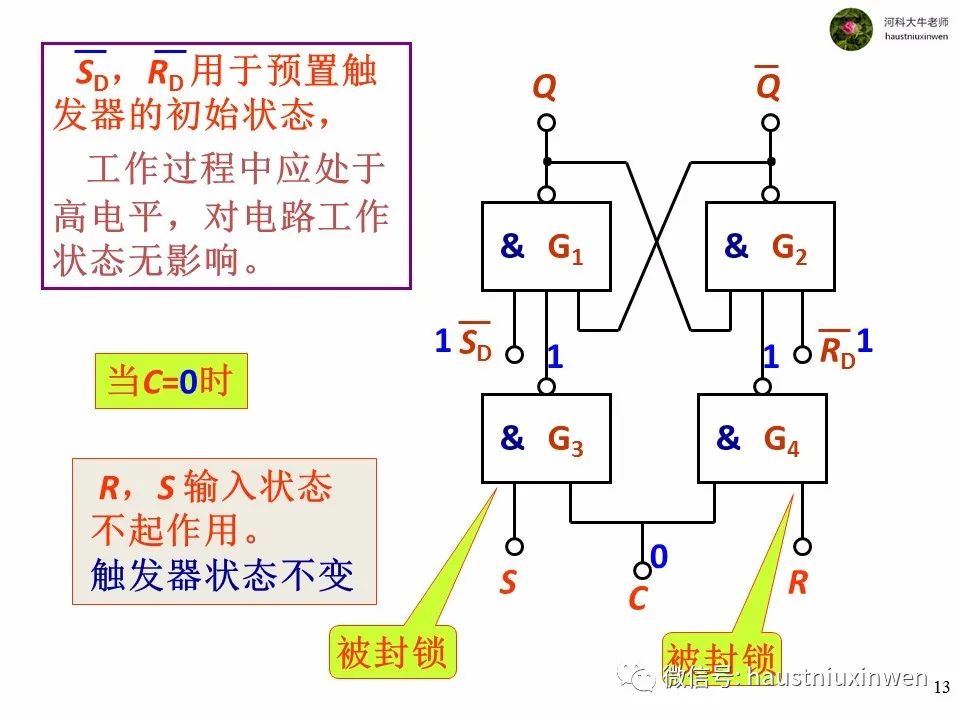

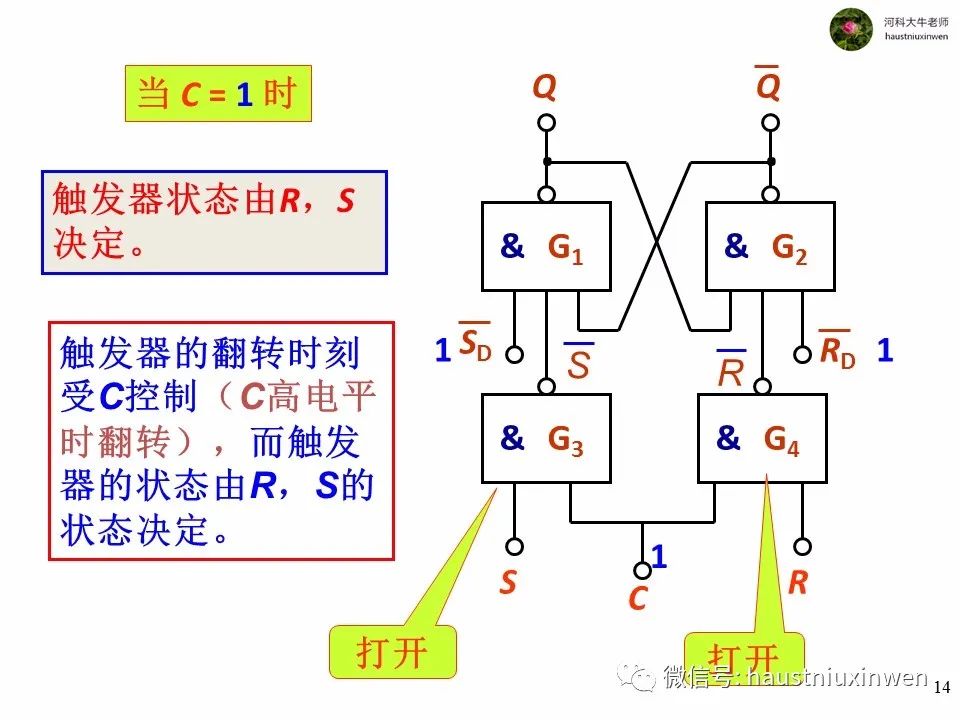

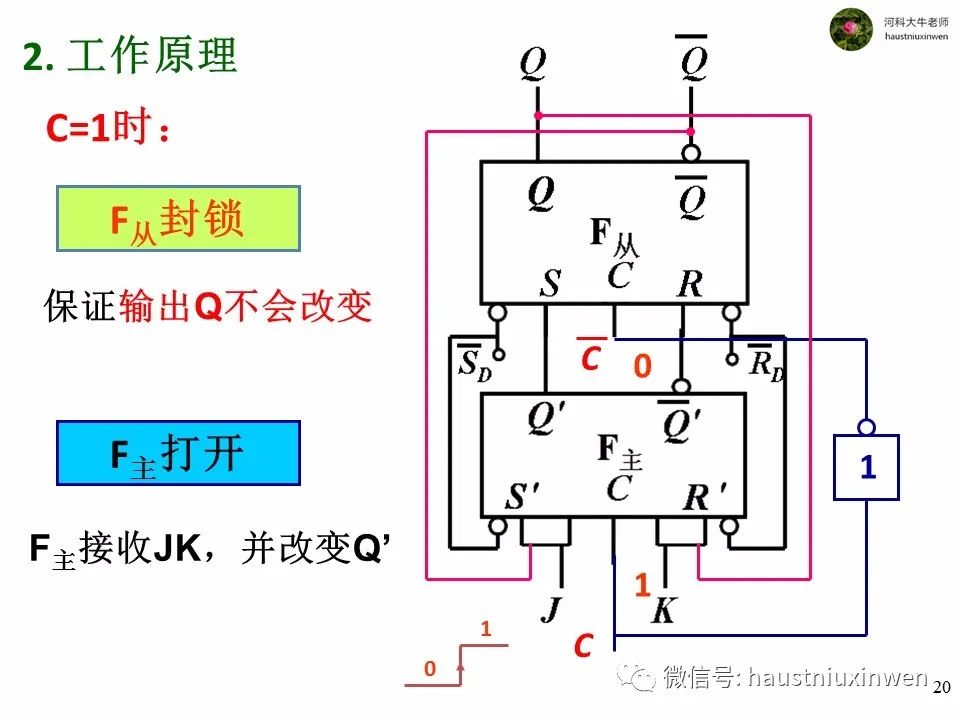

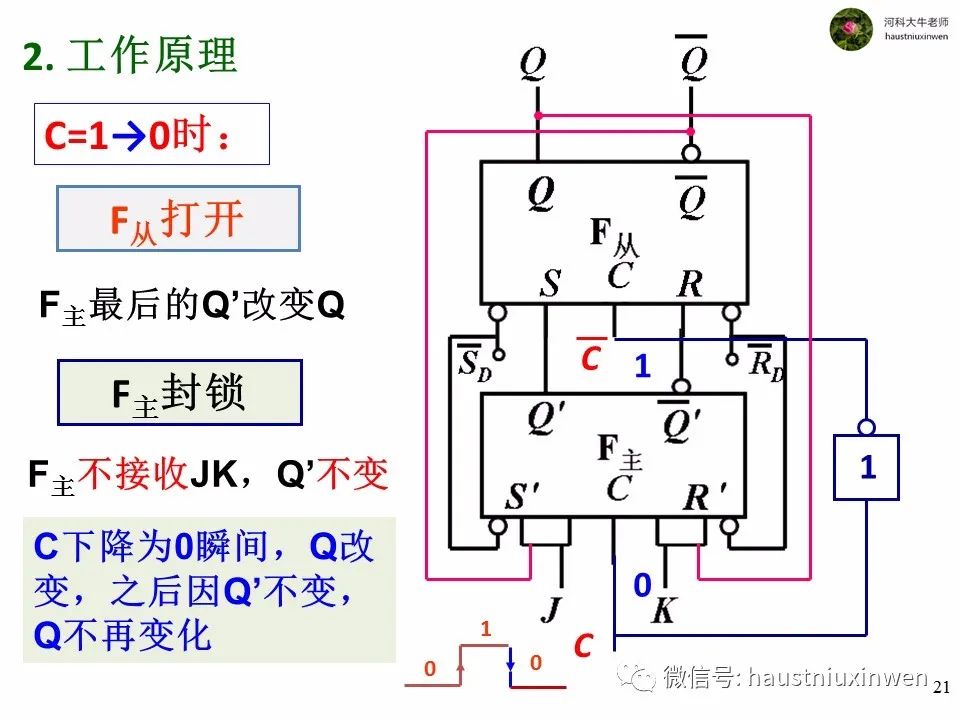

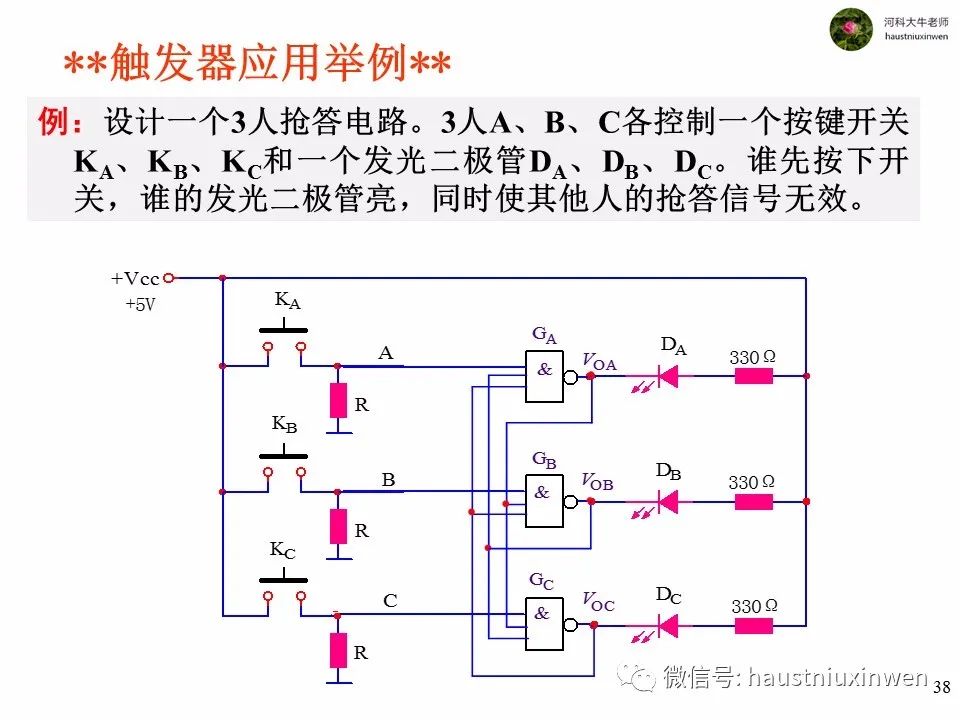

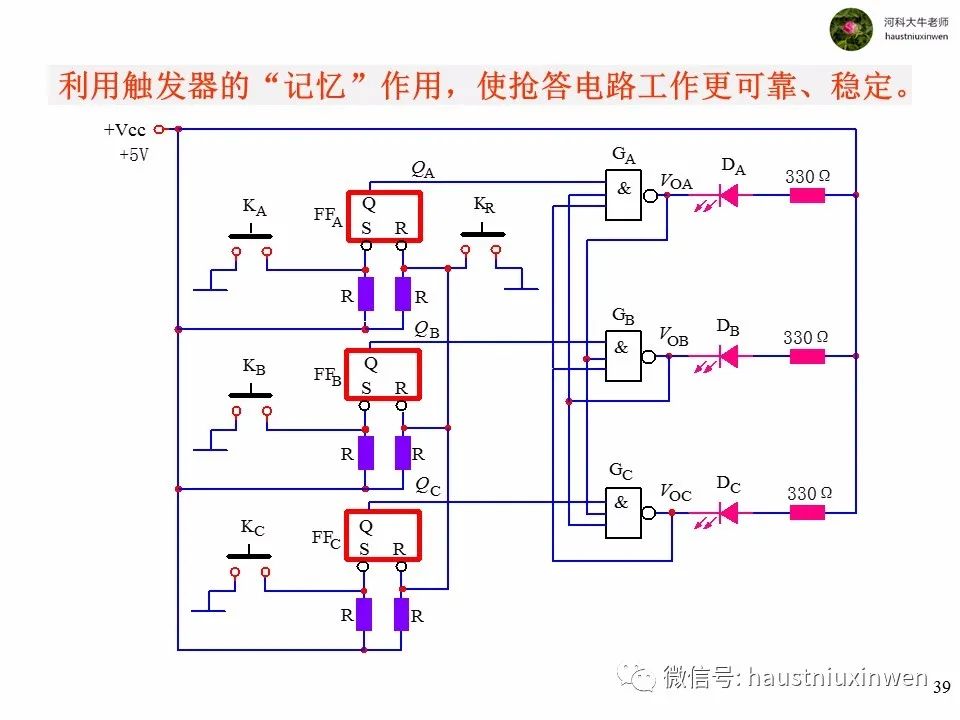

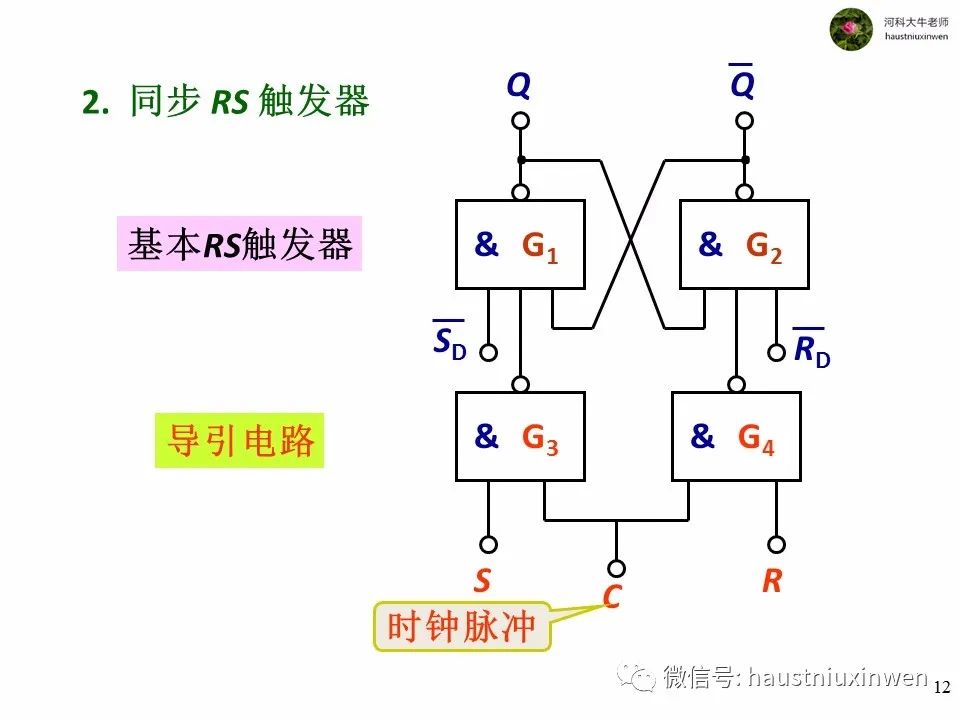

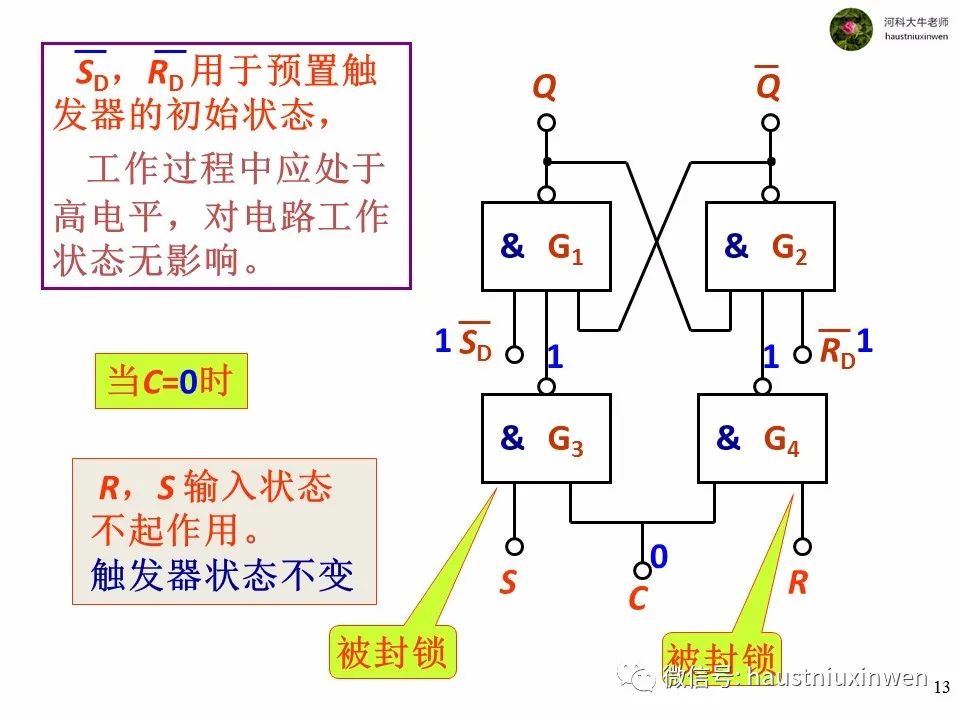

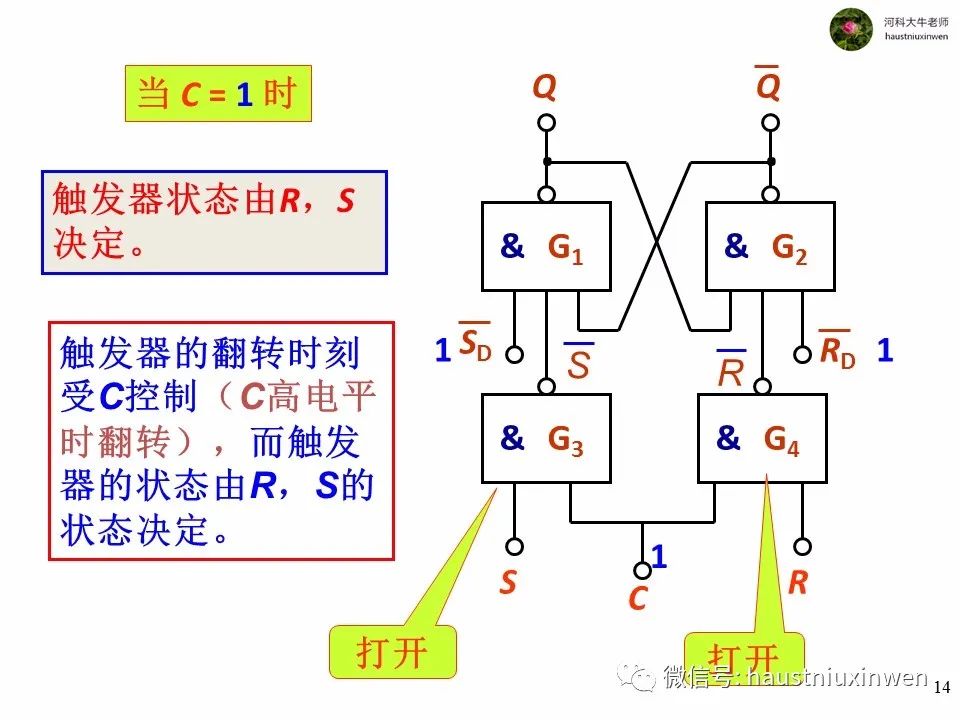

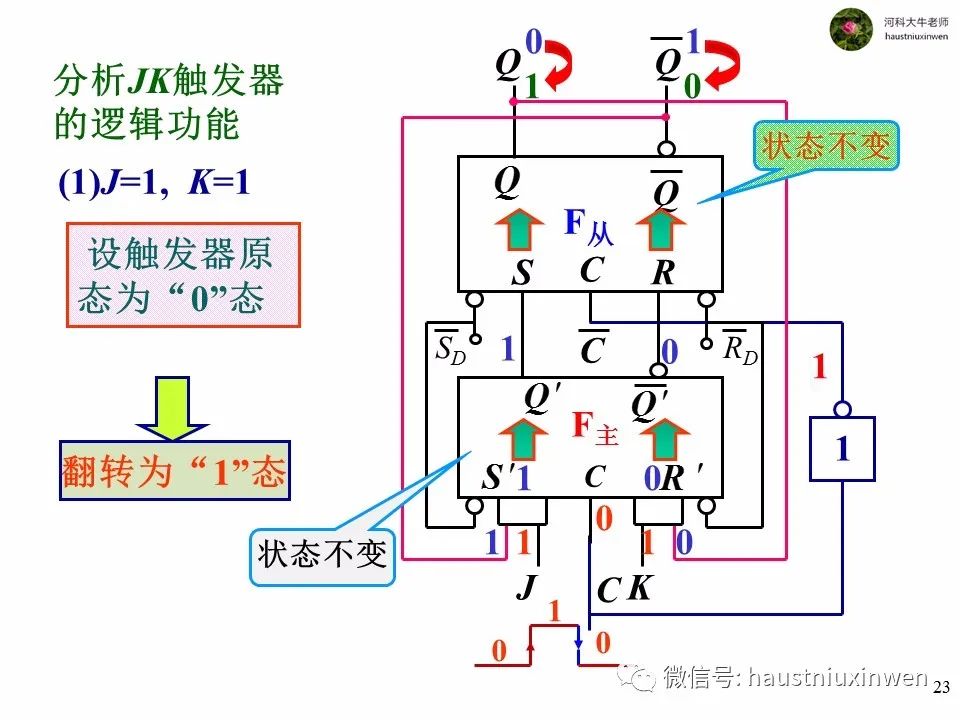

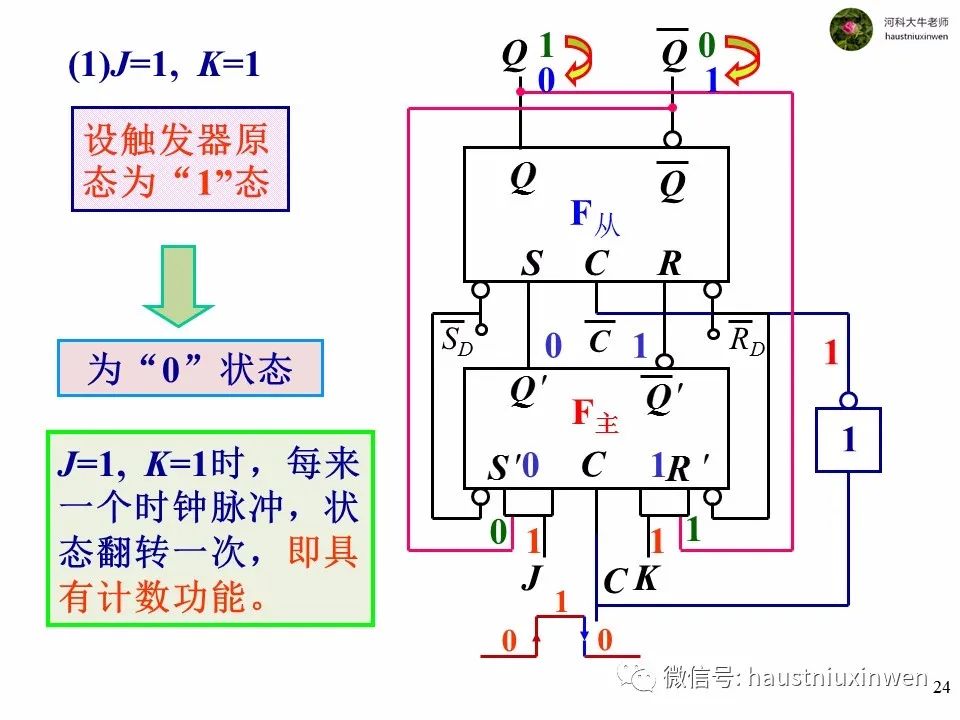

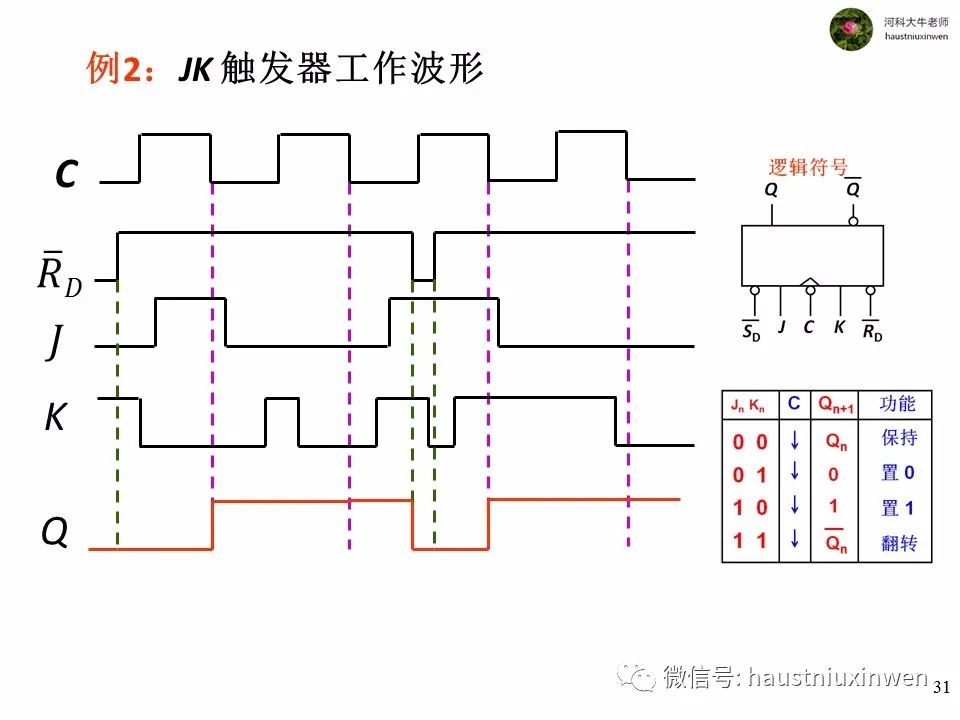

與模擬電路中的反饋不同的是,反饋不是隨時(shí)隨地進(jìn)行的,而是有節(jié)奏的,當(dāng)有效觸發(fā)信號(hào)來臨,才能進(jìn)行控制輸出的作用。觸發(fā)信號(hào)不來,輸入信號(hào)即便有變化,也不能改變輸出。這種動(dòng)作機(jī)制可以保證邏輯電路的多個(gè)輸入信號(hào)動(dòng)作完成后才去實(shí)現(xiàn)邏輯功能,即減少誤動(dòng)作,增加可靠性。

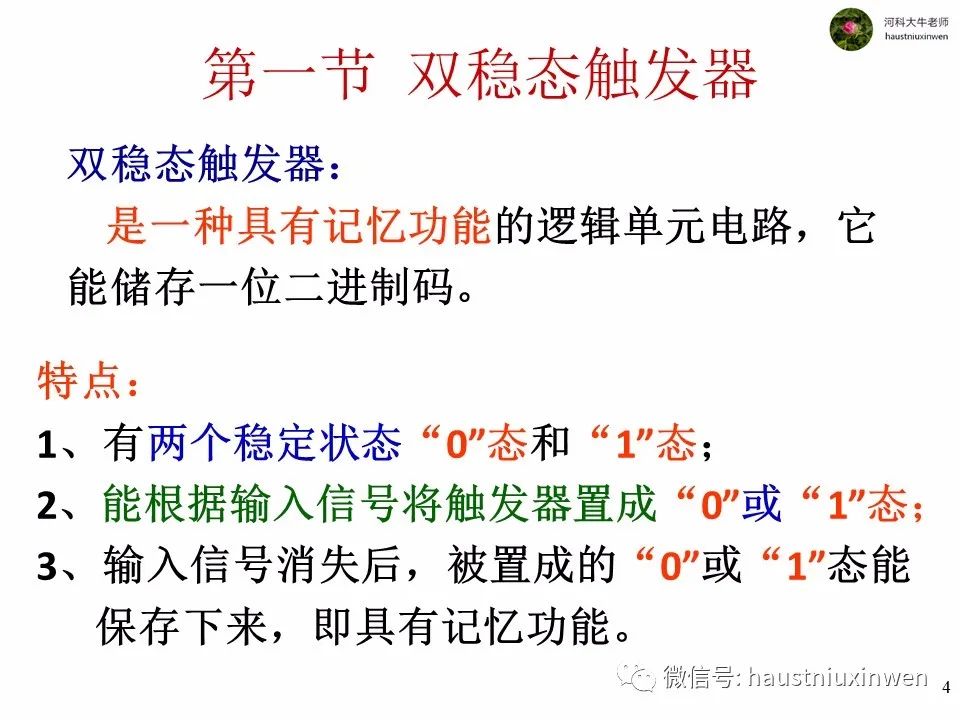

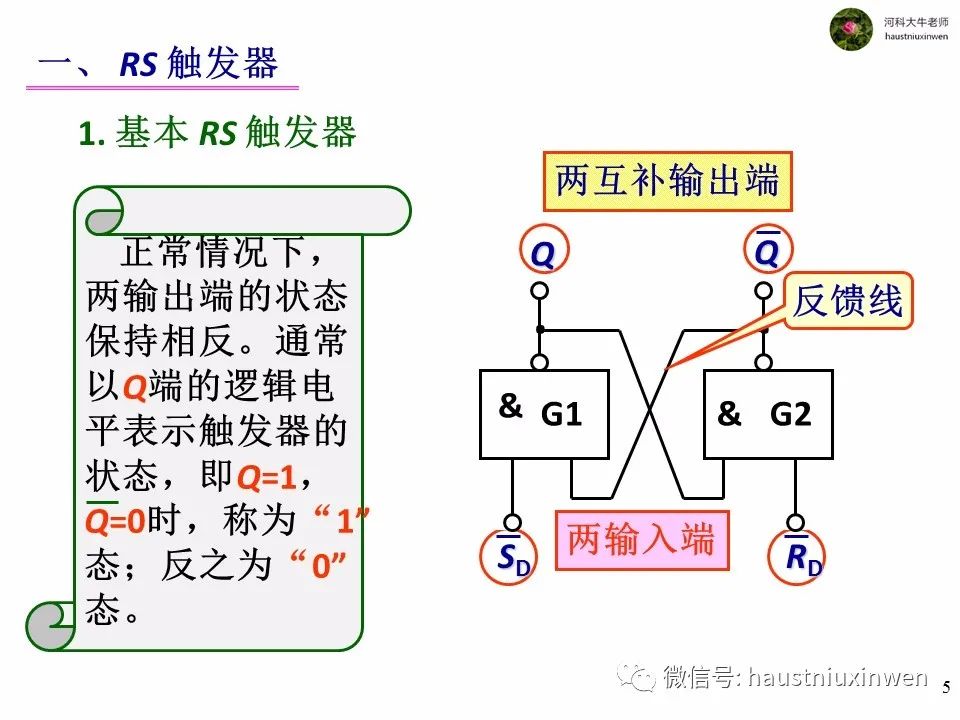

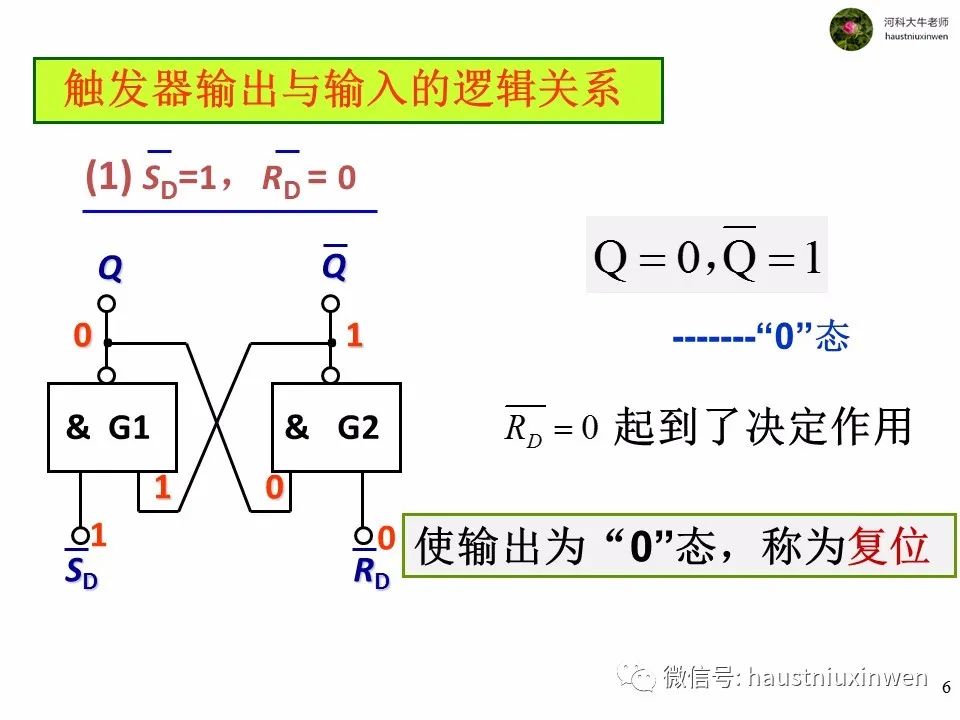

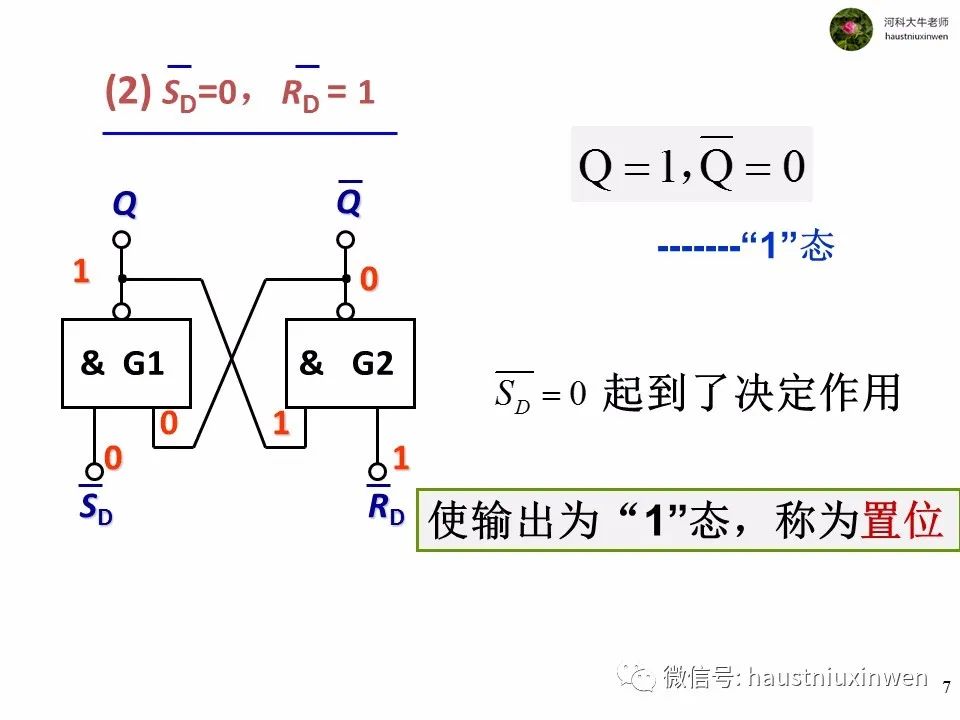

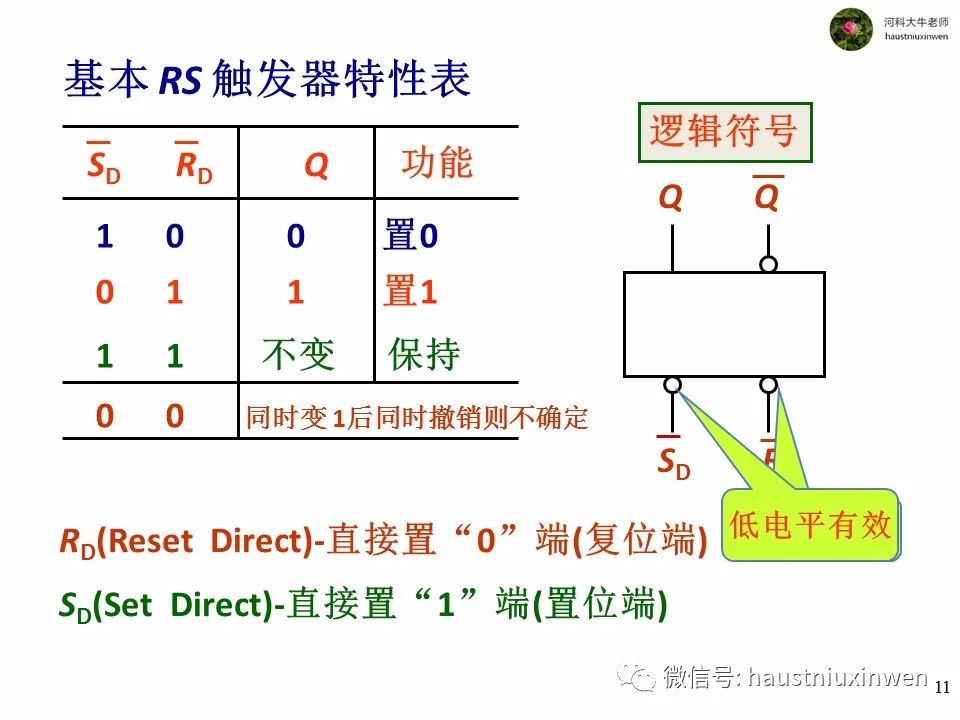

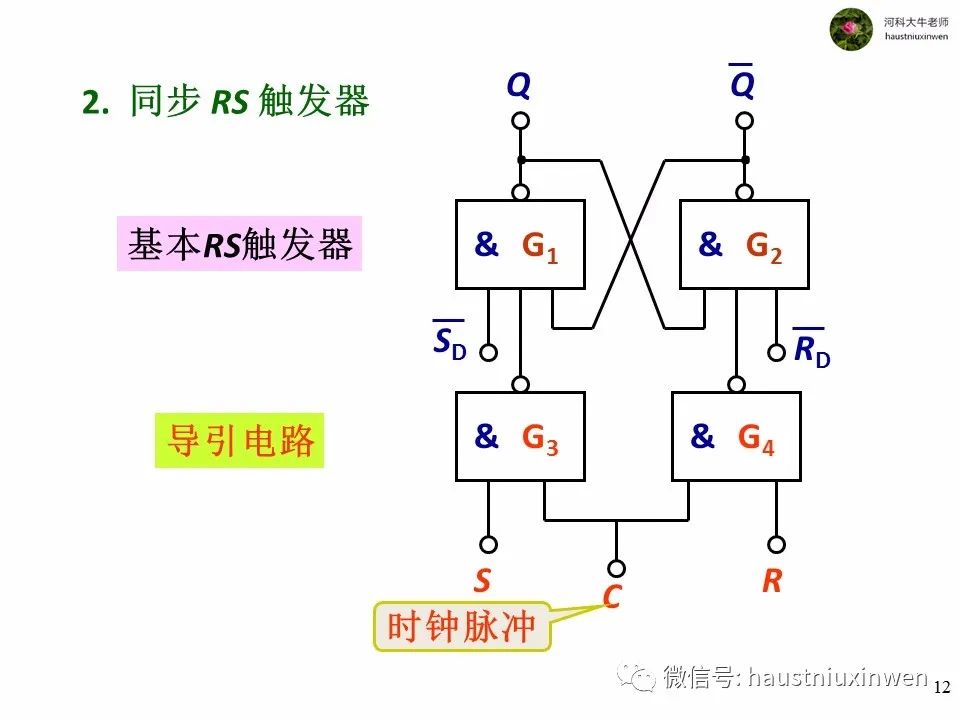

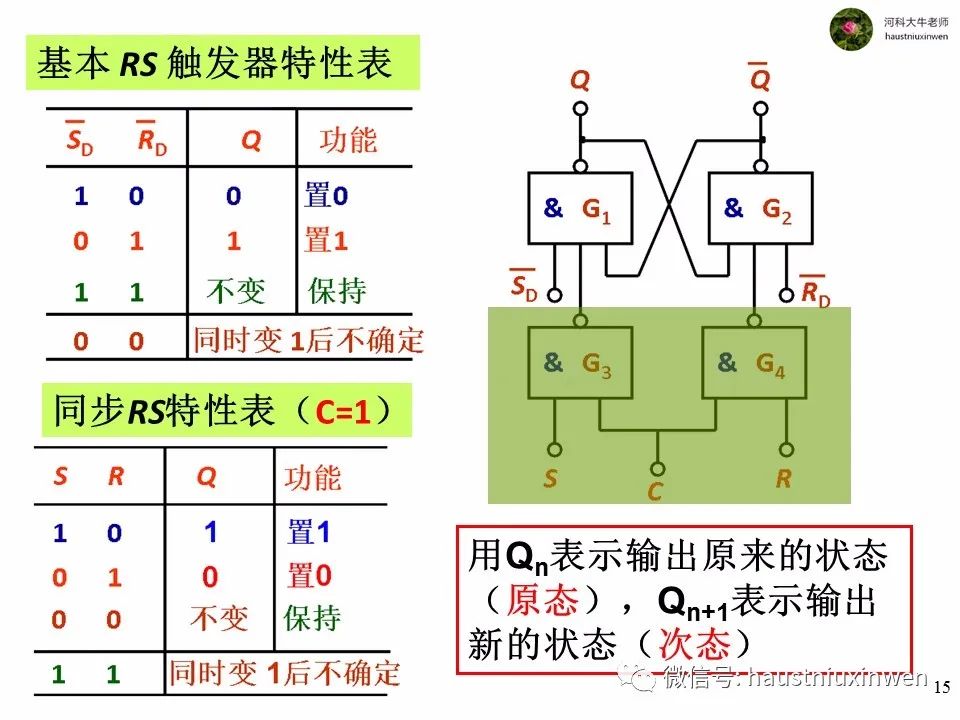

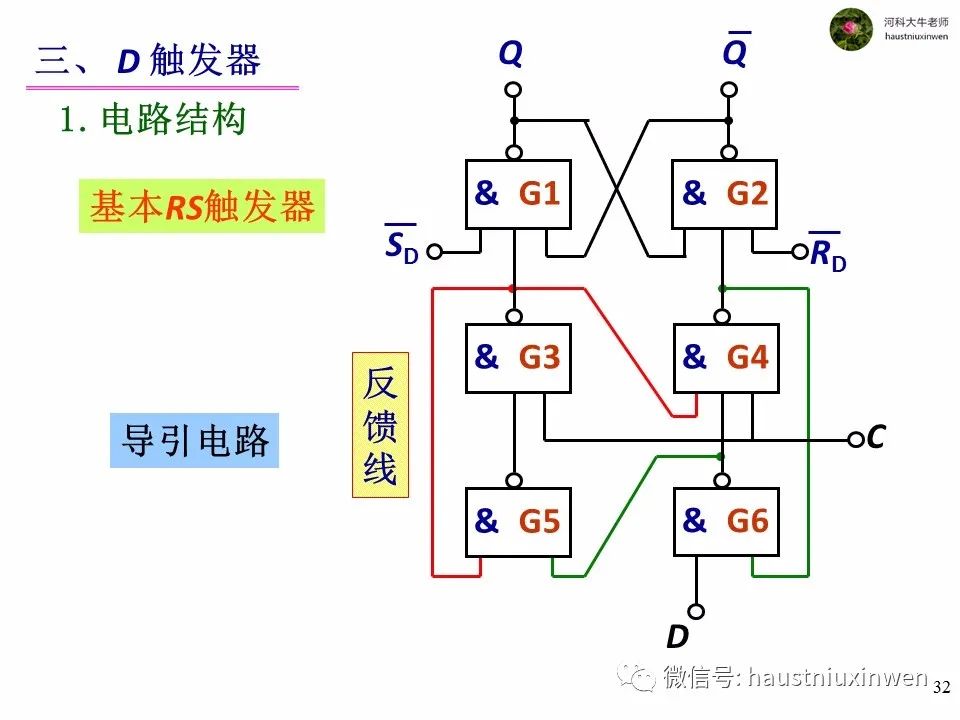

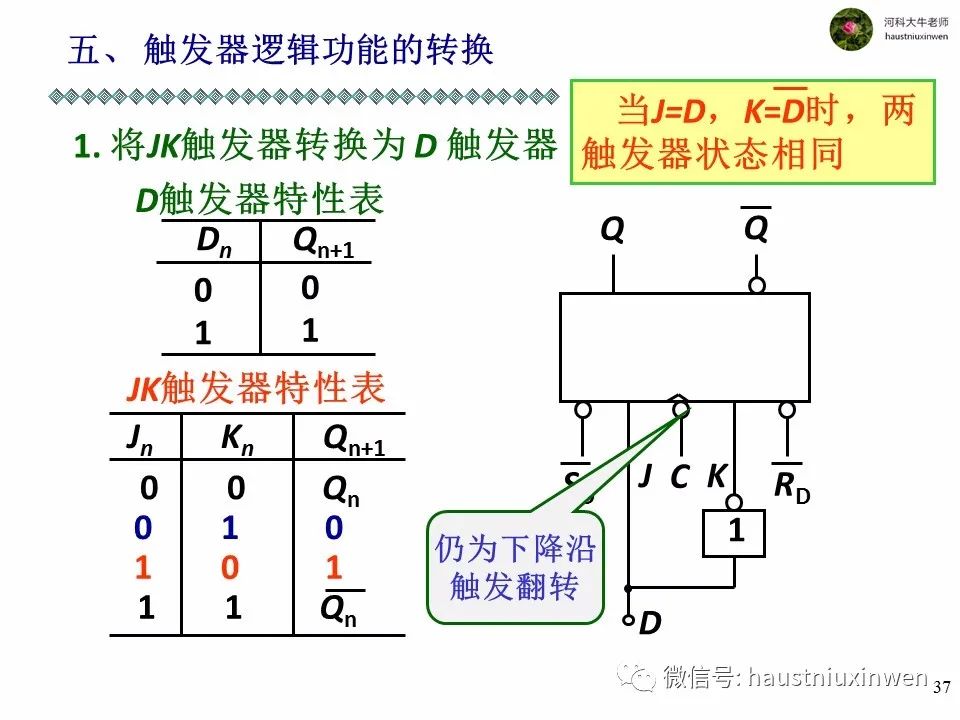

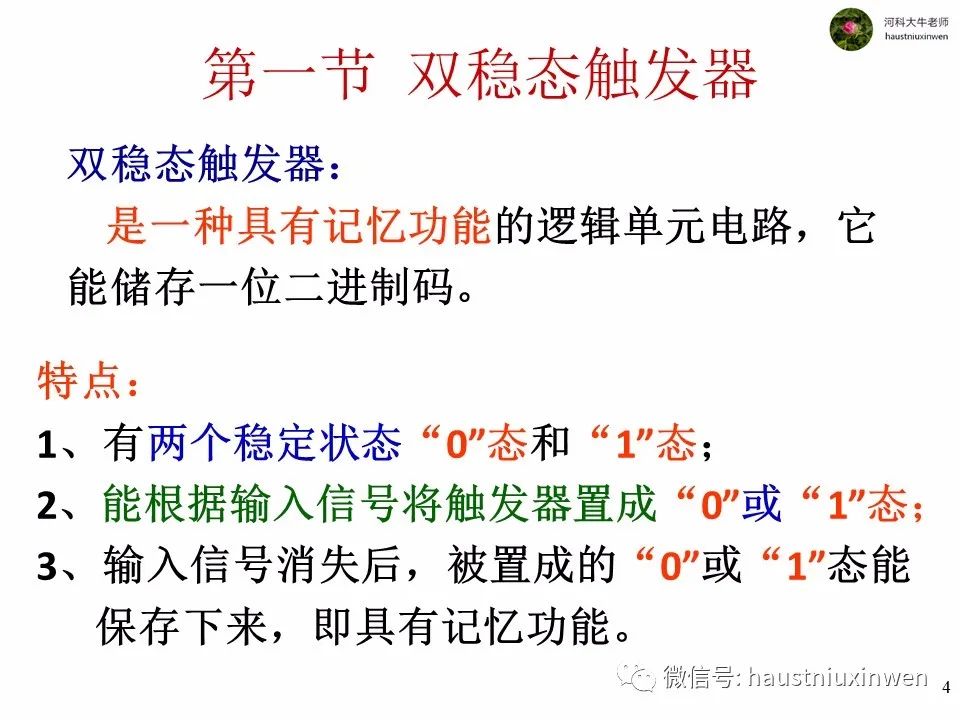

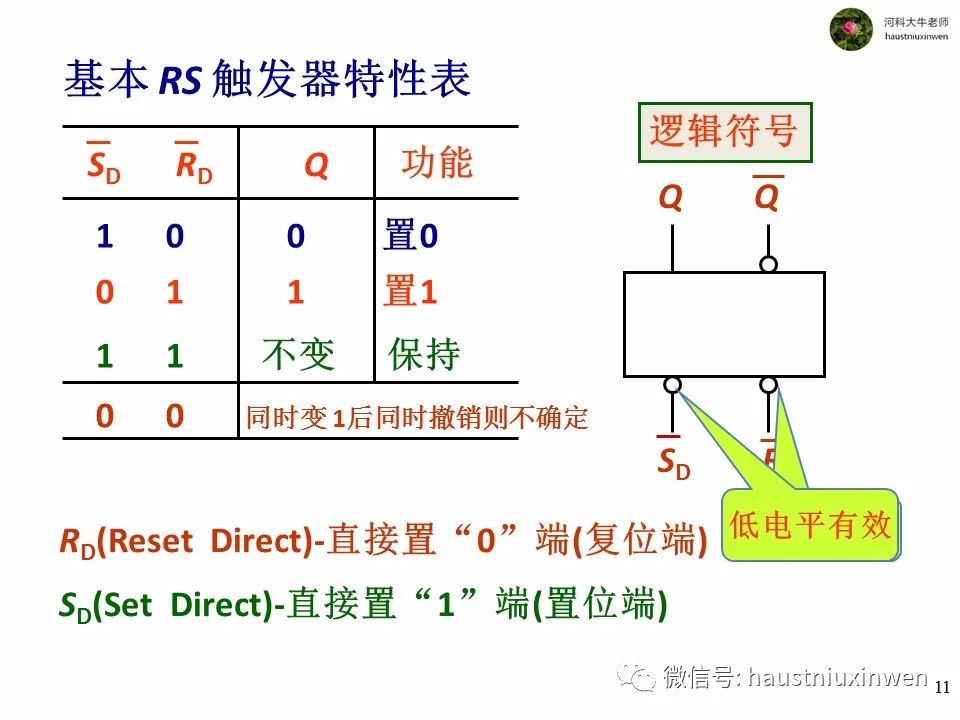

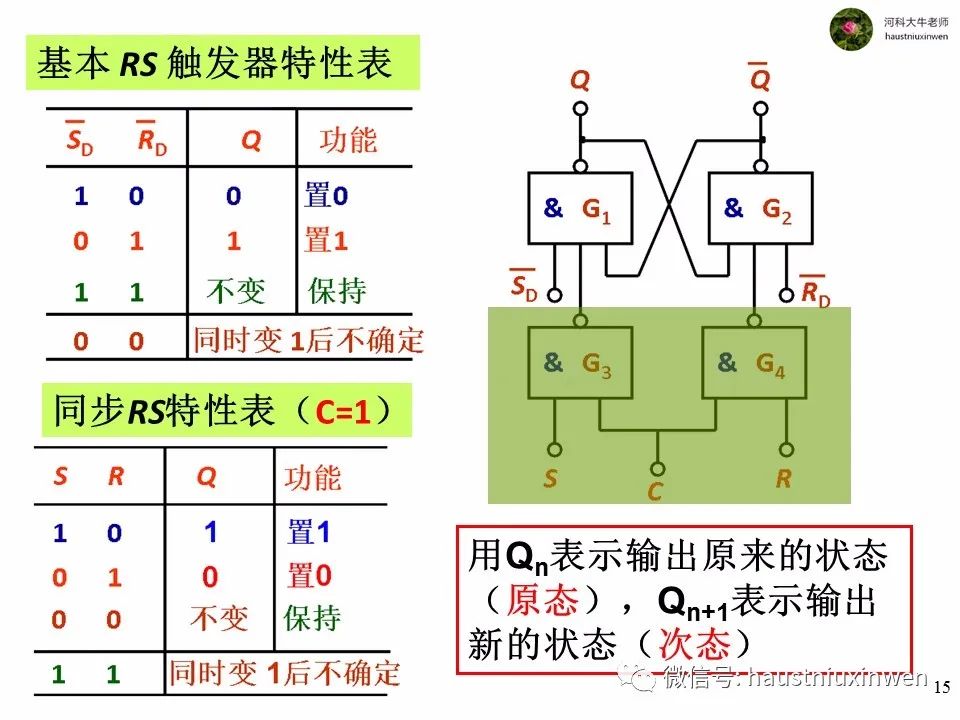

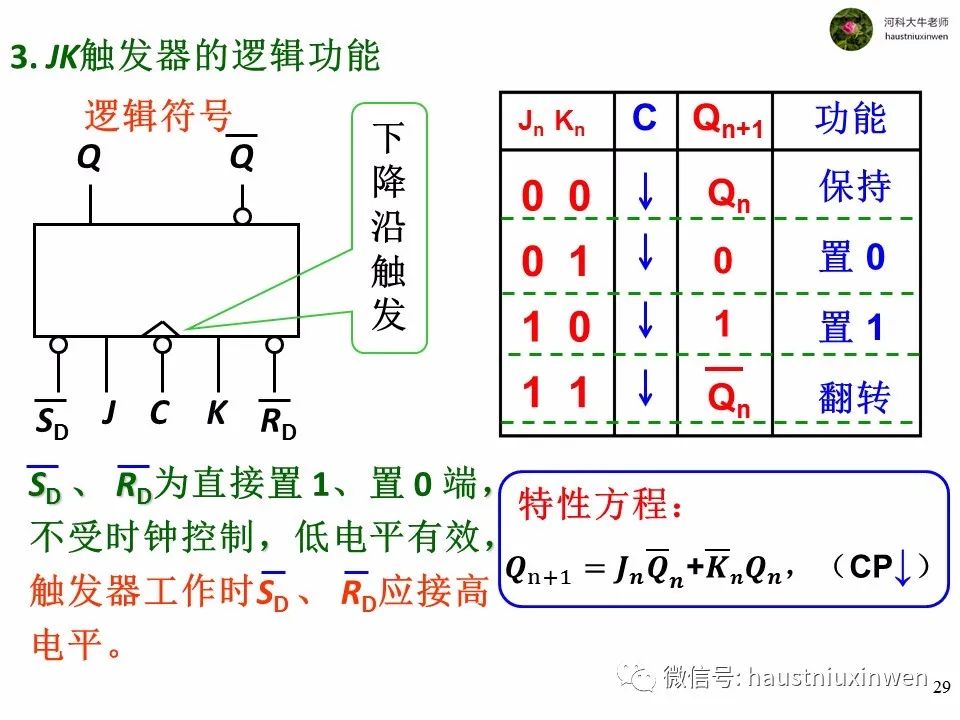

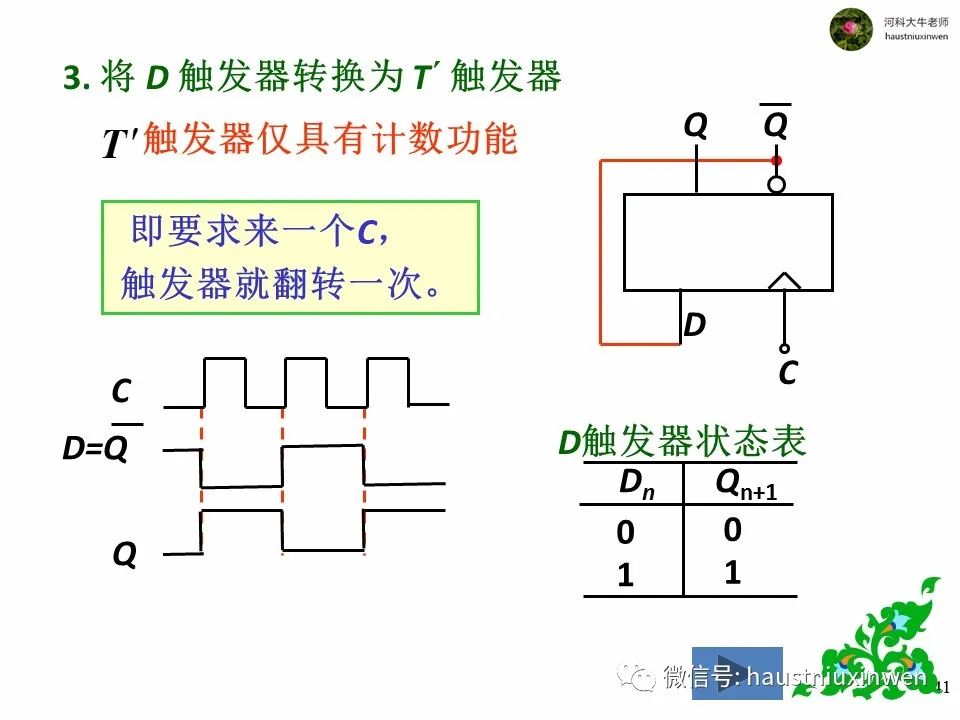

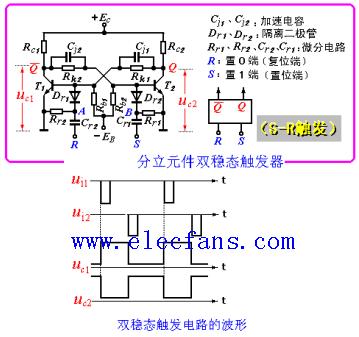

組合邏輯電路的基本單元是門電路,而時(shí)序邏輯電路的基礎(chǔ)單元是雙穩(wěn)態(tài)觸發(fā)器。

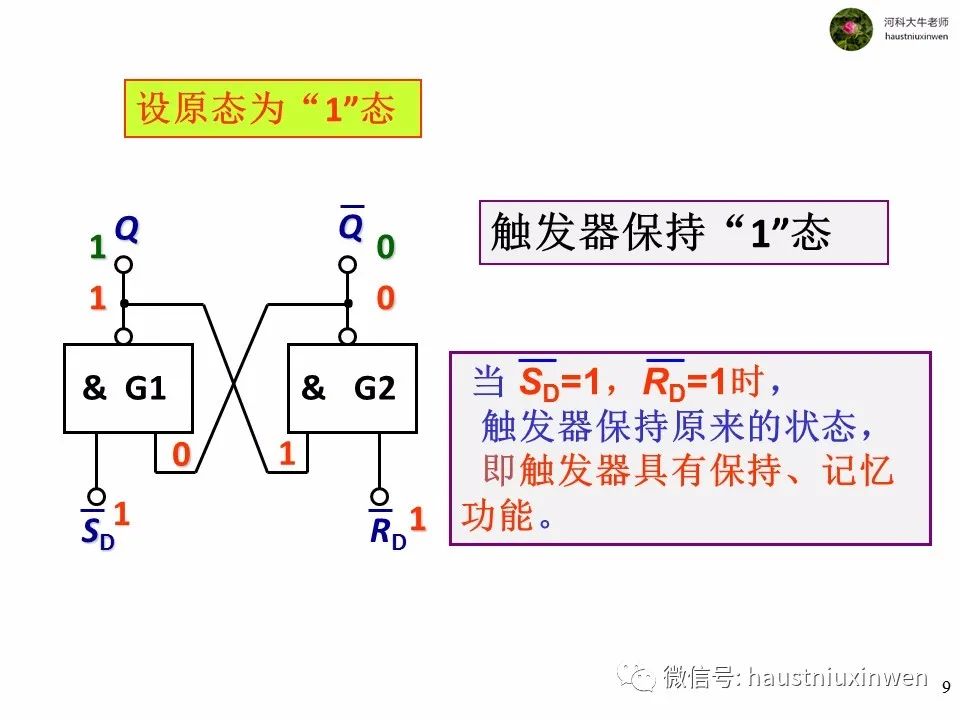

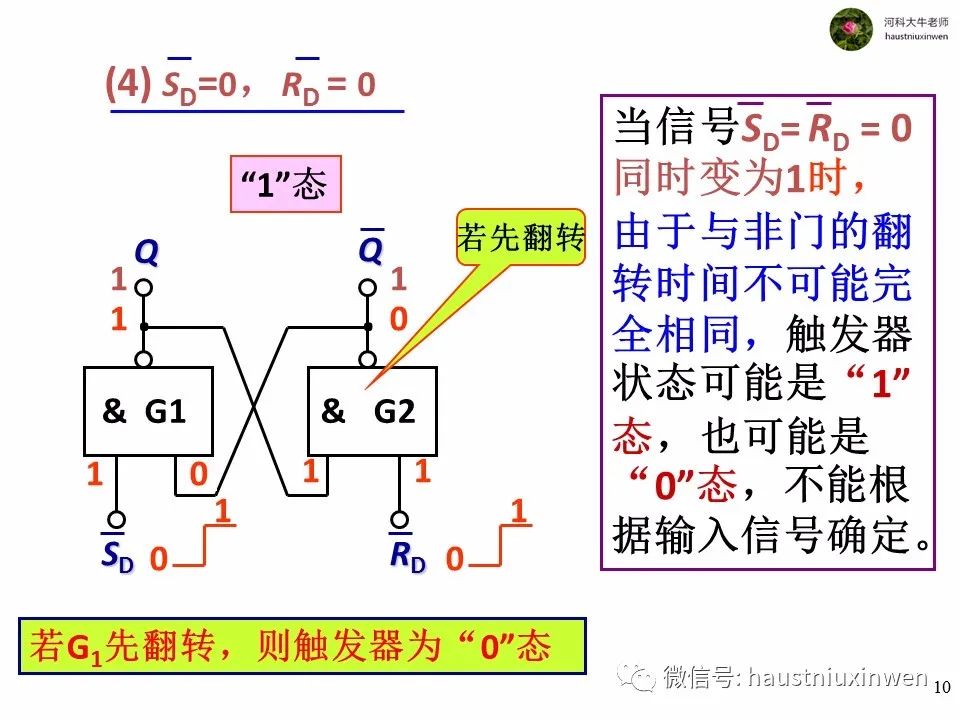

穩(wěn)態(tài)是指在沒有有效觸發(fā)信號(hào)時(shí),輸出端的狀態(tài)始終保持不變。

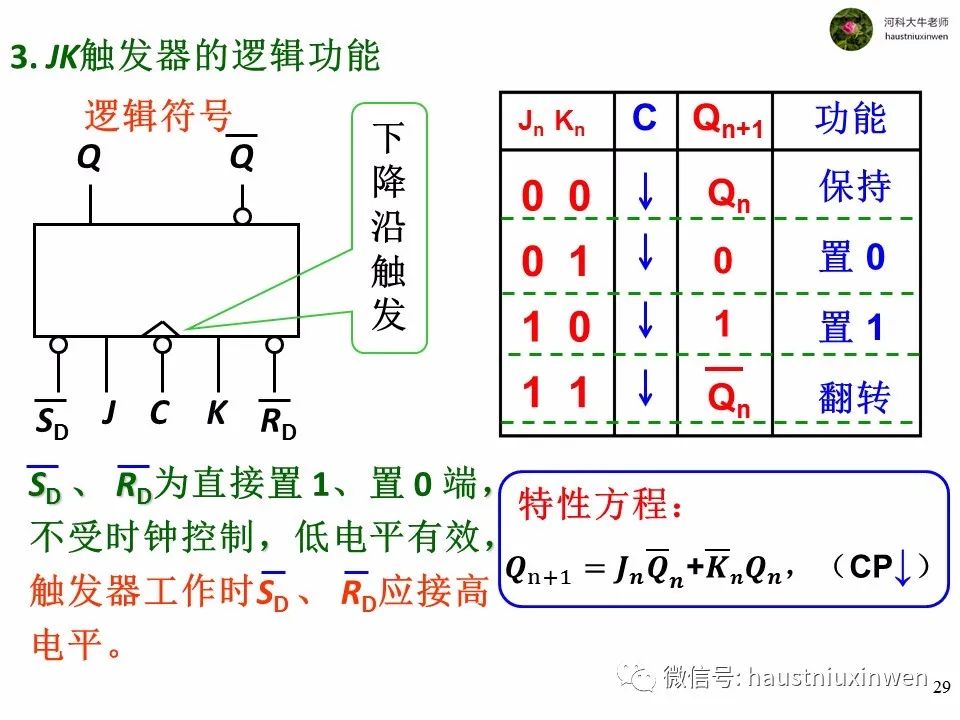

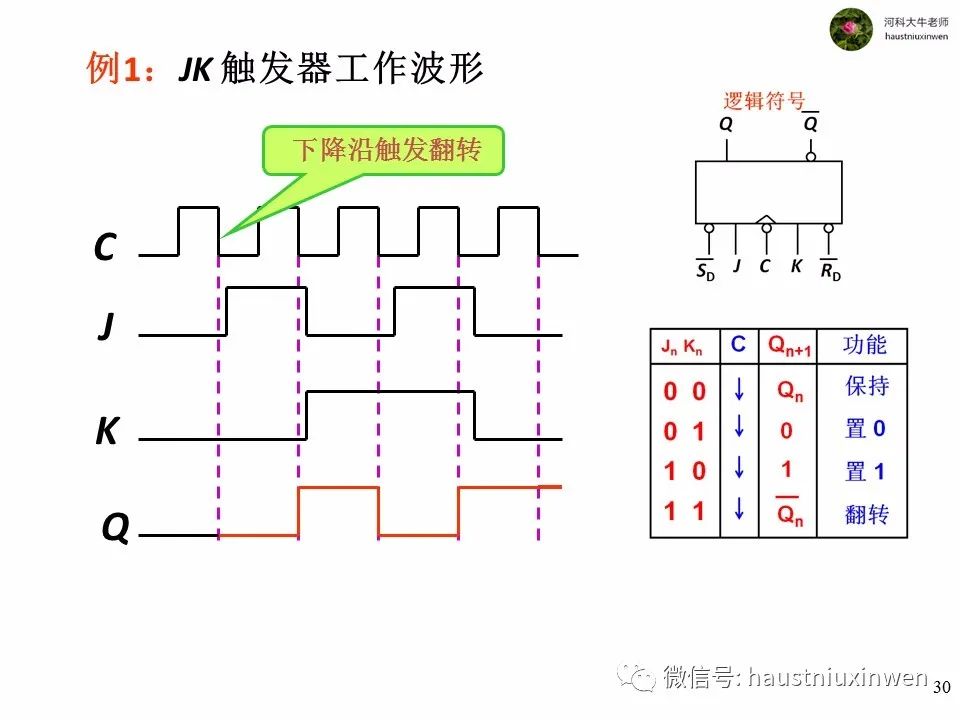

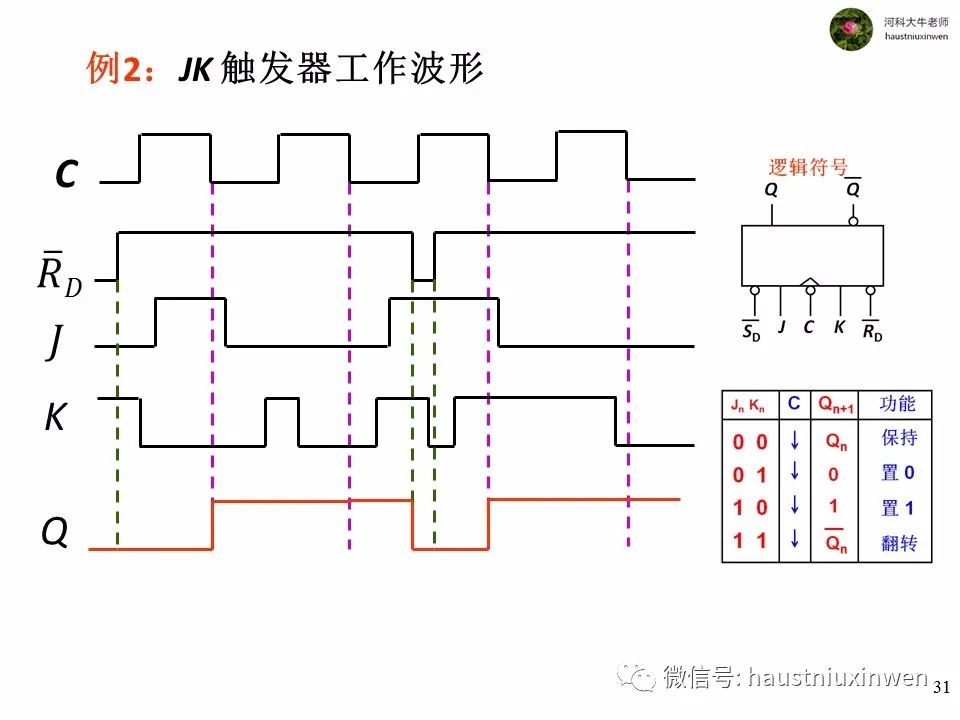

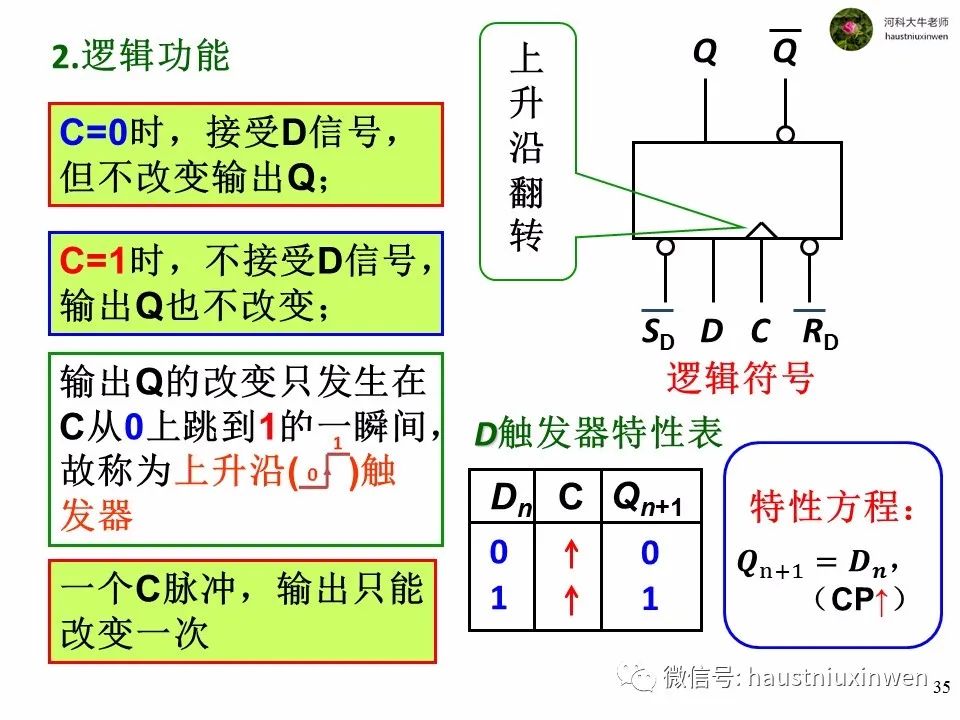

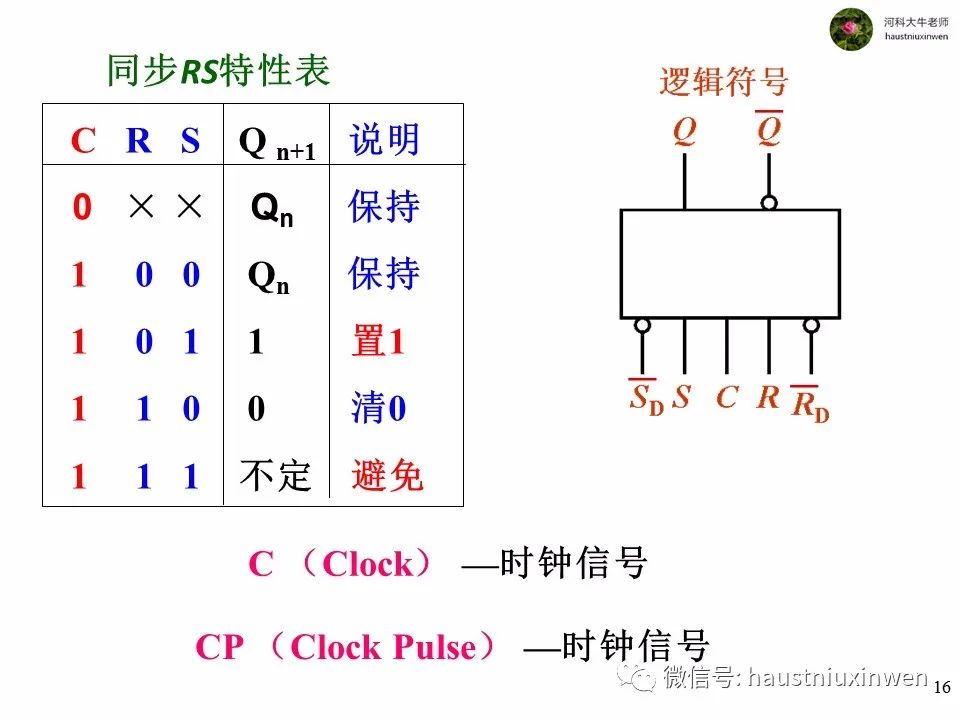

而觸發(fā)信號(hào)有電平觸發(fā)和邊沿觸發(fā)兩種。

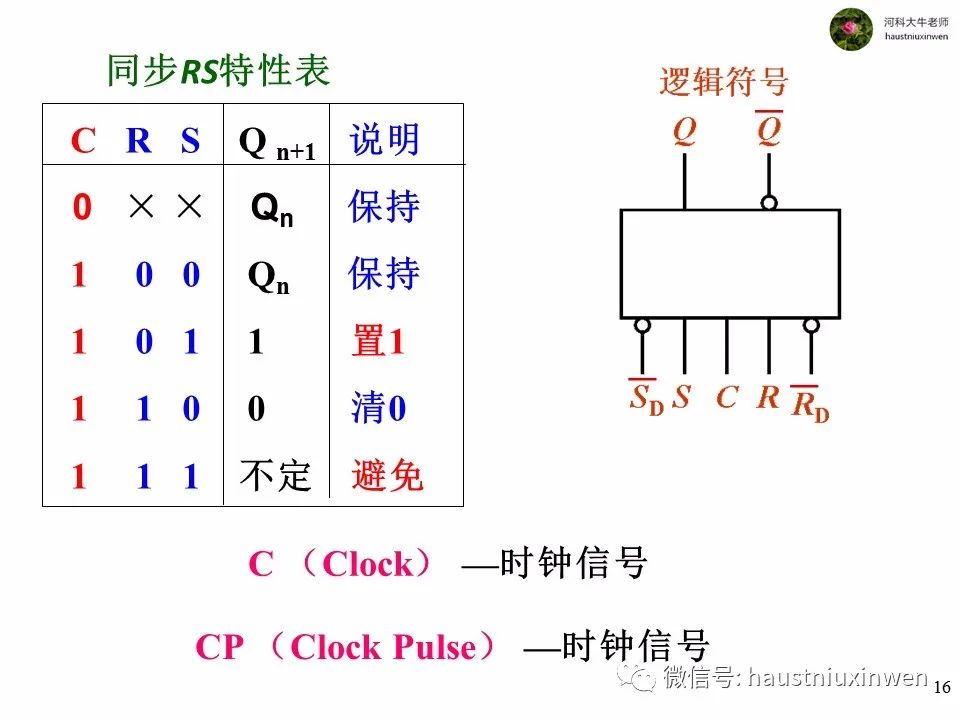

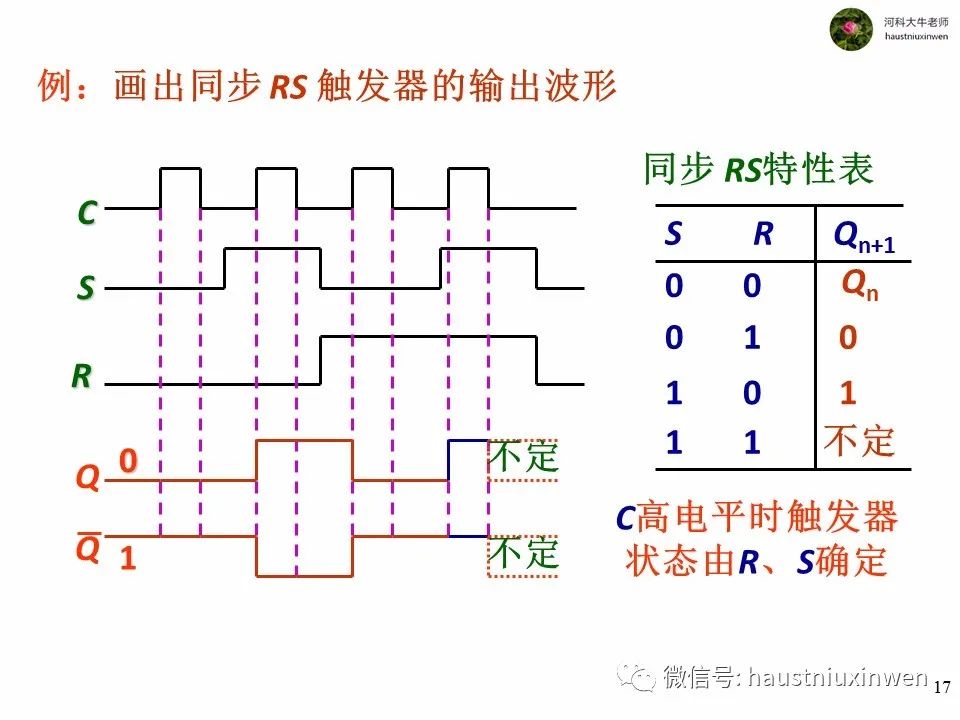

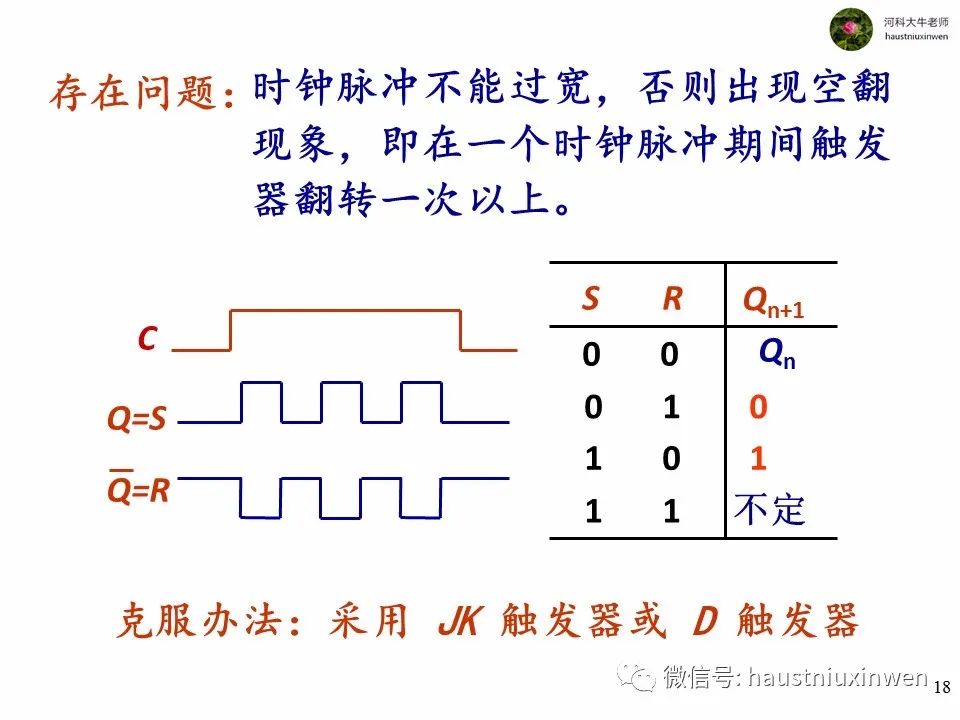

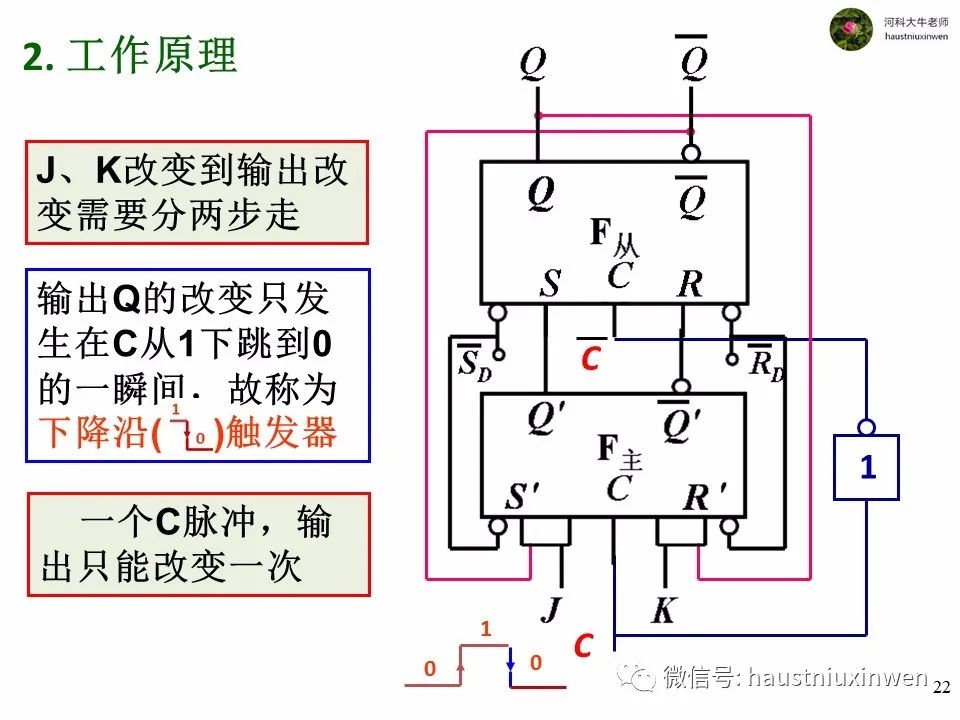

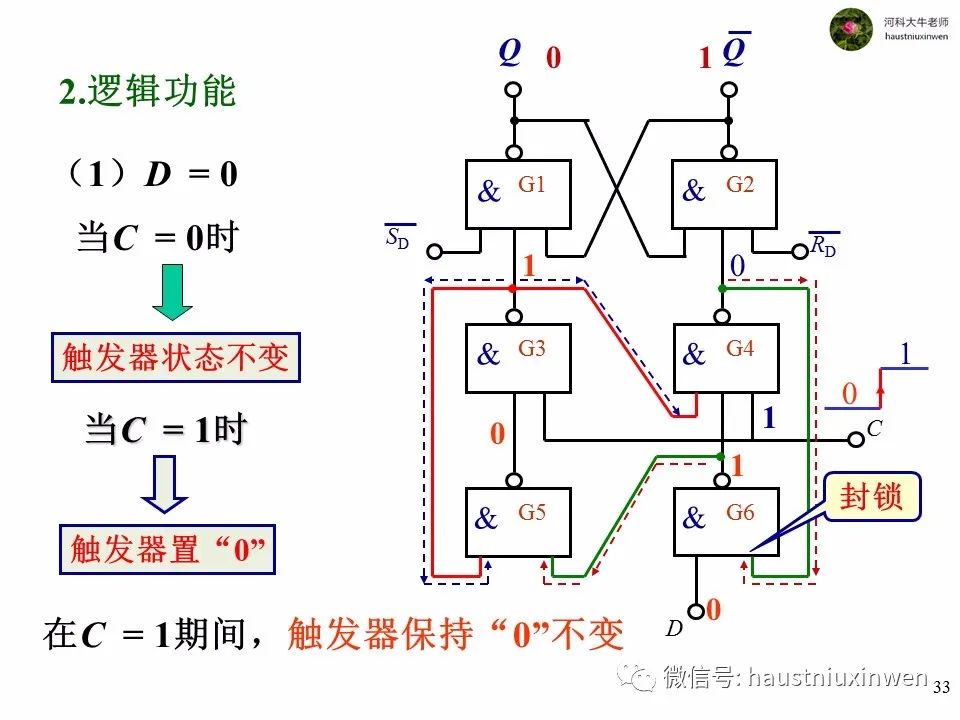

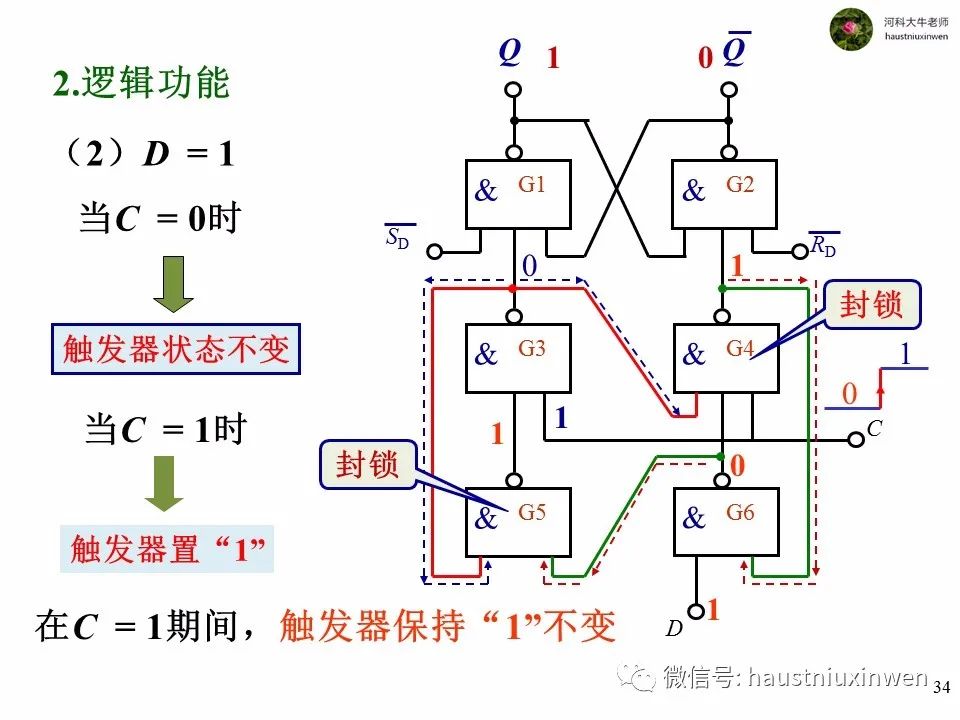

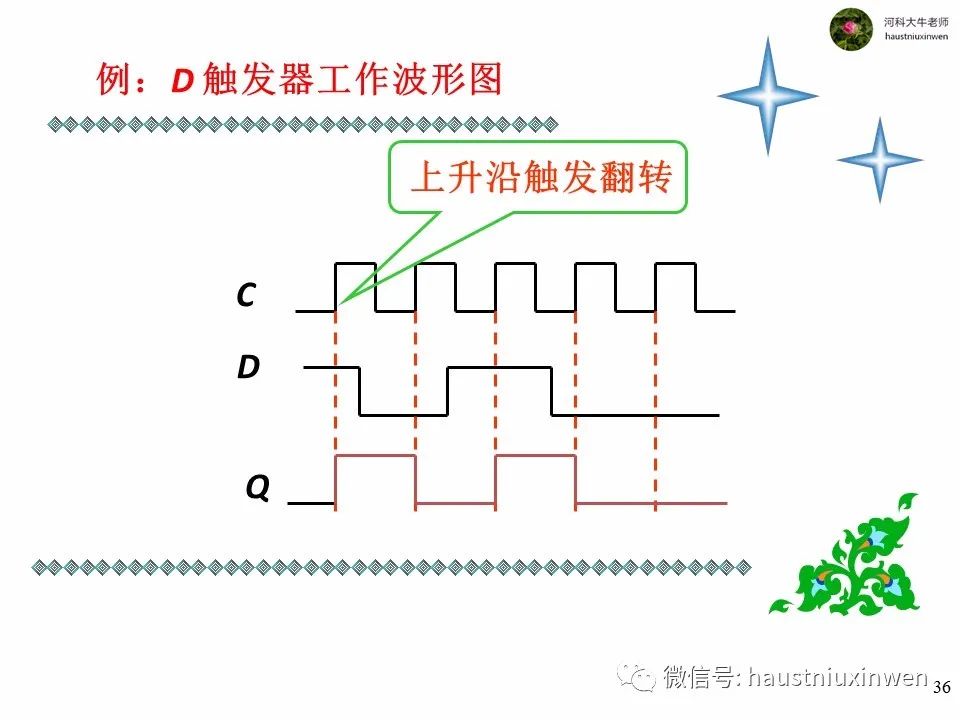

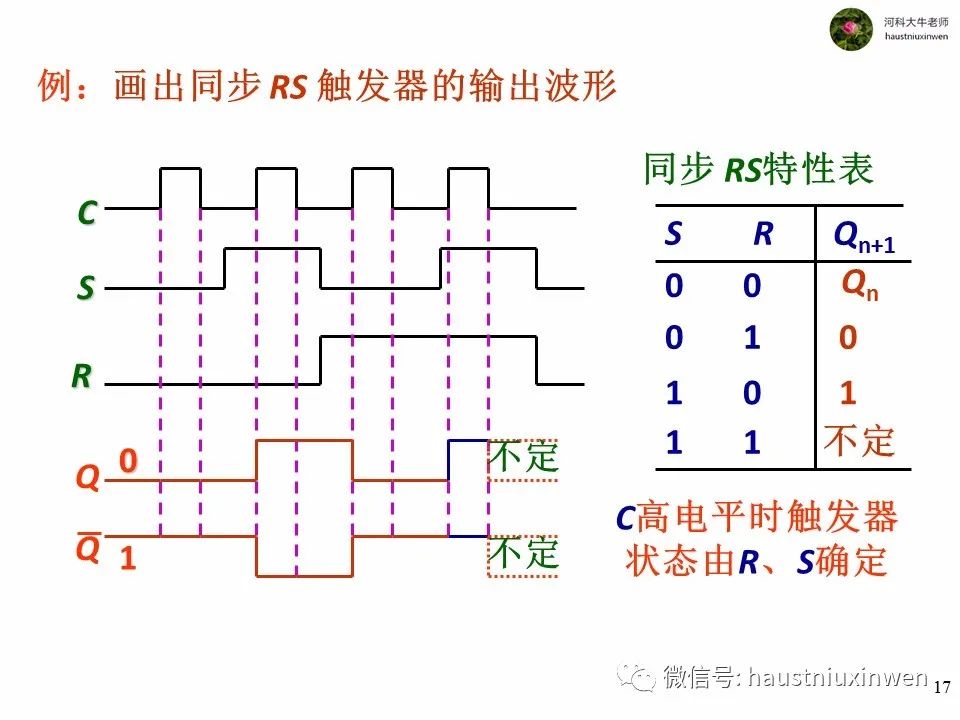

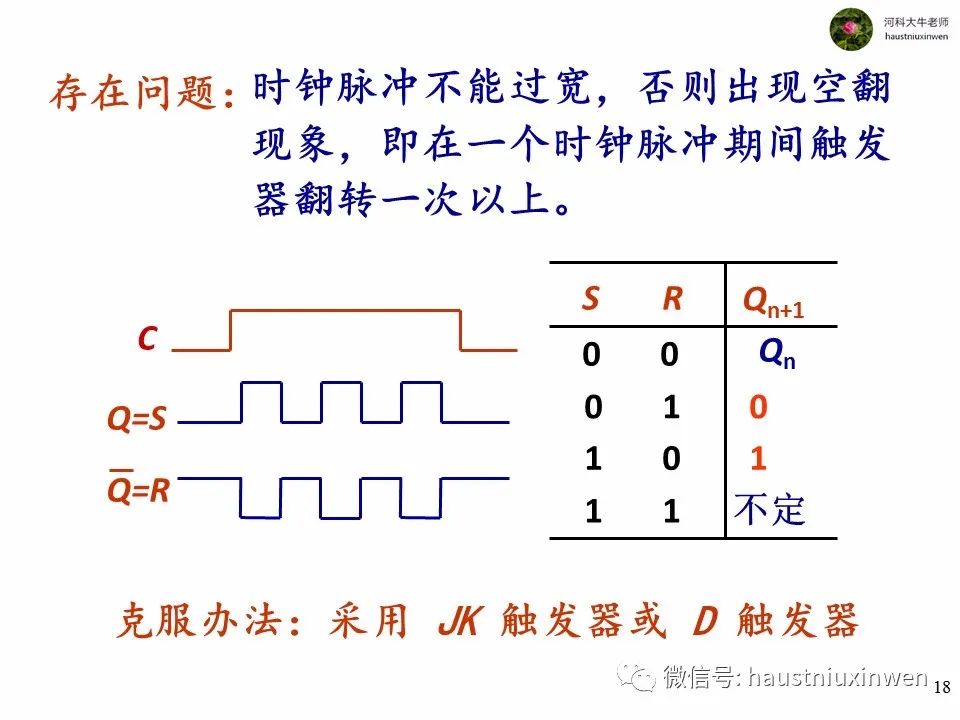

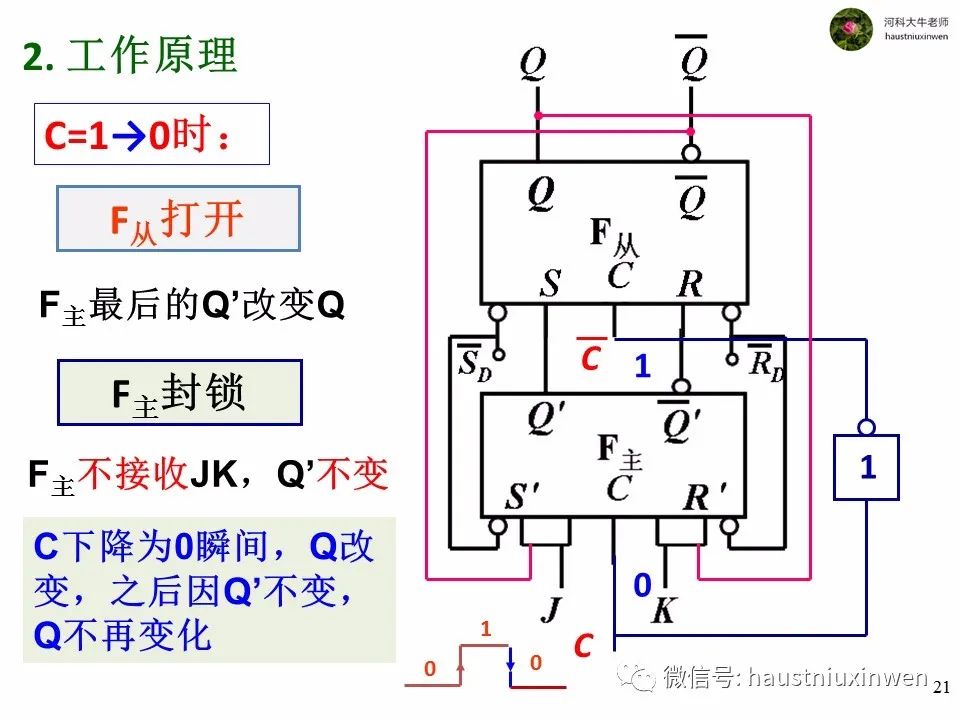

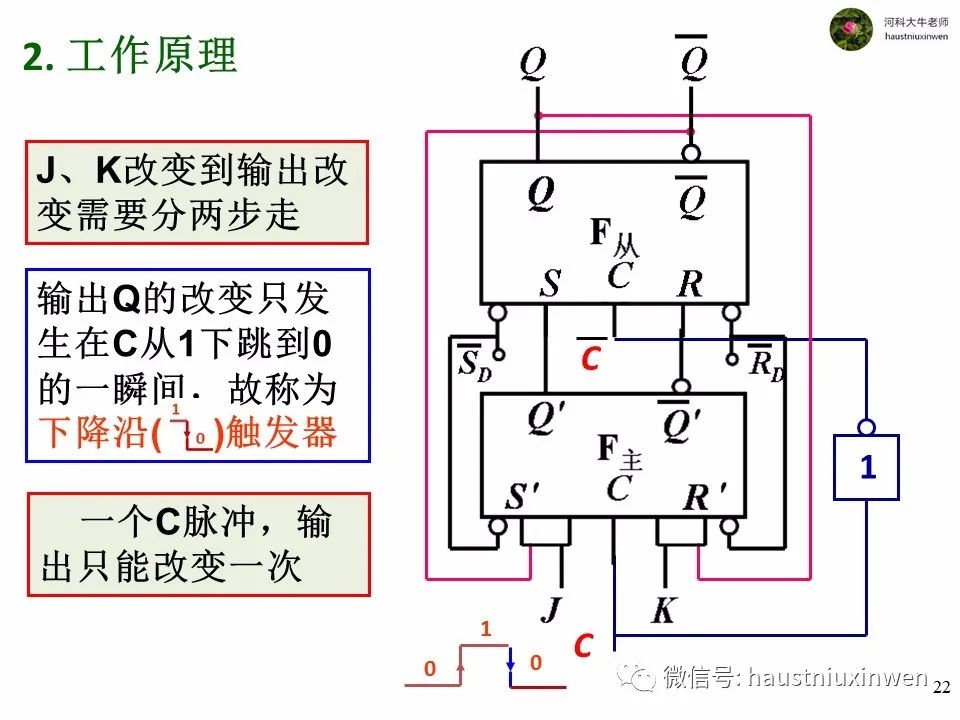

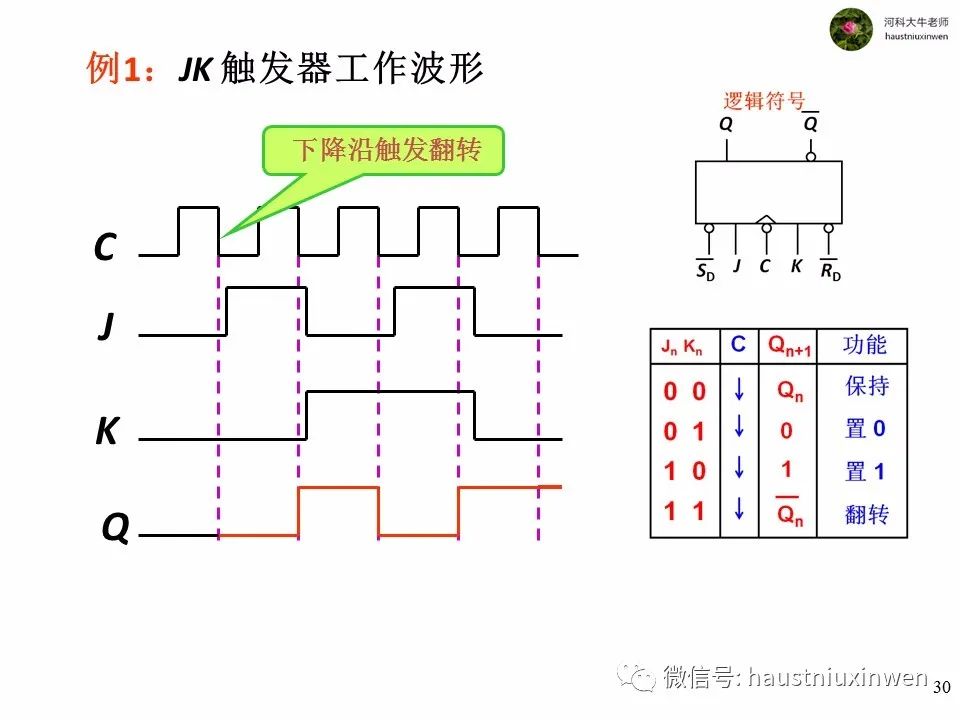

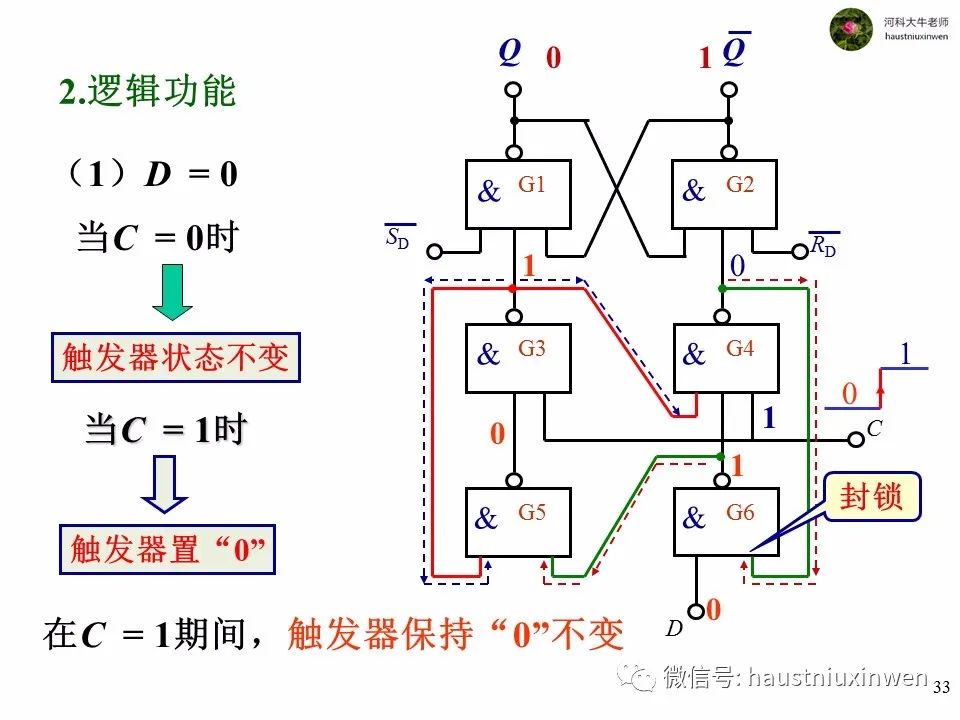

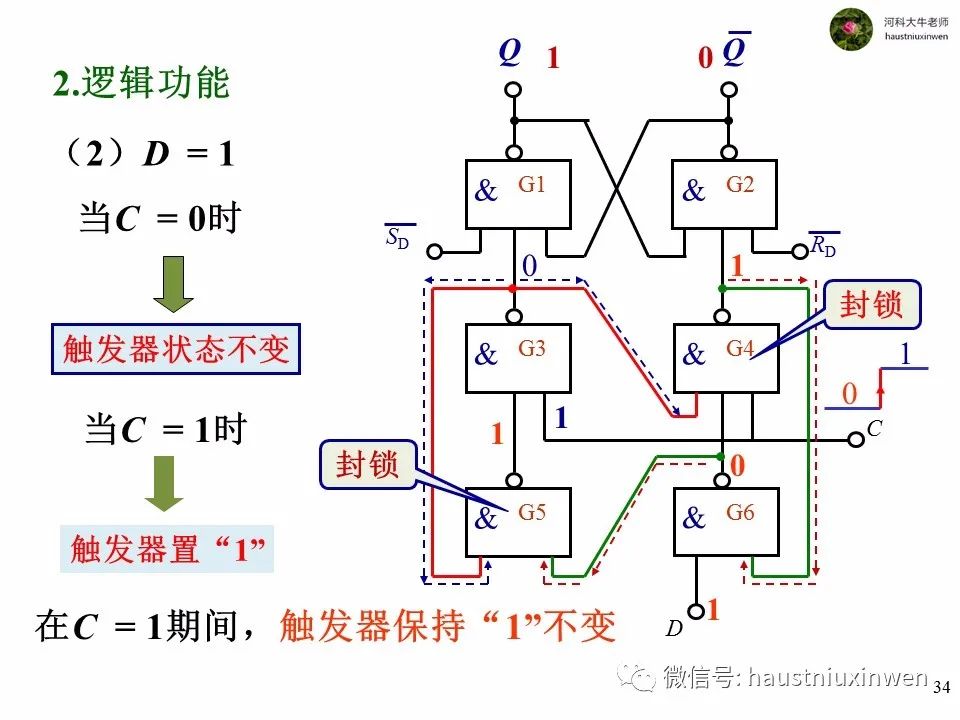

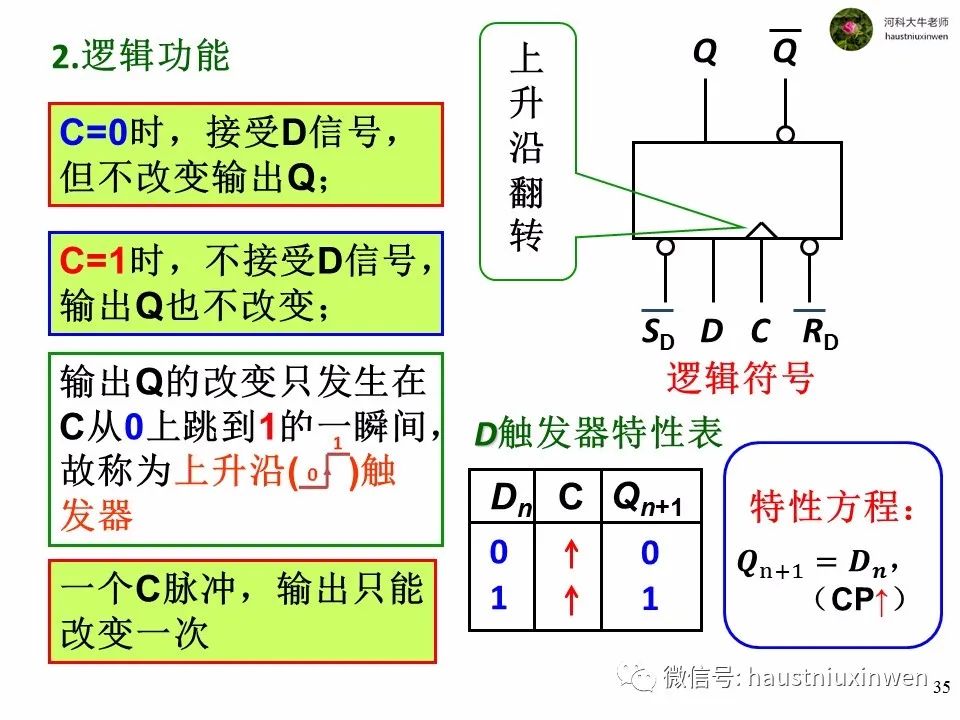

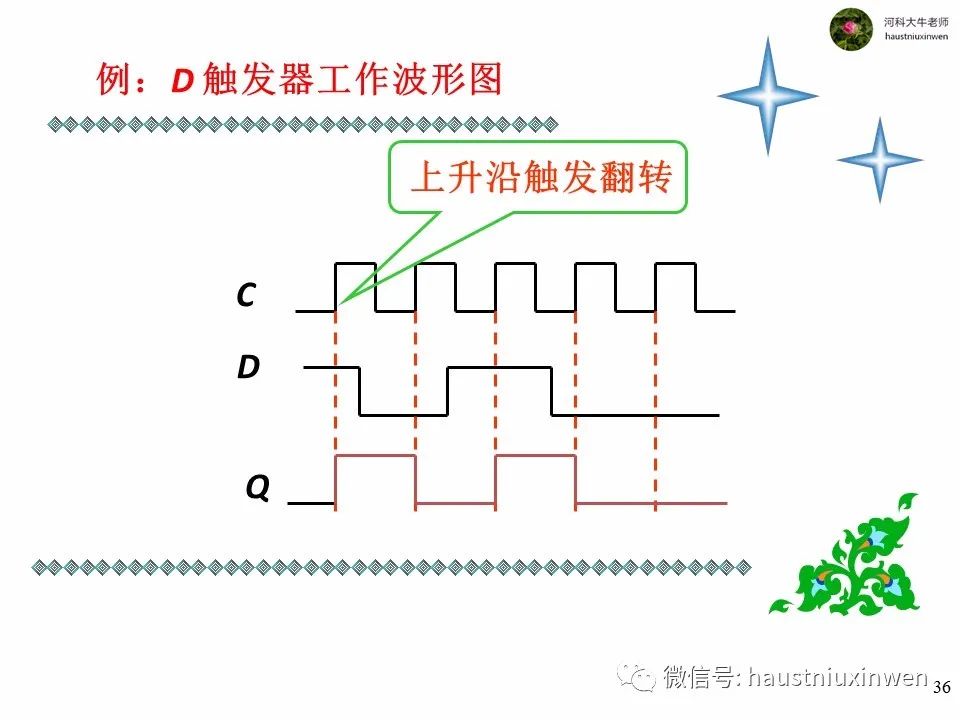

電平觸發(fā)是指當(dāng)時(shí)鐘信號(hào)為高電平時(shí),允許輸出根據(jù)輸入和原狀態(tài)改變。邊沿觸發(fā)是指當(dāng)時(shí)鐘信號(hào)由0變1或者由1變0時(shí),輸出才能根據(jù)輸入和原狀態(tài)改變。

電平觸發(fā)在需要多個(gè)信號(hào)都滿足時(shí)才執(zhí)行功能的情況下經(jīng)常使用,以避免因多路信號(hào)反應(yīng)時(shí)間不一致造成的誤操作。

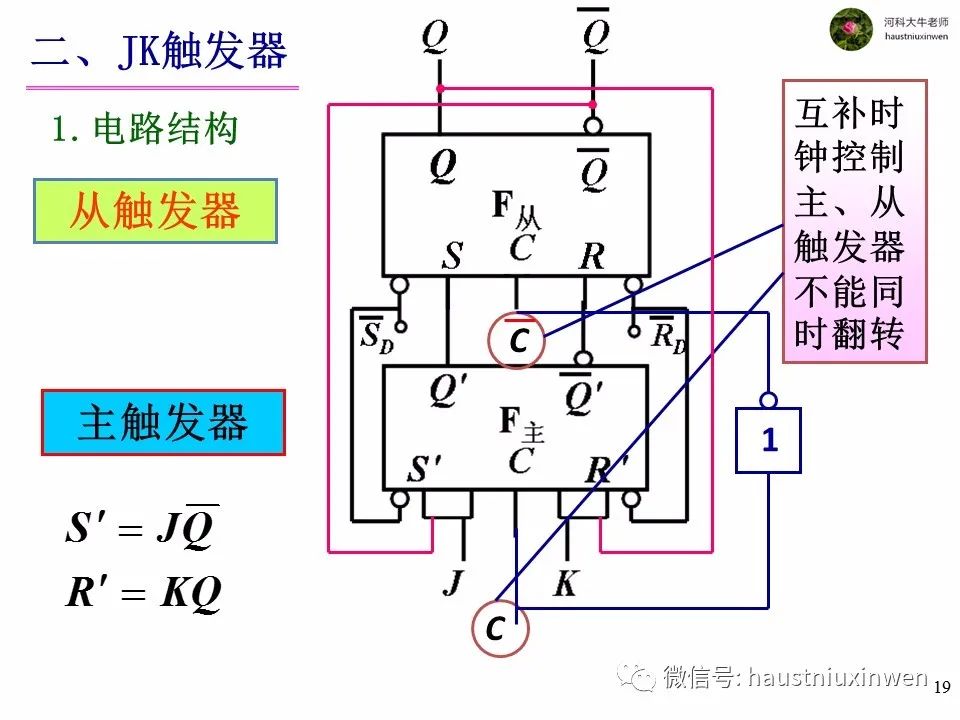

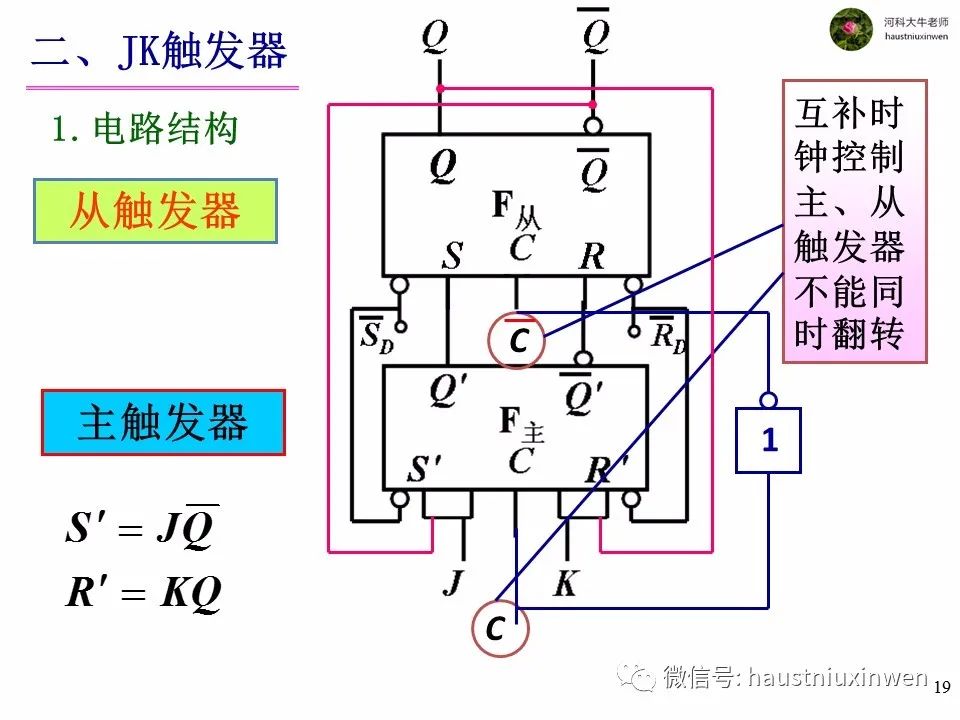

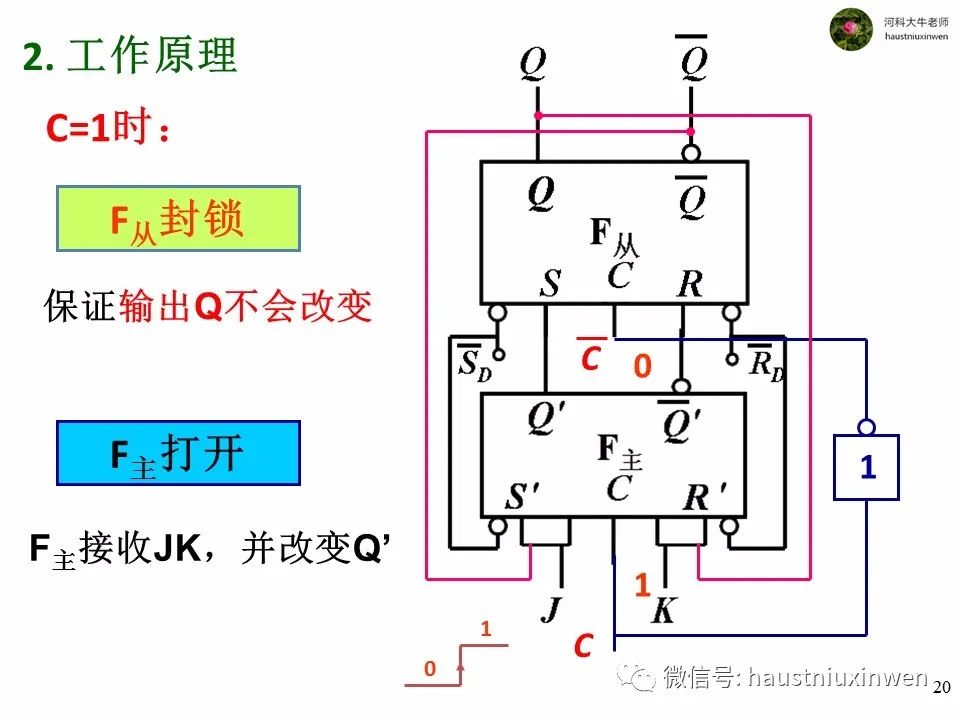

邊沿觸發(fā)可以實(shí)現(xiàn)一個(gè)觸發(fā)脈沖信號(hào)觸發(fā)器只動(dòng)作一次的功能,避免空翻失控。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

模擬電路

-

門電路

-

觸發(fā)器

-

時(shí)序邏輯電路

-

脈沖信號(hào)

相關(guān)推薦

數(shù)字電路--觸發(fā)器雙穩(wěn)態(tài)觸發(fā)器

發(fā)表于 02-05 14:16

什么是雙穩(wěn)態(tài)觸發(fā)器?

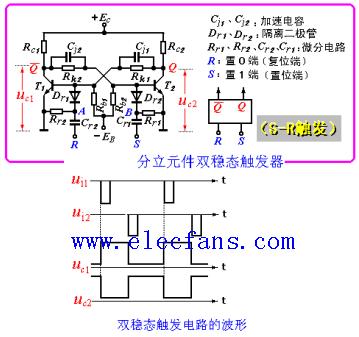

雙穩(wěn)態(tài)觸發(fā)電路實(shí)際上也是RS觸發(fā)器,其ui1端相當(dāng)于R端,ui2端相當(dāng)于S端。因此,用門電路組成的

發(fā)表于 05-26 13:31

?1w次閱讀

數(shù)字電路--觸發(fā)器雙穩(wěn)態(tài)觸發(fā)器

發(fā)表于 12-20 17:32

?0次下載

本文主要介紹了雙穩(wěn)態(tài)觸發(fā)器的工作原理詳解。雙穩(wěn)態(tài)觸發(fā)器是脈沖和數(shù)字電路中常用的基本觸發(fā)器之一。雙穩(wěn)態(tài)

發(fā)表于 04-04 10:58

?10.1w次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的數(shù)字邏輯電路,廣泛應(yīng)用于數(shù)字系統(tǒng)中的存儲(chǔ)、計(jì)數(shù)、時(shí)序控制等領(lǐng)域。 一、雙穩(wěn)態(tài)觸發(fā)器的基本特征

![的頭像]() 發(fā)表于

發(fā)表于 08-11 09:56

?688次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的邏輯電路,廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)中。 雙穩(wěn)態(tài)觸發(fā)器的基本概念 雙穩(wěn)態(tài)

![的頭像]() 發(fā)表于

發(fā)表于 08-11 09:59

?1016次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger or Flip-Flop)是一種具有兩個(gè)穩(wěn)定狀態(tài)的數(shù)字電路元件,廣泛應(yīng)用于數(shù)字邏輯電路、存儲(chǔ)器和時(shí)序電路中。 一、雙穩(wěn)態(tài)

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:00

?3123次閱讀

雙穩(wěn)態(tài)觸發(fā)器的兩個(gè)穩(wěn)定狀態(tài)通常被稱為“0”狀態(tài)和“1”狀態(tài),這兩個(gè)狀態(tài)可以分別用來表示二進(jìn)制數(shù)碼的0和1。具體來說: 0狀態(tài) :在此狀態(tài)下,雙穩(wěn)態(tài)觸發(fā)器的輸出Q為0,而其非輸出(通常表

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:05

?1174次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的邏輯電路,廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)中。它具有兩個(gè)基本性質(zhì):記憶性和切換性。 一、雙穩(wěn)態(tài)觸發(fā)器的基本概念 1.1

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:08

?813次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的觸發(fā)器,廣泛應(yīng)用于數(shù)字電路和電子系統(tǒng)中。 一、雙穩(wěn)態(tài)觸發(fā)器的特點(diǎn) 穩(wěn)

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:10

?752次閱讀

雙穩(wěn)態(tài)觸發(fā)器是一種具有兩個(gè)穩(wěn)定狀態(tài)的數(shù)字邏輯電路,它可以在兩個(gè)狀態(tài)之間切換,并且能夠在沒有外部輸入信號(hào)的情況下保持當(dāng)前狀態(tài)。雙穩(wěn)態(tài)觸發(fā)器廣泛應(yīng)用于數(shù)字電子系統(tǒng)中,如存儲(chǔ)

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:15

?904次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的電路,通常用于存儲(chǔ)一位二進(jìn)制信息。在數(shù)字電路中,雙穩(wěn)態(tài)觸發(fā)器是一種非常重要的基本組件,廣泛應(yīng)用于寄存

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:18

?1918次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的電子電路,廣泛應(yīng)用于數(shù)字電路設(shè)計(jì)中。 雙穩(wěn)態(tài)觸發(fā)器的工作原理 雙穩(wěn)態(tài)

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:21

?937次閱讀

雙穩(wěn)態(tài)觸發(fā)器的使用方法主要包括以下幾個(gè)方面: 一、安裝與連接 安裝 :雙穩(wěn)態(tài)觸發(fā)器通常是以集成電路的形式存在,可以通過焊接或插入到電路板上。在安裝過程中,需要注意正確的引腳連接和電路布

![的頭像]() 發(fā)表于

發(fā)表于 08-11 10:23

?645次閱讀

雙穩(wěn)態(tài)觸發(fā)器(Bistable Trigger)是一種具有兩個(gè)穩(wěn)定狀態(tài)的數(shù)字電路,常用于存儲(chǔ)一位二進(jìn)制信息。它在數(shù)字電路設(shè)計(jì)中具有重要應(yīng)用,如存儲(chǔ)器、計(jì)數(shù)器、寄存

![的頭像]() 發(fā)表于

發(fā)表于 08-22 10:12

?777次閱讀

雙穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)

雙穩(wěn)態(tài)觸發(fā)器設(shè)計(jì)

評(píng)論