1.AM解調概論

AM解調中一般的方式是進行全波整流或者半波整流,然后經過一個低通濾波器即可。

本文為數字AM解調。本文采取全波整流加FIR低通濾波器的方式進行解調。

在數字通信系統中一般全波整流實現方式就是取絕對值,半波整流就是直接舍棄負值。

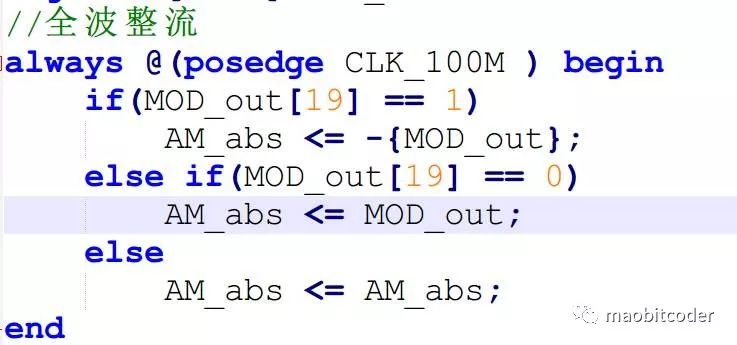

下面一小段代碼就是取絕對值的。

那為什么取絕對值,然后經過低通濾波器就能出來包絡信號呢?關于此處的理論推導。去看書吧。

2.FIR濾波器概述

FIR濾波器是什么樣的結構,有什么樣的特性等等等為了避免大家煩我在這里就不抄課本了。接下來我們就簡單的理解下FIR濾波器。

注意本說法僅僅為新手入門了解。直觀了解FIR濾波器的特性。許多定義和概念可能存在紕漏。希望廣大讀者理性參考。

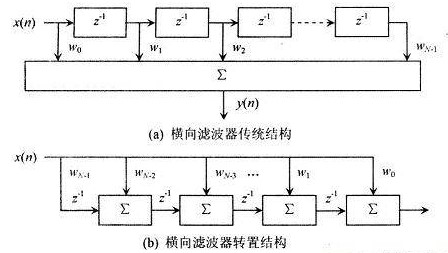

FIR濾波器的結構如下:

我們假設圖中的n就為10。接下來我們拋開FIR這個概念。假設我就是要實現10個數字取個平均數。那么我只要讓h(0),h(1),h(2)……h(9),均為0.1。那么每個數字進來被乘以0.1。然后把10個數字加起來。這就是一個均值濾波。(這種把兩組數據對應相乘然后再加載一起的操作就是卷積的概念)。

依據經驗我們知道,當取的數字越多(即n越大)這個濾波器的輸出值就更穩定。消耗的資源對應著也會越多。

上述舉得例子為求均值。但是假設說我們現在要做更復雜的需求,比如濾除一定頻率的波形。那就需要更加準確的計算各個參數。所幸我們生于偉大的時代,有很多工具可以代替我們算出更合適的抽頭系數。例如matlab的FDATools以及FilterSolutions 2015。

3. FIR濾波器 參數計算

打開Filter Solutions這個軟件。選擇數字濾波器(這個工具功能十分強大,可以設計有源,無源,微帶線,數字等等不同種類的濾波器)。

打開軟件設置如下,因為再實現的時候FIR濾波器采用了完全對稱的結構。我們選擇一個125階的FIR濾波器。選一個合適的窗函數,至于不同的窗函數有什么不同的性能表現在這里就不贅述了。

由于我們的包絡信號是1M。選擇一個2M的低通濾波器。

左上方有各種選項,我們來查看一下它的頻率響應。看起來還是可以的。

然后點擊右上角的SynthesizeFilter、

點擊選項卡的Vec選項,然后Copy Num/Den ,FIR濾波器的抽頭系數就復制到剪切板上了。

4. FIR濾波器 XILINX IP核實現

添加一個FIR濾波器,把系數復制進去(注意只復制括號內的內容)。

可以看到左側的頻率相應圖。其中紅色線為設計的參數。藍色線為經過定點量化后的抽頭系數的頻率響應。圖中的橫坐標為歸一化的頻率(不知道什么叫歸一化頻率的自行百度),縱坐標為幅度的衰減。可以看到設計效果還是可以的。

濾波器也可以選則抽取或者插值或者希爾伯特或者最簡單的單速率濾波器。關于抽取核插值我會在后面更新的文章中寫出,希望大家持續關注。

為了節約資源我們可以設計成抽取濾波器。但是為了避免造成大家的困惑,本文中依然采用單速率的濾波器。

我們進行第二頁的設置

時鐘頻率核輸入采樣頻率均為100M。

接下來進行第三頁的設置最上面的哪個就是抽頭系數的相關設置,在這里我們可以調節量化(定點化)的參數。從而讓前文提到的紅線和藍線更接近(即實現效果更接近設計效果)。當然調節不同的參數,其資源占用和性能表現也會有所不同。下面的幾個選項大家可以自行研究。

后面兩頁內容是設計實現時的面積或者速度優化啥的。大家自行研究在本設計中不做修改。

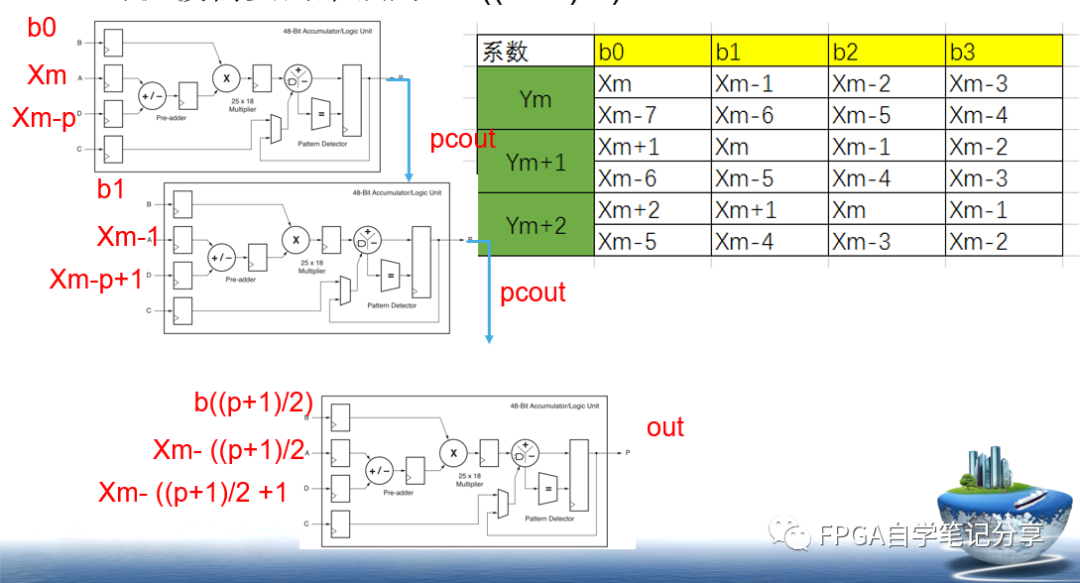

在implementation Details (實現細節中)可以看到數據的輸出格式。其中定點數為[34:17]。也可以發現資源占用為63個乘法器,因為本設計中的FIR濾波器為對稱結構。所以可以省下一半的資源。

這樣我們的FIR濾波器就基本設計完成了。

5. FIR濾波器 XILINX 實現與驗證。

這部分的代碼比較簡單,我們講上節課的Modout信號接出來后進行取絕對值。得到的信號是20bit的。我們選取其中的高16bit送入FIR濾波器。然后就可以得到輸出了,FIR濾波器的輸入輸出信號還有一些有效,握手信號之類的,大家自行查閱手冊了解。

接下來進行仿真,仿真中我們把FIR輸出的[33:17]位單獨拿出來進行顯示即可。最終效果如圖。

-

FPGA

+關注

關注

1629文章

21744瀏覽量

603608 -

低通濾波器

+關注

關注

14文章

474瀏覽量

47423 -

數字信號處理

+關注

關注

15文章

560瀏覽量

45864 -

fir濾波器

+關注

關注

1文章

95瀏覽量

19044 -

半波整流

+關注

關注

0文章

52瀏覽量

12515

發布評論請先 登錄

相關推薦

基于FPGA的FIR數字濾波器的優化設計

基于MATLAB與FPGA的FIR濾波器設計與仿真

基于FPGA的硬件加速器的FIR流水結構濾波器實現、設計及驗證

FPGA的FIR抽取濾波器設計教程

如何使用FPGA實現FIR抽取濾波器的設計

FPGA數字信號處理-FIR濾波器及AM解調

FPGA數字信號處理-FIR濾波器及AM解調

評論