前沿

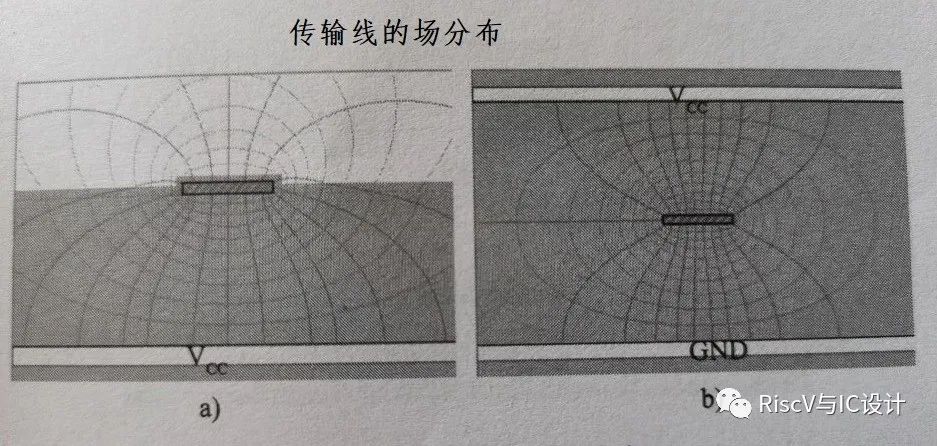

下圖是PCB走線排板時常見的微帶線(左圖)和帶狀線(右圖)的電磁場分布示意圖,其電力線從走線層發出,終止于相關平面層,相關平面層不一定是地線層,可以是電源層,甚至是任意的網絡層,在終止的相關平面層里會產生鏡像電流,這個電流就叫走線層電流的"回流",回流與信號電流構成閉合回路,頻率不是太高時滿足電路理論的基爾霍夫電流定律,兩者相等。

一般高速信號線的回流,我們都會盡量有意安排在地線層或某電源層上,而不是某信號走線層上,否則其串擾可能很大,不適合高速走線,具體分析見后面(三)

一、微帶線的回流分布

微帶線回流密度的大小分布如下圖所示。回流分布在微帶線的下方,且隨著距離微帶線正下方的距離越遠(d越大),回流電流密度越小。

回流電流密度的分布,可以近似用以下公式表示:

隨著d的距離的增大,在距離d范圍以內的回流電流越多,其數據關系如下表所示:

表中也可以通過對上式電流密度I(d)積分,然后進行計算得到。比如對于d/h=2時,則在d=2h以外的電流歸一化數值為(對I0/(pi*h)歸一化):

而歸一化的總電流為

所以包含在-d~d以內的電流的百分比為:

與上表中吻合。按同樣的計算方法,可計算出當d=3h/5h/10h/20h時,分別對應的值為79.5%、87.4%、93.7%96.8%,也非常吻合。

二、帶狀線的回流分布

上圖是帶狀線的回流分布,每個回流層的電流密度依然滿足公式,只不過I0分別對應 I上和I下:

上下兩個回流層的電流總和等于中間走線層的總電流,即I走線 = I上+I下

它們的比例 I上/I下 = h下/h上 。

下圖是上下兩回流層占總走線電流比例的仿真計算結果,例如下層厚度10mil,上層厚度30mil時,從圖示可知上層回流占總回流的比例為25%,則下層為75%,剛好是上下層厚度比例的倒數!

三、相互干擾

當兩根PCB走線靠近時,由上分析可知它們的回流會出現交疊,會相互干擾,靠得越近,交疊越多,干擾越大,如下圖所示:

當d=3h時,根據前式計算可知其密度已經減小為中心位置處的10%,包含的總電流如前計算達到信號電流的79.5%,工程應用中認為d>3h時,相互交疊的影響已經比較小,可以不考慮,這就是抗串擾的走線3h準則。對于射頻模擬信號,簡單使用3h準則是不行的,3h準則主要針對高速數字信號線,而射頻微波的模擬信號走線線,一般都是要加屏蔽的,走成共面波導 CPWG ,CPWG要求兩邊大面積接地,如下圖所示:

CPWG兩邊的接地線打了很多過孔,連接到地平面上

四、CPWG接地孔怎么加?

射頻板上一眼望去,都是密密麻麻的接地孔,據說密集綜合癥者看了會起雞皮疙瘩。接地孔,主要就是防止干擾別人以及被別人干擾。那接地孔一般怎么打?基本規則就是遵循λg/20規則,當然此規則的要求相當低,實際操作時會進行改進。

微帶線周圍加"接地孔"的步驟:

(1) 首先用EDA軟件計算合適的走線寬度和間距,這是在PCB疊層設計時就需要確定的參數,CPWG的信號線到兩邊地線的距離即是我們要知道的接地孔距離微帶線的距離。計算軟件可以使用si9000,這是絕大多數電路板廠家計算阻抗的工具,allegro里面的計算主要針對普通微帶線,無法計算CPWG傳輸線。

(2) 然后按照λg/20來估算接地孔之間的距離,比如信號頻率100MHz, 板材介電常數4.3,那么等效波長λg=c/(f*sqrt(Eff)), Eff為等效介電常數,由于微帶線的上面是空氣,介電常數為1,下面是4.3,所以等效的介電常數既不是1也不是4.3,而是介于兩者之間,和介質厚度密切相關,可以借助keysight的ads里的傳輸線計算工具計算如下:

則λg/20=82.2mm。

對于CPWG傳輸線也是類似的:

如果從這個計算來看的話,整個射頻板可能只需要打幾個過孔就行了,不過一般射頻板都是被打成篩子狀,主要原因有兩個:

- 如果是CPWG傳輸線,盡量沿著銅皮的邊界打孔,保證孔的焊盤與所在的銅皮的邊界重疊;在文獻”Southwest microwave,Optimizing Test Boards for 50 GHz End Launch Connectors“中提到,沿著邊界打接地孔,可以拓展CPWG信號的帶寬。

下圖是沿邊界打接地孔,其S21在25GHz頻率以上時明顯衰減小于上圖,話又說回來,有多少設計的板子需要工作在25GHz以上?所以普通的射頻微波電路板,沒有那么高工作頻率時,可以不一定非要沿邊界打接地孔,前后偏移一些問題不大

- 打密集接地孔可以增加隔離度

在文獻”Peter Vizmuller, “RF Design Guide: Systems, Circuits and Equations,” 1995, Artech House“中利用波導截止頻率的觀點分析指出:打密集的接地過孔可以使PCB的CPWG走線向CPWG外其他地方的輻射降低數個db(3-5db),這是把射頻板子打成篩子的主要原因之一,另外一個原因就是實現充分良好接地。

實際操作時,如果計算出來的λg/20比較大(通常都是這樣),可以選擇2mm~2.5mm的間隔打接地孔,如果λg/20比較小就適當減小間隔,但是需要保證:

- 滿足PCB廠家加工要求,接地孔太密集,PCB廠家加工有問題

- 接地孔不要把其他平面層打破,這樣會造成回流面積增大,容易引起信號完整性問題,特別是使用通孔時這個問題要注意,有時板子密度非常大,無法滿足不要把其他平面層打破且明顯引起信號完整性問題,此時可以使用埋孔或盲孔(當然成本會比較高)。

五、差分線的保護地

如果需要給差分信號加保護地,為了不破壞差分線之間的對稱平衡關系,要求兩邊都要同時加地,而且要求地與差分線的距離至少要大于兩倍的差分線的間距,如下圖。

-

衰減器

+關注

關注

4文章

640瀏覽量

34447 -

信號完整性

+關注

關注

68文章

1416瀏覽量

95606 -

射頻電路

+關注

關注

35文章

430瀏覽量

43379 -

PCB走線

+關注

關注

3文章

134瀏覽量

13968 -

EDA芯片

+關注

關注

0文章

7瀏覽量

6818

發布評論請先 登錄

相關推薦

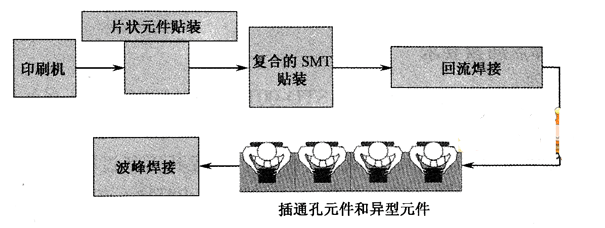

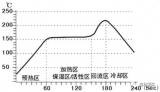

通孔回流焊簡述

通孔回流焊接組件的本體材料和設計

通孔回流焊錫膏的選擇

分享一下波峰焊與通孔回流焊的區別

回流通孔件的簡易方法

什么是通孔回流焊?有什么優點?

通孔回流焊工藝的優點_通孔回流焊工藝的缺點

通孔回流焊工藝原理_通孔回流焊接工藝的優缺點

什么是通孔回流焊工藝,在電子組裝中有什么作用

通孔回流焊工藝在PCB組裝中有什么樣的作用

通孔回流焊的定義

淺析射頻電路的接地孔與回流問題

淺析射頻電路的接地孔與回流問題

評論