我們知道,SiC MOSFET現階段最“頭疼”的問題就是柵氧可靠性引發的導通電阻和閾值電壓等問題,最近,日本東北大學提出了一項新的外延生長技術,據說可以將柵氧界面的缺陷降低99.5%,溝道電阻可以降低85.71%,整體SiC MOSFET損耗可以降低30%。

9月28日,東北大學和CUSIC在“ICSCRM2023”會議上宣布,他們針對SiC MOSFET開發一種“同步橫向外延生長法(SLE法)”,目的是通過在4C-SiC外延層上再生長3C-SiC層,來解決高溫柵氧導致的可靠性問題。

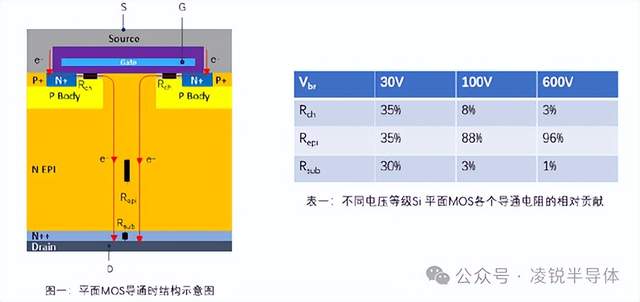

為什么需要怎么做?傳統4C-SiC柵氧層制備最大的問題是溫度太高(約1300℃),這會導致SiO2/SiC界面出現碳殘留,導致溝道遷移率低,以及可靠性和閾值電壓等缺陷。

如果通過3C-SiC來制備柵氧層,工藝問題可以低于900℃,可以完美解決這個問題。根據“行家說三代半”之前的報道,3C-SiC MOSFET的n溝道遷移率范圍為100-370 cm2/V·s。而4H-SiC MOSFET通常為20-40cm2/V·s,溝槽器件為6-90 cm2/V·s,京都大學的技術可以做到131 cm2/V·s,但也比3C-SiC MOSFET低3倍左右。

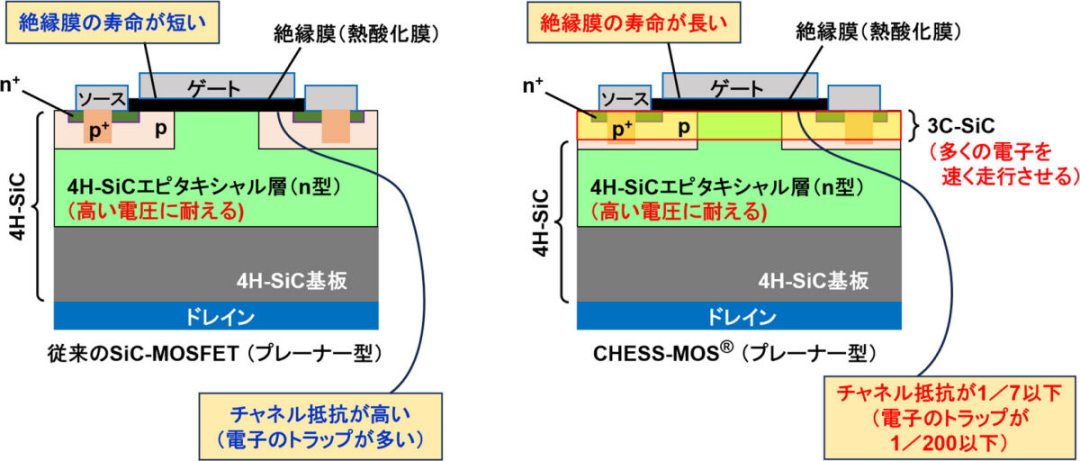

東北大學根據這思路制備了一種CHESS-MOSFET,即在4C-SiC疊加3C-SiC層,如下圖:

采用4H-SiC外延層的MOSFET(左),CHESS-MOS(右)

該研究團隊表示,CUSIC 設計的“CHESS-MOS”能夠同時降低功率損耗并確保長期可靠性。

該器件的特點是采用了混合外延層,既利用了3C-SiC的高遷移率,也利用了4H-SiC層的高耐壓。

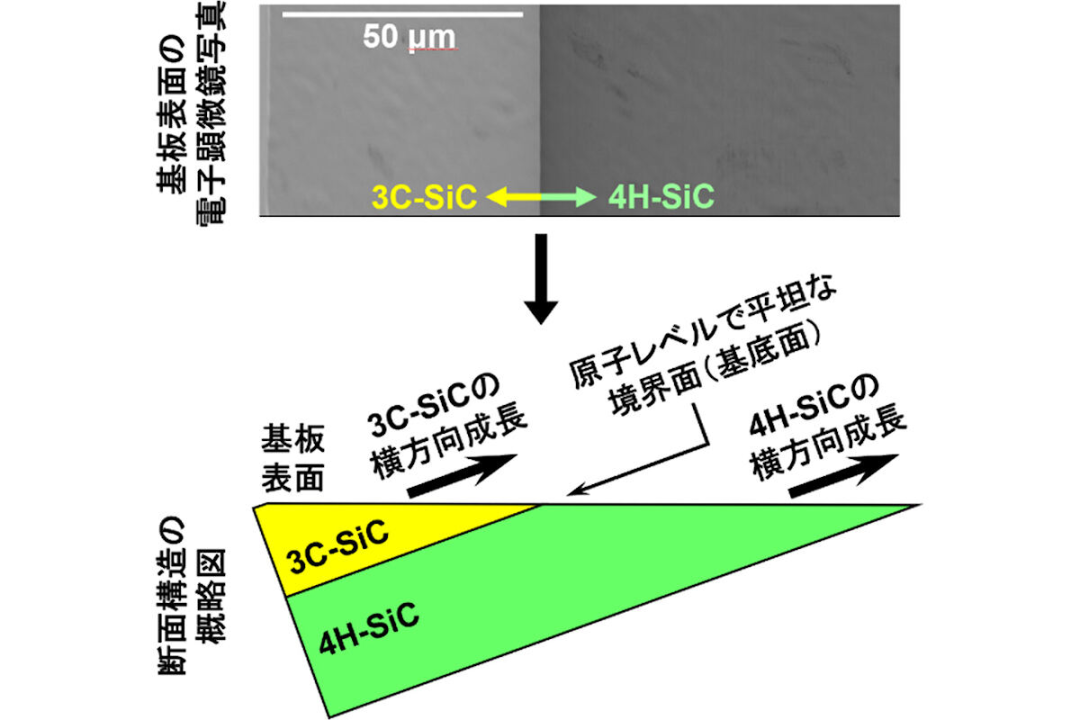

然而,要實現這一目標需要開發新的外延和晶體生長技術,以無縫堆疊兩種不同晶格SiC層。因此,該研究團隊開發了SLE方法。

簡單來說,SLE方法是在4H-SiC的延伸基面上生長3C-SiC層,3C-SiC也沿著4H-SiC基面延伸,這樣使得3C-SiC層與4H-SiC層之間的界面非常平坦,沒有原子偏差。

掃描非線性介電常數顯微鏡測量結果顯示,3C-SiC表面的缺陷密度僅為4H-SiC的1/200,表明SLE方法可以大幅降低界面缺陷密度,預測CHESS-MOS可將損耗降低30%以上。

而且,由于基于3C-SiC的CHESS-MOS還可以極大地降低絕緣膜漏電流密度,消除絕緣膜在短時間內劣化的風險,提高器件的長期可靠性。

在實驗中,該團隊還發現,使用SLE法可以形成3C-SiC/4H-SiC/3C-SiC/4H-SiC等雙量子阱結構的現象,那么通過有意地形成這種堆疊結構,可以制造高頻器件,而在以前,SiC半導體器件被認為難以實現。

此外,該團隊還有另一個新發現,他們通過使用SLE方法在半絕緣4H-SiC襯底上生長3C-SiC層,可避免由于與襯底電容耦合而導致的高頻信號衰減問題,這將有望為高頻集成電路的大規模生產鋪平道路。

最為重要的是,SLE方法能夠直接在SiC外延層表面的一部分引入不同的晶體結構,而無需大幅改變現有的SiC MOSFET器件形狀或制造工藝,預計該技術很快可以導入器件生產線。

審核編輯:劉清

-

MOSFET

+關注

關注

147文章

7203瀏覽量

213664 -

SiC

+關注

關注

29文章

2841瀏覽量

62742 -

SLE

+關注

關注

0文章

13瀏覽量

8514 -

漏電流

+關注

關注

0文章

263瀏覽量

17047 -

閾值電壓

+關注

關注

0文章

73瀏覽量

51458

原文標題:SiC MOS新技術:溝道電阻可降85%

文章出處:【微信號:SiC_GaN,微信公眾號:行家說三代半】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

mos管和MOS管的使用方法

mos驅動電阻如何選擇計算

mos管gs之間電阻阻值怎么選

MOS管驅動電阻的測試方法

MOS管驅動電阻大小的影響

淺談電纜的電阻和電壓降

場效應管怎么區分n溝道p溝道(MOS管導通條件)

介紹一款用于電機驅動電路的N溝道MOS管HKTG90N03

淺析SiC MOS新技術:溝道電阻可降85%

淺析SiC MOS新技術:溝道電阻可降85%

評論