什么是ACLR?

鄰道泄露抑制比是用于衡量下行的發射性能,是主信道的發射功率與測得的相鄰信道的功率之比。ACLR值越低,表示相臨信道的功率的干擾越小,說明系統的性能越好。一般用dBc作為單位。

現在有些廠家或運營商的招標規范喜歡用“輸入互調抑制”來定義該指標,主要是目前直放站系統需要兼容多制式,通過一個指標去衡量2G、3G、4G和5G的ACLR。

另外一個原因是由于ACLR的指標太嚴格,如果設備是沒有DPD或是純模擬的,那么實現這個指標完全靠末級的功放了,要滿足這么好的ACLR,一般得使用大功率功放,這樣整機的功耗和散熱又受影響了。所以提出一個新指標,就不用參考3GPP,進而降低下標準。

那我們看看什么是輸入互調?

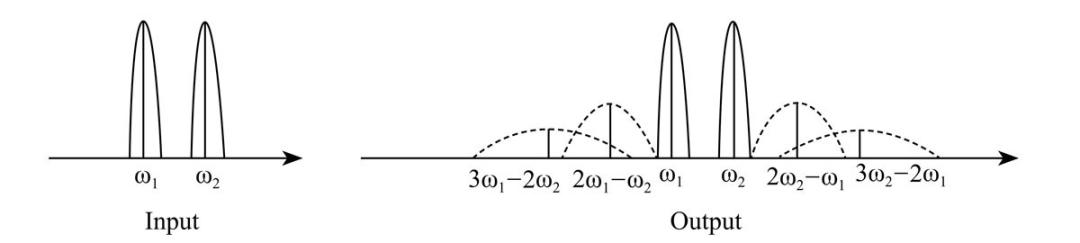

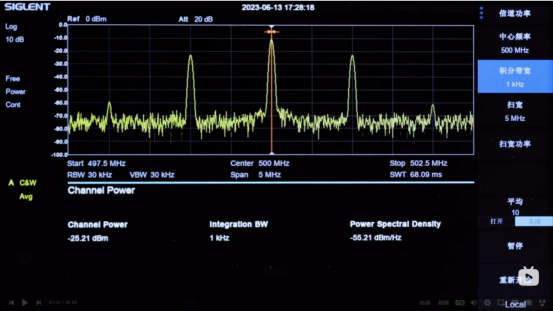

輸入互調是指兩個及兩個以上載波所導致的帶內及帶外互調干擾信號和抑制能力。類似下圖所述:

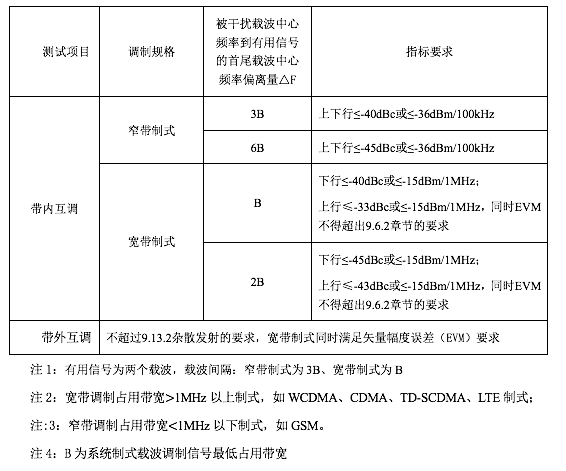

輸入互調的指標如下:

為什么需要ACLR?

ACLR、輸入互調和SEM都是衡量系統的工作頻段內的“帶外雜散”。由于調制過程中和傳輸過程中的非線性產生的相鄰有用信道外的有害雜散。這個不包含雜散發射,雜散發射是指工作頻段外的,而ACLR和SEM衡量的帶外雜散都是屬于工作頻段內。

由以上定義可以知道,ACLR和SEM類似,衡量設備共址的情況下,別互相干擾對方。

但ACLR和SEM還是有區別的,具體區別下期可以展開聊聊。

怎么設計才能滿足ACLR?

這個指標優化起來需要注意以下幾個方面:

1、末級功放的線性:主要是末級和推動級的功放的性能不好,特別是級聯后的線性,需要在設計前測試、仿真和計算。

2、信噪比不足:主要的輸出功率過小,特別是上行。輸出功率過小,底噪又很大,導致信噪比不足,這樣滿足不了ACLR。需要提高輸出功率或者降低底噪。

3、雜散泄露:特別是DA產生的雜散,特別是零中頻方案的設備,會有一個直流雜散,需要優化到底噪之下。

4、DPD性能:除了小信號時功放的性能需要保證10dB以上的預留外,DPD算法的性能也需要保證,這都需要使用不同的制式信號去調測的。

-

SEM

+關注

關注

0文章

247瀏覽量

14582 -

零中頻

+關注

關注

0文章

64瀏覽量

9187 -

DPD算法

+關注

關注

0文章

4瀏覽量

7067 -

ACLR

+關注

關注

0文章

12瀏覽量

8143

發布評論請先 登錄

相關推薦

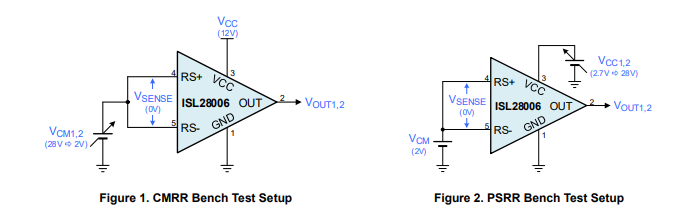

ISL28006:測量共模和電源抑制比

什么是ACLR?

怎么測ADS1299芯片的共模抑制比?

INA128共模抑制比波形失真,是為什么?

如何測定儀表放大器的共模抑制比?

影響電路共模抑制比的因素有哪些?如何去提高電路的共模抑制比?

運放的共模抑制比和電源抑制比對輸出精度的影響是什么?

如何理解運放的電源抑制比參數?

求助,關于INA333共模抑制比問題求解

LDO電源抑制比的測量方法

消除共模噪聲的秘密武器-共模抑制比

什么是鄰道泄露抑制比(ACLR)?

什么是鄰道泄露抑制比(ACLR)?

評論