談到package,用過VHDL的工程師并不陌生。實際上,SystemVerilog中的package正是從VHDL引入的,以進一步增強其在系統級的描述能力。我們來看一下SystemVerilog中package的使用方法與注意事項。 SystemVerilog中的package需要在關鍵字package和endpackage之間進行定義,其包含的內容可以是parameter,localparam,const,typedef,task,function,import,export和time unit。當然,package中也可以包含一些不可綜合的用于驗證的內容如class。

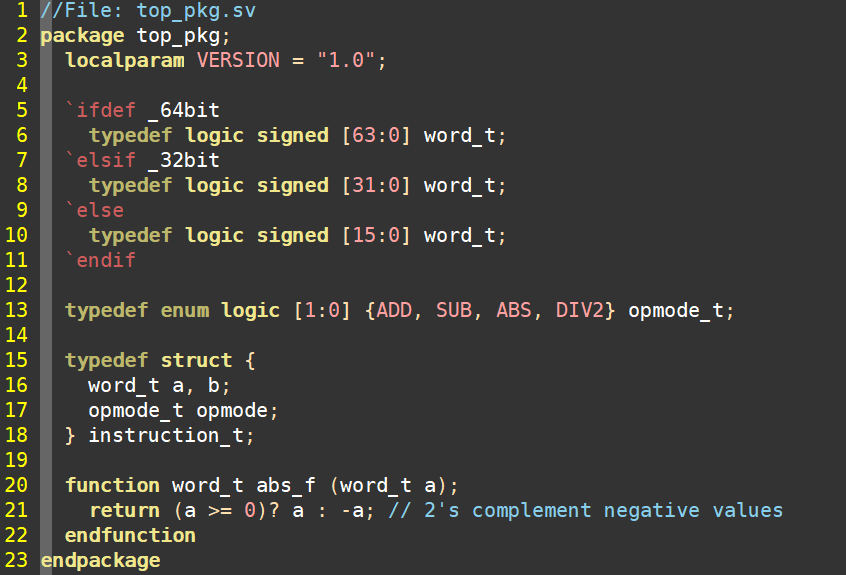

我們來看一個具體的例子,如下圖所示代碼片段。代碼第2行通過關鍵字package表明其描述類別,package之后的top_pkg是package的名字。代碼第5行至第11行以條件編譯的方式結合typedef定義了數據類型。代碼第13行通過typedef enum定義了枚舉類型。代碼第15行到第18行通過typedefstruct定義了結構體。代碼第20行至第22行定義了function。代碼第23行以endpackage確定package結束。

從可綜合的SystemVerilog代碼風格角度而言,需要注意:對于需要定義在package中的常數,應采用localparam或const定義,而不要使用parameter定義。此外,結構體應定義在package中,而不是以獨立的.sv文件存在。

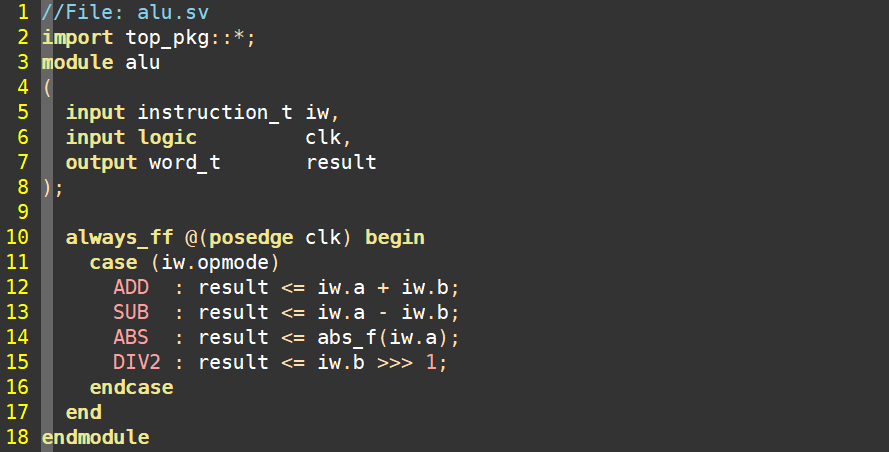

當需要使用package中的對象時,就需要導入package,如下圖所示代碼片段。代碼第2行通過import導入package。“*”表示導入top_pkg中的所有內容。也可以只導入需要使用的package中的某個具體內容,例如

import top_pkg::word_t;

如果使用此方法導入用戶定義的枚舉類型時,需要明確導入使用到的枚舉標簽,如下所示:

import top_pkg::ADD;

import top_pkg::SUB;

import top_pkg::ABS;

import top_pkg::DIV2;

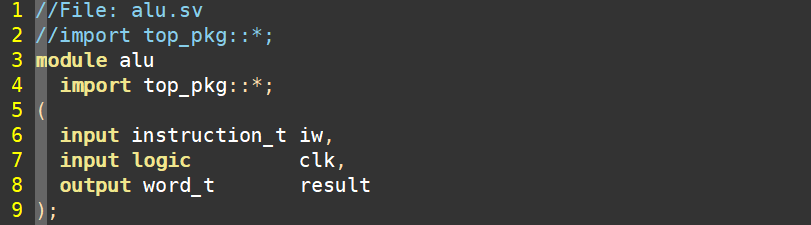

import package可以放在module聲明之前,如上圖所示代碼第2行的位置,也可以放在端口聲明之前,如下圖所示代碼片段的第4行。兩者的效果是一樣的,即:端口聲明部分和module內的語句均可使用導入的package內容。

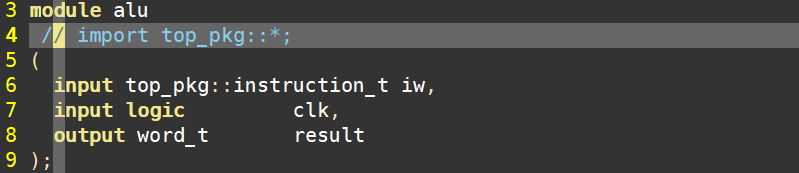

盡管可以使用如下圖所示代碼片段第6行所示方式,但實際工程中并不建議這么使用,這會導致代碼變得冗長。工程實踐表明,采用類似于“importtop_pkg::*;”的方式更為方便,也更為明了。

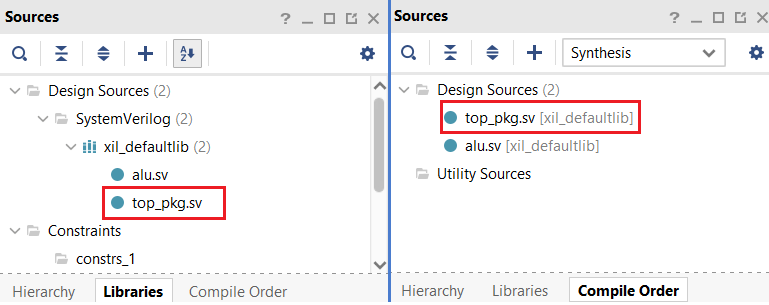

Vivado是支持package的。只需將package單獨定義在一個后綴為.sv的文件中即可。Vivado會自動將package放在首位進行編譯,如下圖所示。

審核編輯:劉清

-

Vivado

+關注

關注

19文章

815瀏覽量

66857 -

Verilog語言

+關注

關注

0文章

113瀏覽量

8297 -

sub

+關注

關注

0文章

13瀏覽量

2268

原文標題:說說SystemVerilog的Package

文章出處:【微信號:Lauren_FPGA,微信公眾號:FPGA技術驛站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

信號發生器的使用方法及注意事項

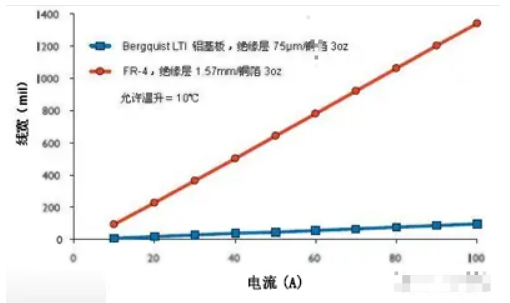

PCB承載大電流的操作方法和注意事項

看一下SystemVerilog中package的使用方法與注意事項

看一下SystemVerilog中package的使用方法與注意事項

評論