高VDS尖峰可能會導致MOSFET雪崩,進而導致器件性能下降和可靠性問題···

電源行業的主要目標之一是為數據中心和5G等應用中的電源設備帶來更高的電源轉換效率和功率密度。與具有單獨驅動器IC的傳統分立MOSFET相比,將驅動器電路和功率MOSFET(稱為DrMOS)集成到IC中可提高功率密度和效率。

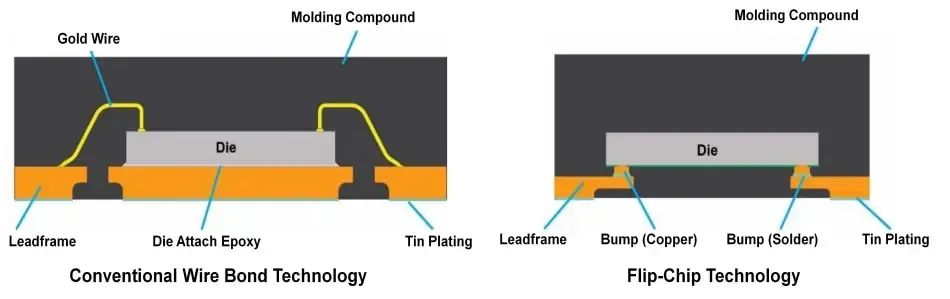

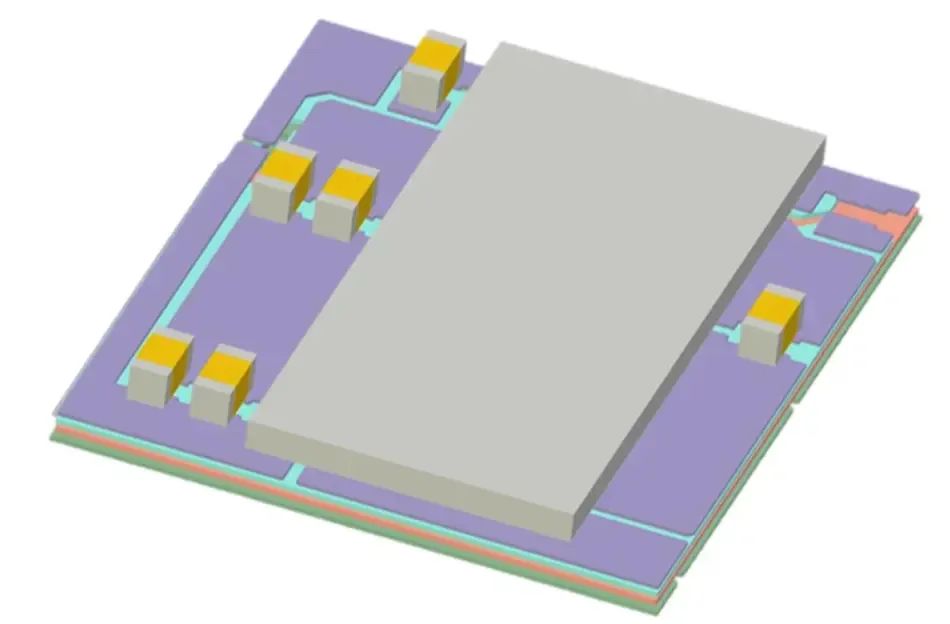

此外,DrMOS的倒裝芯片技術通過縮短響應時間和減小芯片與封裝之間的電感,進一步優化了穩壓器的性能(圖1)。

圖1 這是傳統接合線和倒裝芯片技術之間的比較。資料來源:Monolithic Power Systems

然而,基板和PCB上的寄生電感會對漏-源極電壓(VDS)尖峰產生重大影響,這是由于寄生電感與MOSFET輸出電容(COSS)之間的諧振造成的。高VDS尖峰可能會導致MOSFET雪崩,進而導致器件性能下降和可靠性問題。為了防止MOSFET發生雪崩擊穿,有多種方法可以減輕電壓應力。

第一種方法是在DrMOS上應用更高電壓的雙擴散MOSFET(DMOS)工藝。如果在功率MOSFET設計中采用此工藝,由于同一空間內并聯DMOS的數量減少,DrMOS的導通電阻(RDS(ON))會更高。

第二種方法是使用緩沖電路來抑制電壓尖峰。然而,這種方法會導致緩沖電路產生額外的損耗。此外,添加緩沖電路可能無法有效降低MOSFET的VDS尖峰,因為引起諧振行為的雜散電感主要集成在DrMOS的封裝中。

當嘗試提高穩壓器效率并減少MOSFET的電壓尖峰時,上述權衡的方法可能會導致難以量化和優化寄生電感對PCB和基板的影響。

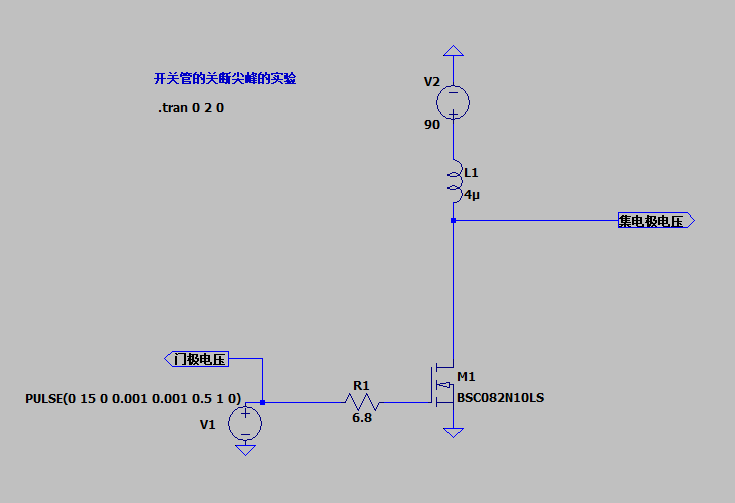

本文將首先討論寄生電感的建模。接下來,在SPICE仿真工具中應用等效寄生電路模型來預測VDS開關尖峰。實驗結果將用于驗證寄生模型的可行性。

DrMOS上的寄生電感建模

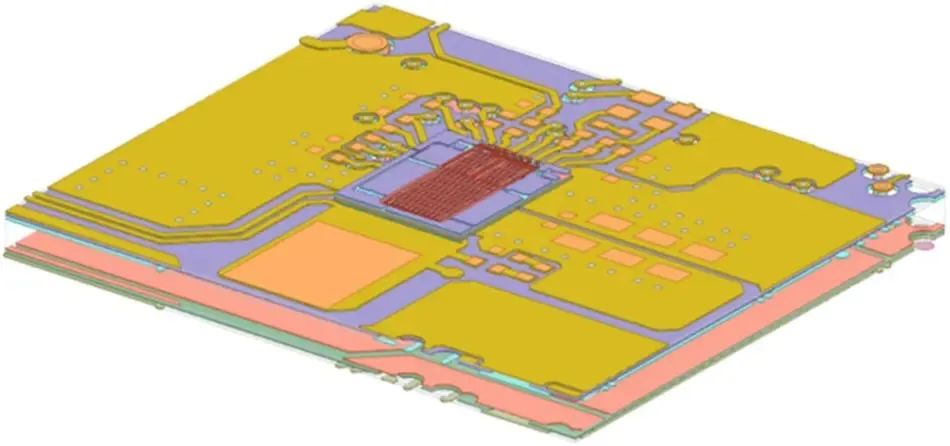

為了模擬寄生電感,我們構建了DrMOS和PCB的3D結構以進行仿真分析(圖2)。材料、堆疊信息和PCB以及封裝層厚度等參數對于建模準確性至關重要。

圖2 DrMOS和PCB的3D建模結構可用于獲取寄生電感。資料來源:Monolithic Power Systems

對PCB和DrMOS進行3D建模后,可以通過ANSYS Q3D提取器對寄生電感行表征和獲取。由于本文重點關注MOSFET的VDS尖峰,因此主要的仿真設置是電源網絡和驅動器網絡上的寄生參數。

當考慮從Q3D提取器獲得的寄生分量時,可以在不同頻率條件下選擇寄生電感矩陣(包括DrMOS上每個網絡的自項和互項)。由于高側MOSFET(HS-FET)和低側MOSFET(LS-FET)上的VDS諧振頻率在300MHz至500MHz之間,因此采用300MHz條件下的寄生電感矩陣進行進一步的行為模型仿真。

SPICE上的行為模型仿真

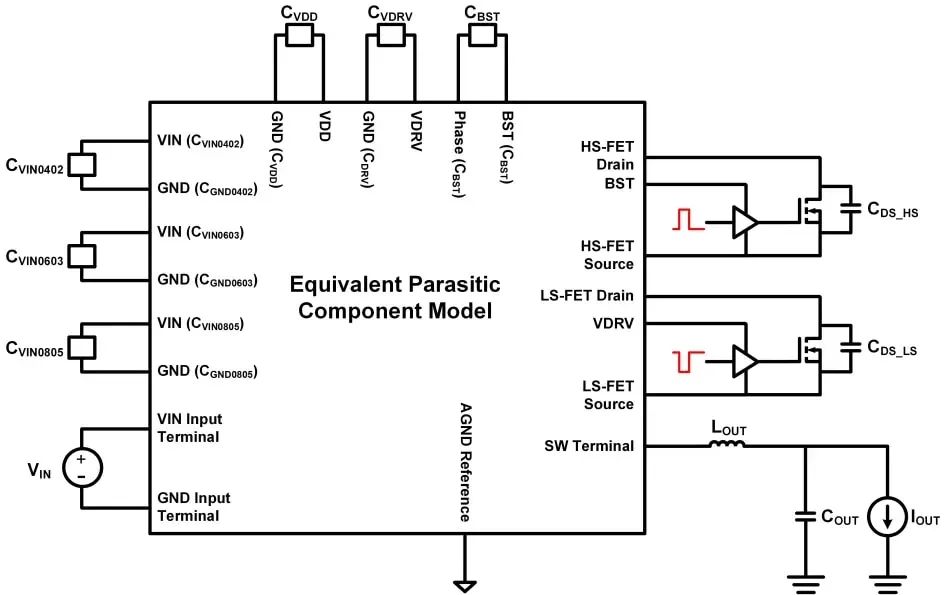

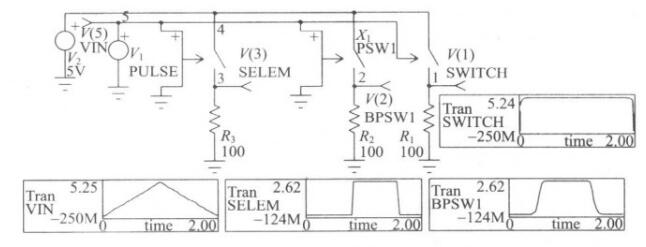

從Q3D導出等效寄生元件模型后,PCB上不同類型去耦電容的影響將被考慮在內。由于在多層陶瓷電容器(MLCC)上施加直流電壓后電容會衰減,因此必須考慮每個MLCC在特定直流電壓偏置條件下的等效電路。每個考慮因素都應基于MLCC的工作電壓。圖3顯示了SPICE上行為模型仿真的電路配置。

圖3 可以使用行為模型仿真來配置電路。資料來源:Monolithic Power Systems

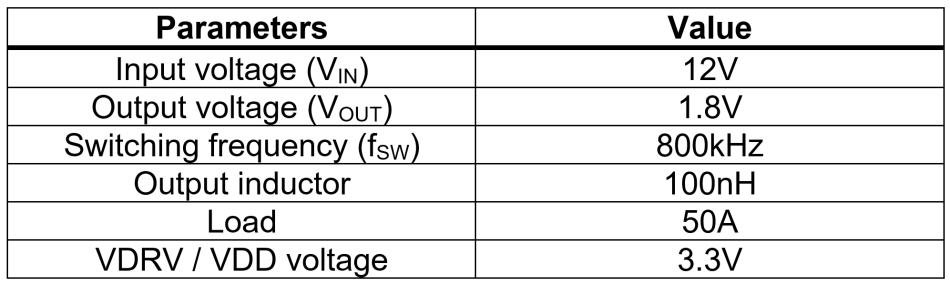

表1顯示了基于圖3所示原理圖的仿真和測量條件。

表1 數據為實驗測試臺的結果。資料來源:Monolithic Power Systems

優化寄生電感

要在不影響效率的情況下抑制VDS尖峰,優化PCB和封裝上的寄生電感至關重要。借助先進的封裝技術,可以將輸入電容器集成在封裝中,以縮短去耦路徑(圖4)。在封裝內并聯嵌入式電容可以有效降低DrMOS上的等效寄生電感。

圖4 具有嵌入式電容器的3D DrMOS結構優化了VDS尖峰。資料來源:Monolithic Power Systems

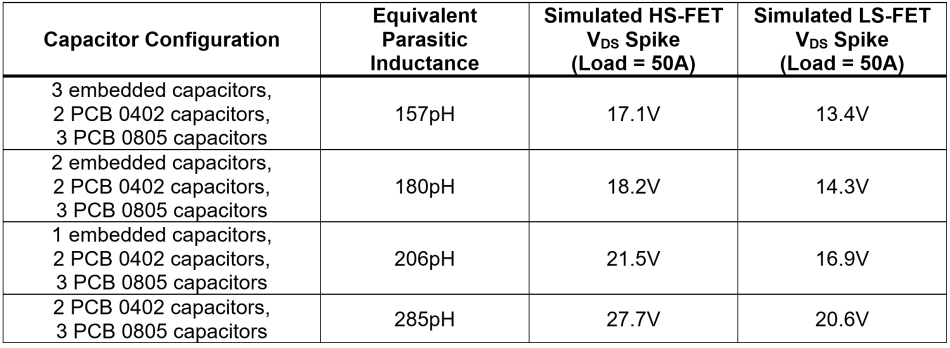

表2顯示了在DrMOS上使用不同去耦電容器配置時的等效寄生電感和VDS尖峰。

表2 顯示了不同電容器配置下的等效寄生電感和VDS尖峰。資料來源:Monolithic Power Systems

如表2中的仿真結果所示,不僅等效寄生電感降低,而且MOSFET上的VDS尖峰也得到抑制。此外,由于MLCC的低ESR特性,嵌入式輸入電容器不會產生額外的功率損耗。因此,可以添加不同的嵌入式輸入電容器來減少DrMOS應用中的寄生電感。

帶有嵌入式電容器的DrMOS

本文解釋了寄生電感對VDS開關尖峰的影響,以及防止VDS開關尖峰導致MOSFET雪崩擊穿的幾種方法。為了量化寄生電感對VDS開關尖峰的影響,首先引入了寄生電感建模,然后提出了SPICE上的行為建模。

通過SPICE獲得的結果與MP87000-L等DrMOS解決方案的實驗結果非常吻合,這意味著該行為模型可以準確預測MOSFET上發生雪崩擊穿的風險。

為了有效抑制VDS尖峰而不需要任何權衡取舍,在封裝中引入了嵌入式電容器。行為模型仿真證實,這些電容器可以降低等效寄生電感,從而降低VDS尖峰,而不會產生額外損耗。

審核編輯:劉清

-

MOSFET

+關注

關注

148文章

7811瀏覽量

217200 -

驅動器

+關注

關注

54文章

8472瀏覽量

148488 -

PCB板

+關注

關注

27文章

1461瀏覽量

52778 -

電源轉換器

+關注

關注

4文章

344瀏覽量

34933 -

寄生電感

+關注

關注

1文章

158瀏覽量

14774

原文標題:怎么通過SPICE仿真來預測VDS開關尖峰?

文章出處:【微信號:PCB電子電路技術,微信公眾號:PCB電子電路技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論