在本文中,我們將介紹噪聲和電源抑制比 (PSRR) 在低壓差 (LDO) 穩(wěn)壓器中的影響。讓我們簡(jiǎn)要討論一下什么是 LDO。

低壓降穩(wěn)壓器

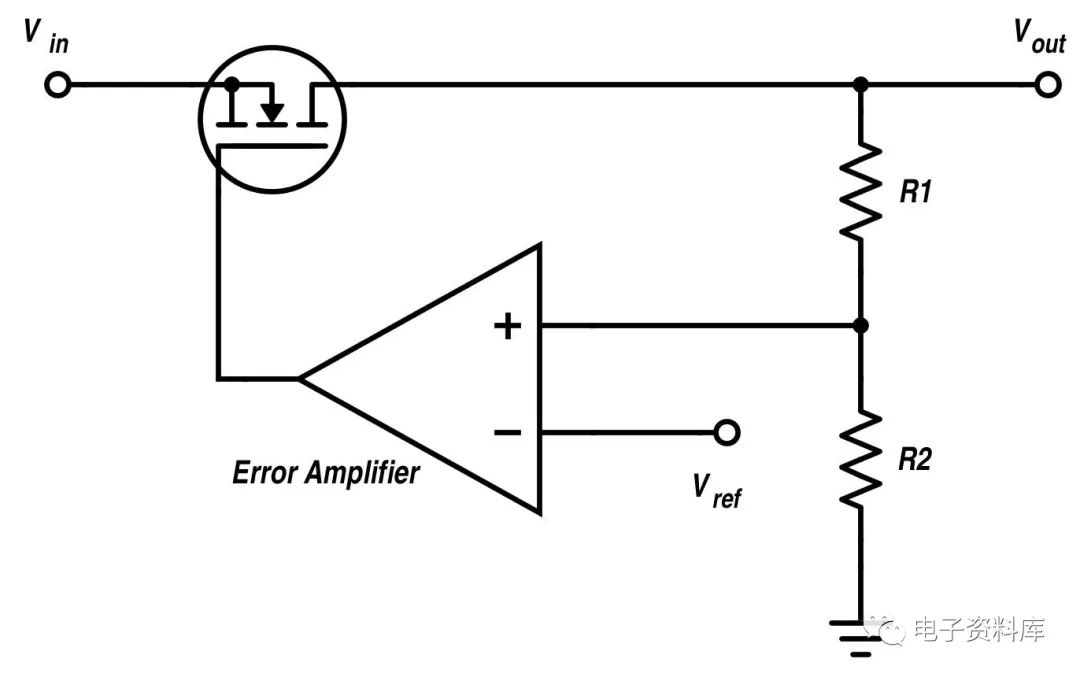

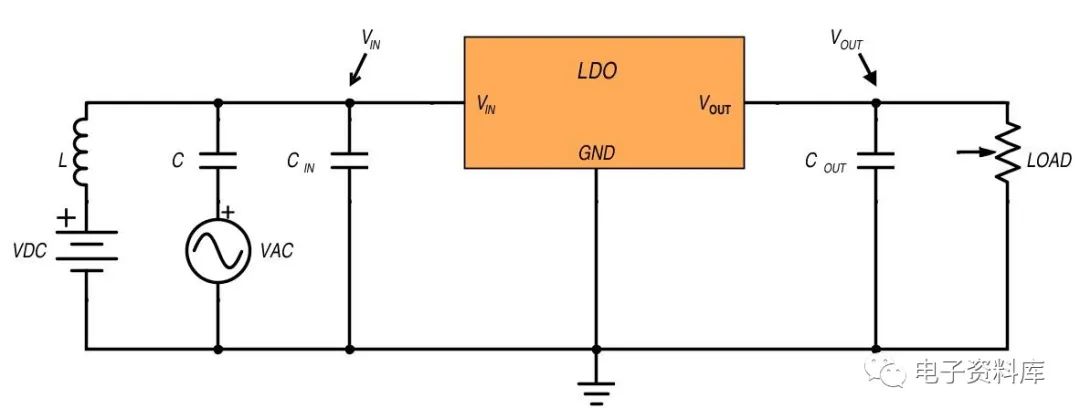

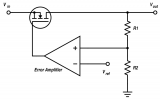

低壓差或 LDO 穩(wěn)壓器是一種直流線性穩(wěn)壓器,即使提供給它的輸入電壓幾乎等于輸出電壓,也可以通過它來(lái)控制輸出電壓。LDO 有兩個(gè)組件——功率 FET 和一個(gè)差分放大器(誤差放大器)。LDO的配置見下圖:

低壓降穩(wěn)壓器 (LDO) 中的噪聲

低壓差 (LDO) 穩(wěn)壓器中的噪聲源可分為兩大類,即固有的和外部的。LDO 中的固有噪聲有兩個(gè)主要來(lái)源:

- 內(nèi)部參考電壓。

- 誤差放大器。

而外部噪聲就像噴氣式飛機(jī)的噪聲,是從電路外部的源傳遞的。

為了獲得 15 μA 或更低的靜態(tài)電流,現(xiàn)代 LDO 使用幾十納安的內(nèi)部偏置電流進(jìn)行管理。

降低 LDO 中的噪聲

降低 LDO 噪聲的兩種主要方法是:

- 濾波參考電壓(基準(zhǔn)電壓)

- 降低誤差放大器的噪聲增益

在某些 LDO 中,使用外部電容器對(duì)基準(zhǔn)進(jìn)行濾波。現(xiàn)實(shí)情況是,為了達(dá)到低噪聲條件,許多所謂的超低噪聲 LDO 需要一個(gè)外部噪聲衰減電容器。不幸的是,由于沒有進(jìn)入反饋節(jié)點(diǎn)的權(quán)利,因此無(wú)法降低固定輸出 LDO 的輸出噪聲。如果誤差放大器的噪聲貢獻(xiàn)大于參考噪聲的貢獻(xiàn),則可以通過降低誤差放大器的噪聲增益來(lái)降低 LDO 的整體噪聲。

確定誤差放大器是否是主要噪聲貢獻(xiàn)者的唯一方法是將固定版本的噪聲與特定 LDO 的可變版本的噪聲進(jìn)行比較。如果固定 LDO 的噪聲量小于可變 LDO,那么我們可以說(shuō)誤差放大器是主要的噪聲源。

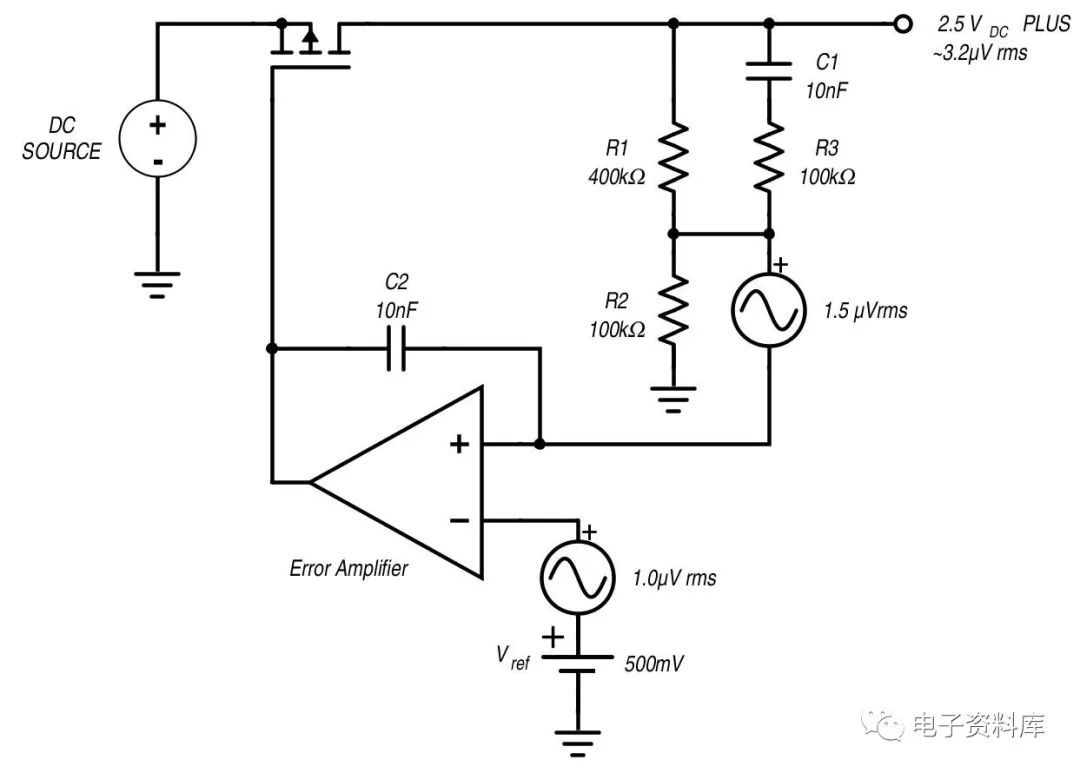

該圖顯示了一個(gè) 2.5 V 輸出可修改 LDO,其中 R1、R2、R3 和 C1 是外部組件。

R3 用于將放大器的高頻增益設(shè)置為 1.5 倍至 2 倍。而C1則用于將降噪系統(tǒng)(C1、R1和R3)的低頻零位設(shè)置在10Hz和100Hz之間,以確保將噪聲降低到1/f。

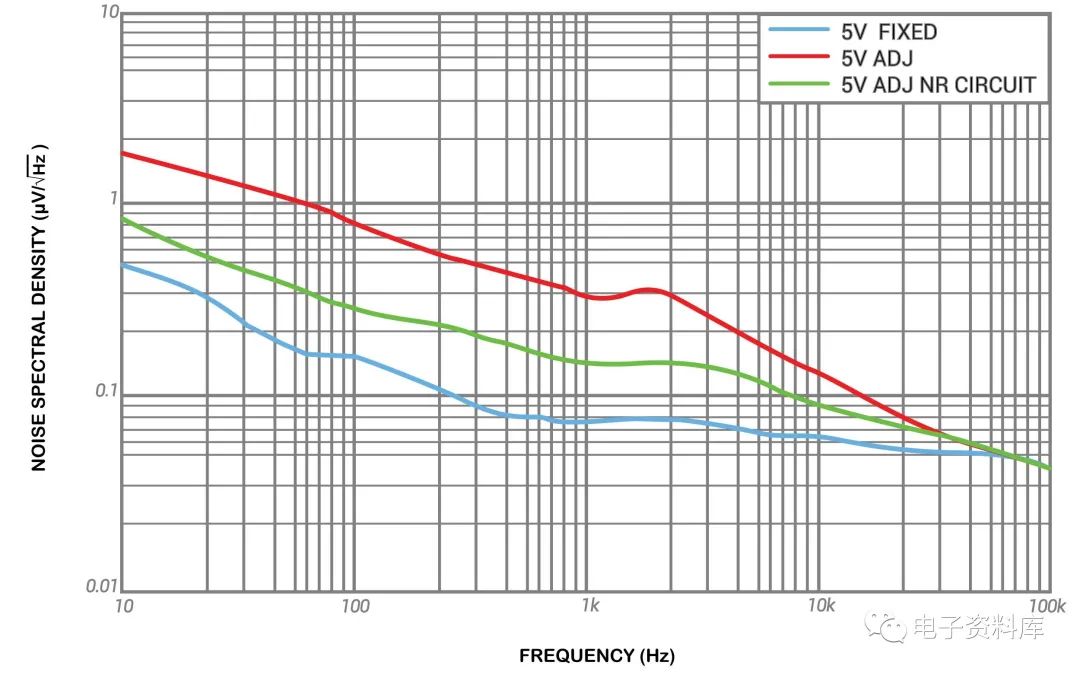

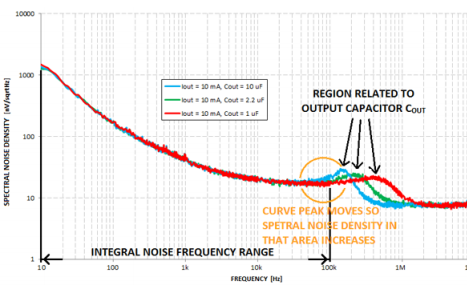

降噪 (NR) 網(wǎng)絡(luò)對(duì)高壓自適應(yīng) LDO 的噪聲頻譜密度的結(jié)果如下圖所示。

在上圖中,可以看出,在 20 Hz 和 2 kHz 之間,噪聲性能提高了大約三倍 (~10 dB)。

LDO 中的電源抑制比

PSRR 代表“電源抑制比”,隨著集成水平的提高,它在現(xiàn)代片上系統(tǒng) (SoC) 設(shè)計(jì)中逐漸成為越來(lái)越重要的參數(shù)。

PSRR 是兩個(gè)傳遞函數(shù)之間的比率:

? 電源節(jié)點(diǎn)到輸出節(jié)點(diǎn)的傳遞函數(shù),即 (Asupply(ω))

? 輸入節(jié)點(diǎn)到輸出節(jié)點(diǎn) A(ω) 的傳遞函數(shù)。A(ω) 也稱為開環(huán)傳遞函數(shù)。

PSRR(ω) = 20 · log [A(ω) /Asupply(ω)] [dB]

在哪里,

1/ Asupply(ω) 是電源增益的倒數(shù),稱為 PSR。

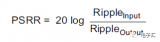

從上面的等式可以明顯看出,PSRR 與 A(ω) 成正比,與 Asupply(ω) 成反比。因此,如果 Asupply(ω) 減小而開環(huán)增益 A(ω) 增大,則 PSRR 將增大。PSRR 基本上是 LDO 抑制輸入側(cè)出現(xiàn)的紋波的能力。在理想的 LDO 中,直流頻率將是唯一的輸出電壓。然而,由于高頻下出現(xiàn)的小尖峰,誤差放大器并不具有完美的功能。考慮到紋波,PSRR 表示如下:

PSRR=20 xlog RippleinputRippleoutput

實(shí)際例子

LDO 具有:

PSRR= 55 分貝

頻率 = 1 MHz

輸入紋波 = 1mV

它可以將該頻率下的 1 mV 衰減至輸出端僅 1.78 μV。因此,PSRR 增加了 6dB,這等于衰減增加了 2 倍。

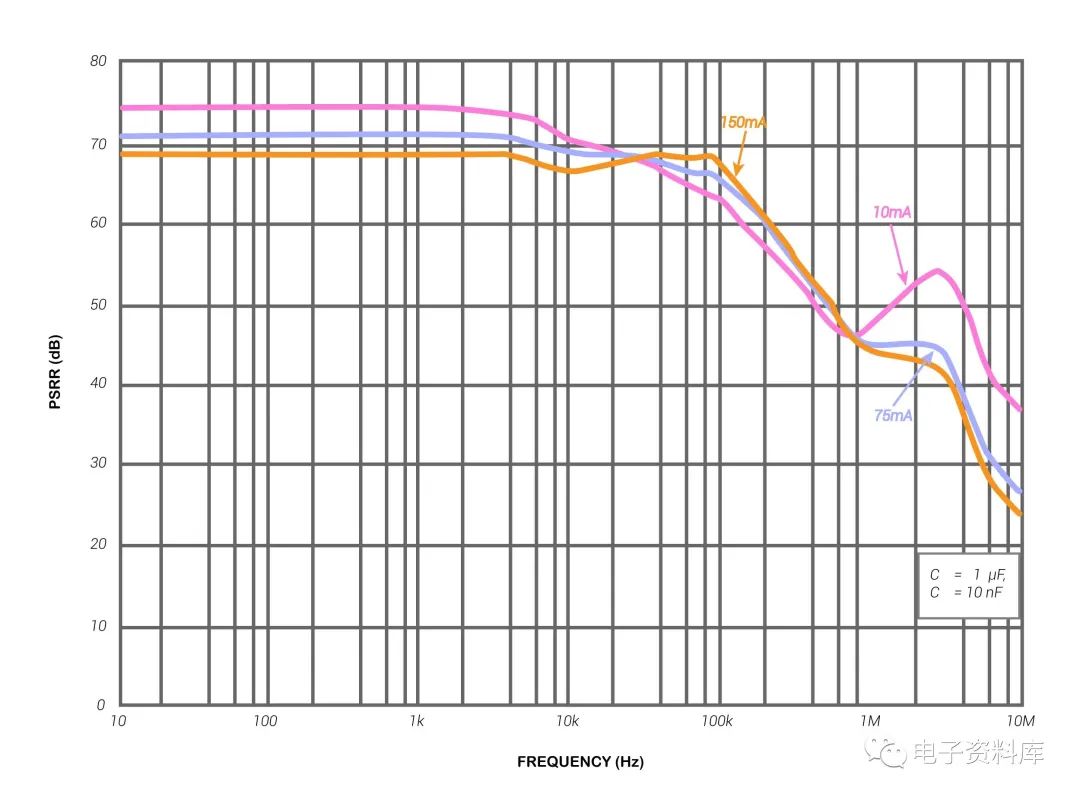

大多數(shù) LDO 在較低頻率(通常為 10 Hz – 1 kHz)下具有相對(duì)較高的 PSRR。在寬帶上具有高 PSRR 的 LDO 可以抑制非常高頻的噪聲,就像開關(guān)產(chǎn)生的噪聲一樣。

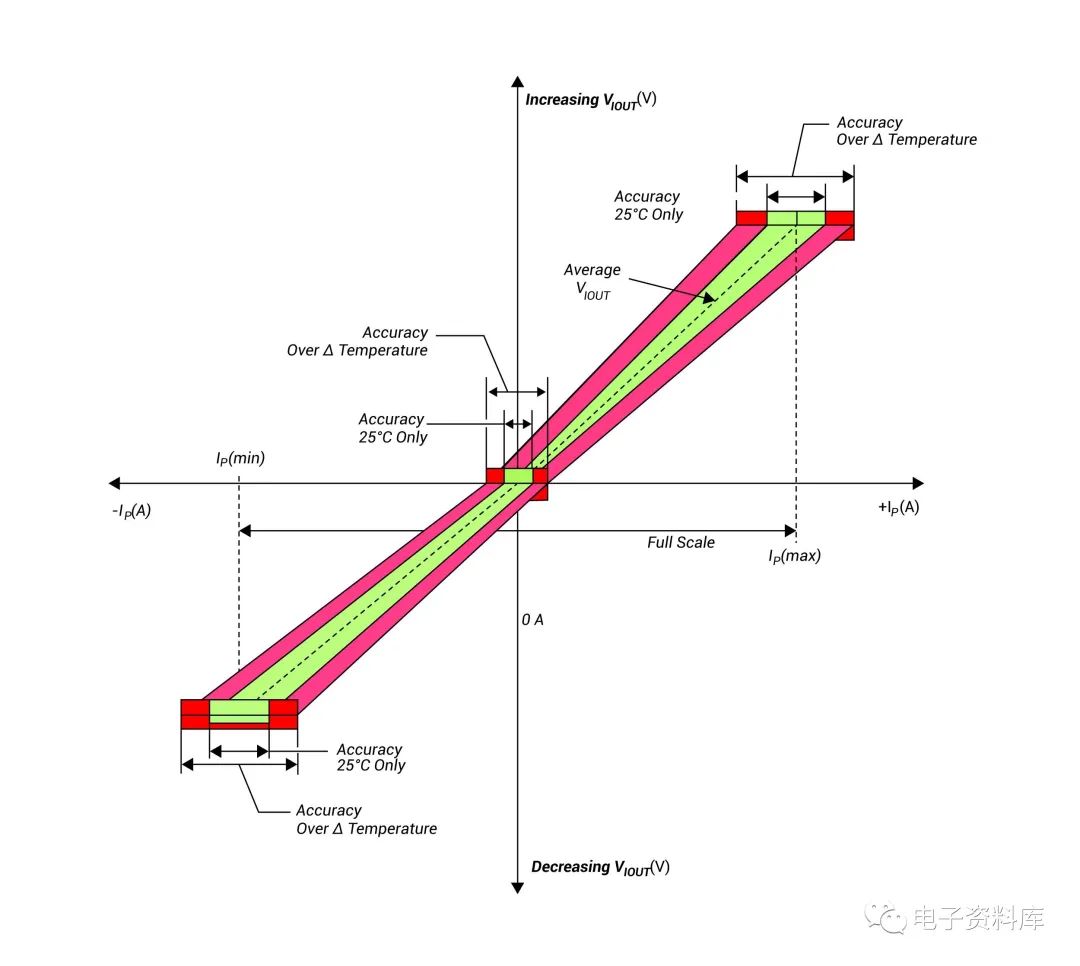

PSRR 會(huì)隨著頻率、溫度、電流、輸出電壓和電壓差等一些參數(shù)而波動(dòng)。PSRR 應(yīng)為負(fù)值,因?yàn)樗糜谟?jì)算拒絕。但是,該圖表將其顯示為正數(shù),因此圖表中的最高數(shù)字表示更高的噪聲抑制。

測(cè)量 LDO 的 PSRR

有多種測(cè)量 LDO 的 PSRR 的方法:

- 使用LC求和節(jié)點(diǎn)測(cè)量PSRR:

測(cè)量 LDO 的 PSRR 的基本方法如下圖所示。

在這種方法中,兩個(gè)電壓(直流和交流)加在一起并施加到 LDO 的輸入端。工作點(diǎn)偏置電壓為 VDC,VAC 為噪聲源。在上圖中,電容 C 用于防止 VAC 短路 VDC,電感 L 防止 VDC 短路噪聲源。

在低頻下測(cè)量 PSRR 由電感器 L 和電容器 C 創(chuàng)建的高通濾波器決定。該濾波器的 3dB 點(diǎn)由以下

公式?jīng)Q定:Fmin=12ΠLCFmin=12ΠLC

當(dāng)頻率低于 3dB 點(diǎn)時(shí),測(cè)量 PSRR 變得困難他們開始減弱。

- 使用加法放大器測(cè)量 PSRR

為了獲得改進(jìn)的 PSRR 測(cè)量,描述了另一種方法,其中使用高帶寬放大器作為求和節(jié)點(diǎn)來(lái)插入信號(hào),從而在 VAC 和 VDC 之間提供隔離。這種方法可以在下圖中看到:

在這種方法中,PSRR 是在無(wú)負(fù)載條件下測(cè)量的。

使用此方法時(shí),在測(cè)量 PSRR 時(shí)必須牢記以下因素。

- 輸入電容可能是高速放大器進(jìn)入不穩(wěn)定狀態(tài)的原因;在測(cè)量 PSRR 之前應(yīng)移除該電容。

- 為了減少電感效應(yīng),Vin 和 Vout 應(yīng)立即用示波器或網(wǎng)絡(luò)分析儀測(cè)量。

- 長(zhǎng)線會(huì)增加電感并影響結(jié)果。這就是為什么測(cè)試裝置不應(yīng)該有任何長(zhǎng)線。

- 選擇 AC 和 DC 輸入值時(shí)應(yīng)考慮以下條件:

? VAC(最大值)+ VDC < LDO 的 VABS(最大值)

? VDC – VAC > LDO 的 VUVLO

如果滿足以下條件,將獲得最佳結(jié)果:

? VDC–VAC > Vout + Vdo + 0.5

其中:

Vout 是 LDO 的輸出電壓

Vdo 是工作點(diǎn)的特定壓降電壓。

5. 放大器的結(jié)果將開始衰減施加到 LDO 的非常高頻率的 VAC 信號(hào)。

6. MOSFET輸出阻抗與漏極電流成反比,導(dǎo)致LDO開環(huán)輸出阻抗降低,負(fù)載電流增加,增益降低。

-

SoC設(shè)計(jì)

+關(guān)注

關(guān)注

1文章

151瀏覽量

19015 -

FET

+關(guān)注

關(guān)注

3文章

689瀏覽量

63766 -

電源抑制比

+關(guān)注

關(guān)注

0文章

76瀏覽量

13820 -

誤差放大器

+關(guān)注

關(guān)注

9文章

120瀏覽量

35291 -

低壓差穩(wěn)壓器

+關(guān)注

關(guān)注

0文章

359瀏覽量

21021

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

淺談LDO的噪聲與PSRR之間的差異

什么是LDO?淺析低壓差穩(wěn)壓器 (LDO) 中的噪聲及電源抑制比

為什么運(yùn)放和ADC的PSRR不能把LDO輸出的內(nèi)部噪聲抑制的干干凈凈呢?

為什么運(yùn)放和ADC的PSRR不能把LDO輸出的內(nèi)部噪聲抑制的干干凈凈呢?

LDO噪聲簡(jiǎn)介

什么是LDO噪聲?LDO噪聲是如何分類的?

一文介紹LDO噪聲及分類

LDO的PSRR該如何測(cè)量呢

LDO穩(wěn)壓器的PSRR和輸出噪聲在RF電路中的選擇

和電源噪聲說(shuō)「拜拜」!因?yàn)檫@顆具有超高PSRR的LDO

LDO噪聲到底是什么

LDO的噪聲與PSRR之間的差異

評(píng)論