作者:Stephen Evanczuk

對于希望在邊緣的推理處理器上實施人工智能 (AI)算法的設計人員來說,他們正不斷面臨著降低功耗并縮短開發時間的壓力,即使在處理需求不斷增加的情況下也是如此。現場可編程門陣列 (FPGA) 為實施邊緣 AI所需的神經網絡 (NN) 推理引擎提供了特別有效的速度和效率效率組合。然而,對于不熟悉 FPGA 的開發人員來說,傳統 FPGA的開發方法可能相當復雜,往往導致他們去選擇不太理想的解決方案。

本文將介紹來自 Microchip Technology 的一種比較簡單的方法。通過這種方法,開發人員可以使用 FPGA 和軟件開發套件 (SDK)

構建經過訓練的 NN,或者使用基于 FPGA 的視頻套件立即啟動智能嵌入式視覺應用開發,從而避開傳統的 FPGA 開發。

為什么要在邊緣使用 AI?

邊緣計算為物聯網 (IoT) 應用帶來了諸多好處,涵蓋了包括工業自動化、安全系統、智能家居等在內的多個領域。在以工廠車間為目標的工業物聯網 (IIoT)應用中,邊緣計算通過避免到云端應用的往返延遲,可以顯著縮短過程控制環路的響應時間。同樣,基于邊緣的安全系統或智能家居門鎖即使由于意外或人為原因與云端的連接斷開時,也能繼續正常工作。在很多情況下,在任何此類應用中使用邊緣計算時,都可以通過減少產品對云資源的依賴來幫助降低整體運營成本。隨著產品要求的提高,開發者可以依靠產品中內置的本地處理功能去幫助維持更穩定的運營開支,而不會面臨增加昂貴的云資源的意外需求。

對機器學習 (ML)

推理模型的快速接受和需求的增加,極大地提高了邊緣計算的重要性。對于開發人員來說,推理模型的本地處理能力有助于降低云端推理所需的響應延遲和云資源成本。對于用戶來說,使用本地推理模型會讓他們更加相信,其產品在偶爾與互聯網斷開或基于云的供應商產品發生變化時仍能正常運行。此外,在安全和隱私方面的擔憂會進一步推動對本地處理和推理的需求,以限制通過公共互聯網傳輸到云端的敏感信息數量。

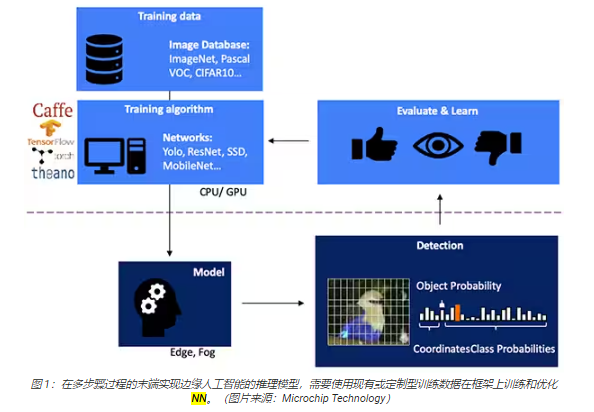

為基于視覺的對象檢測開發 NN 推理模型是一個多步驟過程。首先進行模型訓練,這一步通常在 TensorFlow 等 ML框架上使用公開的標記圖像或自定義的標記圖像進行訓練。由于處理需求,模型訓練通常使用云端或其他高性能計算平臺的圖形處理單元 (GPU)進行。訓練完成后,模型被轉換為能夠在邊緣或霧計算資源上運行的推理模型,并將推理結果以一組對象類概率的形式交付(圖 1)。

為什么推理模型存在計算方面的挑戰

與訓練過程中使用的模型相比,雖然 NN 推理模型的大小和復雜程度都有所降低,但還是需要大量計算,這對于通用處理器來說仍是一個挑戰。在其通用形式中,深層NN 模型由多層神經元集組成。在一個全連接網絡的每一層內,每個神經元 nij 都需要計算每個輸入與相關權重系數 wij 的乘積之和(圖 2)。

圖

2 中沒有顯示激活函數和類似函數帶來的額外計算要求。激活函數通過將負值映射為零,將大于 1 的值映射為 1來修改每個神經元的輸出。每個神經元 nij 的激活函數的輸出作為下一層i+1 的輸入,以此類推直至每一層。NN模型的輸出層最終產生一個輸出向量,代表原始輸入向量(或矩陣)對應于監督學習過程中使用的某一個類(或標簽)的概率。

相比上圖所示具有代表性的通用NN 架構,有效的 NN 模型是由大得多、復雜得多的架構來構建的。例如,用于圖像對象檢測的典型卷積 NN (CNN)以分段方式應用這些原理,掃描輸入圖像寬度、高度和顏色深度,從而生成一系列最終會產生輸出預測向量的特征圖(圖 3)。

用 FPGA 加速 NN 數學

雖然在邊緣執行推理模型的方案不斷涌現,但很少有方案能夠提供實際的邊緣高速推理所需的最佳靈活性、性能和能效組合。在現有的邊緣 AI 替代品中,FPGA特別有效,因為它們可執行基于硬件的高性能計算密集型工作,同時功耗相對較低。

盡管 FPGA 優勢突出,但由于傳統的開發流程有時會讓沒有豐富 FPGA 經驗的開發人員望而生畏,舍棄 FPGA。為了有效實施通過 NN 框架生成的 NN模型的 FPGA,開發人員需要了解將模型轉換為寄存器傳輸語言 (RTL)、設計綜合和最終審定之間的細微差別,并需要制定具體的設計階段路線,從而做到優化實施(圖 4)。

憑借其 PolarFire FPGA、專用軟件和相關知識產權 (IP),Microchip Technology 提供了一種解決方案,讓沒有 FPGA經驗的開發人員也能廣泛地使用高性能、低功耗邊緣推理。

PolarFire FPGA 采用先進的非易失性工藝技術制造,旨在最大限度地提高靈活性和性能,同時將功耗降至最低。除了用于通信和輸入/輸出 (I/O)的大量高速接口外,它們還具有深厚的 FPGA 結構,能夠使用軟 IP 內核支持高級功能,具體包括 RISC-V 處理器、高級內存控制器和其他標準接口子系統(圖 5)。

PolarFire FPGA 架構提供了一套廣泛的邏輯元件和專用功能塊,通過 PolarFire FPGA 系列的不同器件獲得各種不同的容量支持,具體包括MPF100T、MPF200T、MPF300T 和 MPF500T 系列(表 1)。

在特別令人關注的推理加速功能中,PolarFire 架構包括一個專用數學塊,提供一個具有預加法器的 18 位 × 18 位有符號乘法累加函數

(MAC)。內置的點積模式使用一個數學塊來執行兩個 8 位乘法運算,通過利用模型量化對精度的影響可以忽略這一優勢,提供了一種可提高容量的機制。

除了能加快數學運算外,PolarFire 架構還有助于緩解在通用架構上實施推理模型時遇到的存儲器擁堵問題,例如用來保存在 NN算法執行過程中創建的中間結果的小型分布式存儲器。另外,NN 模型的權重值和偏置值可以存儲在一個系數為 16 深 x 18 位的只讀存儲器 (ROM)中,這種存儲器通過位于數學塊附近的邏輯元件構建。

結合其他 PolarFire FPGA 結構特性,數學塊為 Microchip Technology 更高級別的 CoreVectorBlox IP奠定了基礎。這將作為一個靈活的 NN 引擎,能夠執行不同類型的 NN。除了一組控制寄存器外,CoreVectorBlox IP 還包括三個主要功能塊:

微控制器:一個簡單的 RISC-V 軟處理器,可從外部存儲器讀取 Microchip 固件二進制大對象 (BLOB) 和用戶特定型 NN BLOB文件。通過執行固件 BLOB 的指令來控制 CoreVectorBlox 的整體運算。

矩陣處理器 (MXP):這是一種由 8 個 32 位算術邏輯單元 (ALU)組成的軟處理器,旨在使用逐元素張量運算對數據向量執行并行運算,包括加法、減法、xor、移位、mul、dotprod 等,并根據需要使用 8 位、16 位和 32位混合精度。

CNN 加速器:使用通過數學塊實現的二維 MAC 函數陣列來加速 MXP 運算,運算精度為 8 位。

一個完整的 NN 處理系統將包括 CoreVectorBlox IP 塊、存儲器、存儲器控制器和主機處理器,如微軟 RISC-V(Mi-V)軟件處理器內核(圖 6)。

在視頻系統實施過程中,主機處理器將從系統存儲器加載固件和網絡 BLOB,并將其復制到雙數據速率 (DDR) 隨機存取存儲器 (RAM) 中供CoreVectorBlox 塊使用。當視頻幀到達時,主機處理器將其寫入 DDR RAM,并向 CoreVectorBlox塊發出信號,以開始圖像處理。在主機運行網絡 BLOB 中定義的推理模型后,CoreVectorBlox 塊將結果(包括圖像分類)寫回 DDR RAM

中,供目標應用程序使用。

開發流程簡化了 NN FPGA 實施

Microchip 使開發人員避開了在 PolarFire FPGA 上實施 NN 推理模型的復雜性。NN 模型開發人員無需處理傳統 FPGA流程的細節,而是像往常一樣使用其 NN 框架,并將生成的模型加載到 Microchip Technology 的 VectorBlox 加速器軟件開發工具包(SDK) 中。SDK 生成所需的一組文件,包括正常 FPGA 開發流程所需的文件和上文提到的固件和網絡 BLOB 文件(圖 7)。

由于 VectorBlox Accelerator SDK 流程將 NN 設計置于在 FPGA 中實施的 NN 引擎之上,因此不同的 NN 可以在同一FPGA 設計上運行,而無需重復 FPGA 設計綜合流程。開發者為生成的系統創建 C/C++代碼,并能在系統內快速切換模型,或使用時間切片同時運行模型。

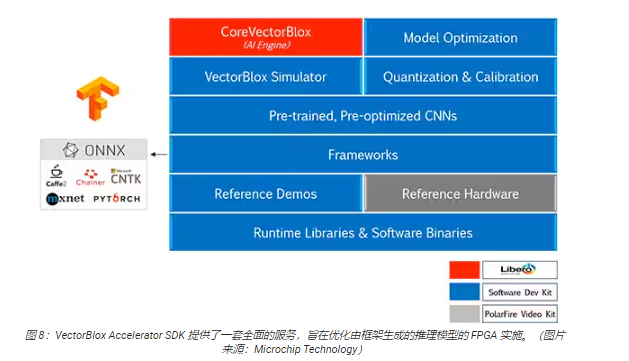

VectorBlox Accelerator SDK 將 Microchip Technology Libero FPGA 設計套件與 NN推理模型開發的全套功能融為一體。除了模型優化、量化和校準服務之外,SDK 還提供了一個 NN 仿真器,能讓開發人員在 FPGA 硬件實施中使用其模型之前用相同的BLOB 文件進行模型評估(圖 8)。

VectorBlox Accelerator SDK 支持采用開放神經網絡交換 (ONNX) 格式的模型,以及來自包括TensorFlow、Caffe、Chainer、PyTorch 和 MXNET 在內的多種框架的模型。可支持的 CNN 架構包括MNIST、MobileNet 版、ResNet-50、Tiny Yolo V2 和 Tiny Yolo V3。Microchip正在努力擴大支持范圍,將大多數網絡納入預訓練模型的開源式 OpenVINO 工具包 開放模型動物園 中,包括Yolo V3、Yolo V4、RetinaNet和 SSD-MobileNet 等。

視頻套件演示 FPGA 推理

為幫助開發人員快速啟動智能嵌入式視覺應用開發,Microchip Technology 提供了一個全面的樣例應用,設計用于在該公司的

MPF300-VIDEO-KIT PolarFire FPGA 視頻和成像套件和參考設計上運行。

基于 Microchip MPF300T PolarFire FPGA,該套件電路板結合了雙攝像頭傳感器、雙數據速率 4 (DDR4)RAM、閃存、電源管理和各種接口(圖 9)。

該套件附帶一個完整的 Libero 設計項目,用于生成固件和網絡 BLOB 文件。將 BLOB 文件編程到板載閃存中后,開發人員點擊 Libero

中的運行按鈕即可開始演示,處理來自攝像頭傳感器的視頻圖像,并將推理結果在顯示屏上顯示(圖 10)。

對于每個輸入視頻幀,基于 FPGA 的系統會執行以下步驟(步驟編號與圖 10 相關)。

從相機中加載一幀畫面

將幀存儲在 RAM 中

讀取 RAM 中的幀

將原始圖像轉換為 RGB、平面化 RGB 并將結果存儲在 RAM 中。

Mi-V soft RISC-V 處理器啟動 CoreVectorBlo x引擎,從 RAM 中檢索圖像,進行推理并將分類概率結果存儲回 RAM中。

Mi-V 使用結果創建一個包含邊界框、分類結果和其他元數據的疊加幀,并將該框架存儲在 RAM 中。

原始幀與疊加幀混合并寫入 HDMI 顯示屏。

該演示支持 Tiny Yolo V3 和 MobileNet V2模型加速,但需要開發人員改動少許代碼,將模型名稱和元數據添加到包含兩個默認模型的現有列表中,即可使用上述方法運行其他 SDK 支持的模型。

結論

NN 模型等人工智能算法通常會施加計算密集型工作負載,這需要比通用處理器更強大的計算資源。雖然 FPGA能夠很好地滿足推理模型執行的性能和低功耗要求,但傳統的 FPGA 開發方法可能會很復雜,往往導致開發人員轉向不太理想的解決方案。

如圖所示,使用 Microchip Technology 的專用 IP 和軟件,沒有 FPGA經驗的開發人員也能實施基于推理的設計,更好地滿足性能、功耗以及設計進度要求。

-

FPGA

+關注

關注

1641文章

21912瀏覽量

611741 -

嵌入式

+關注

關注

5124文章

19432瀏覽量

312896 -

物聯網

+關注

關注

2921文章

45664瀏覽量

384944 -

AI

+關注

關注

87文章

33495瀏覽量

274068

發布評論請先 登錄

相關推薦

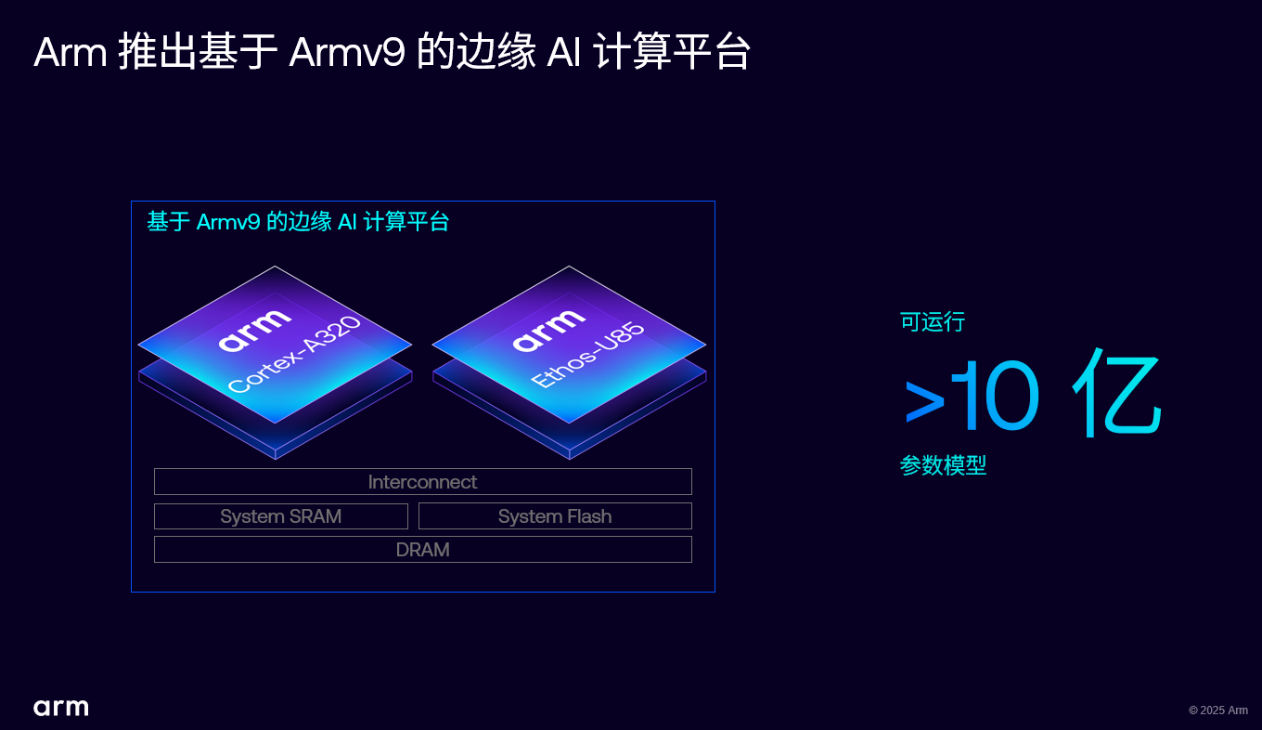

Arm 推出 Armv9 邊緣 AI 計算平臺,以超高能效與先進 AI 能力賦能物聯網革新

AI賦能邊緣網關:開啟智能時代的新藍海

當我問DeepSeek AI爆發時代的FPGA是否重要?答案是......

FPGA+AI王炸組合如何重塑未來世界:看看DeepSeek東方神秘力量如何預測......

FPGA構建高性能DSP

高能效電源的設計指南

硬件幫助將AI移動到邊緣

如何利用FPGA開發高性能網絡安全處理平臺?

EdgeBoard FZ5 邊緣AI計算盒及計算卡

嵌入式邊緣AI應用開發指南

FPGA構建高性能DSP

利用安森美半導體IGBT實現高能效的高性能開關應用

評論