消除反射現象的方法一般有:布線時的拓撲法和相應的端接技術。

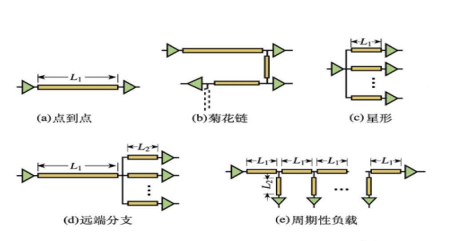

常用布線時的拓撲結構有:點到點、菊花鏈、星形、分支和周期性負載等結構。

點到點(Point-to-point):

點到點的拓撲結構比較簡單,只要在發送端或接收端進行適當的阻匹配。

菊花鏈(Daisy chain):

當網絡(net) 的整個走線長度延遲小于信號的上升或下降時間時,用菊花鏈拓撲結構會比較好,這時網絡上的負載都可以看作為容性負載。菊花鏈同時也限了信號的速率,只能工作在低速電路中 。

星形(Star):

使用星形的拓撲結構時, 對每個分支(stub)都進行均衡設計,要求每個分支的收端負載一致, 并選擇適當的匹配方式 。

遠端分支(Far-end cluster):

跟星形類似,只不過分支是靠近接收端 。在這種拓撲結構中,也要限制遠端 stub 的長度, 使 stub上的傳輸延時小于信號上升沿, 這樣每個接收端都可以被看作為一個簡單的容性負載。

周期性負載(Periodic loading) :

周期性負載的拓撲結構同樣要求每段 stub 的長度足夠小,使 stub 上的傳輸延時小于信號上升沿。這種主干傳輸線和所有的 stub 段組合起來的結構可以看作為一段新的傳輸線,其特征阻抗要比原來主干傳輸線的特征阻抗小,傳輸速率也比原來的低,因此在進行阻抗匹配時要注意 。

傳輸線上的反射會對數字系統性能有重要的負面影響 。為了最小化反射的負面影響,除從拓撲結構上消除相應的影響外,還必須有相應控制它們的方法 。基本上有三種方法減低這些反射的負面影響 。第一種方法就是降低系統的頻率或增大信號的上升沿時間, 以使傳輸線上的反射將在另一個信號驅動到線上之前達到穩態。

然而通常這是不可能的,對于高速系統,增大信號上升沿時間,將影響系統的性能。第二種方法是縮短 PCB 走線長度以使反射在短時間內達到穩態。通常這是不實用的,因為通常芯片功能的強大,管腳的增多,縮短布線必然導致PCB板層數的做多,這大大增加了成本 。

另外,在一些情況下縮短走線在物理實現上有時也是不可能的。第三種方法就是給傳輸線兩端終接一個等于特征阻抗的阻抗,并消除反射,即是所謂的高速電路設計的端接技術。端接技術分為單端斷接技術和負載端接技術。

1 單端端接技術

傳輸線的長度符合下式的條件應使用端接技術:

式中 , L 為傳輸線線長,tr 為源端信號的上升時間,tp 為傳輸線上每單位長度的帶載傳輸延遲。即當 tr小于 2TD時(其中 TD 為傳輸線的傳輸延遲, L*tp=TD),源端電平變換發生在傳輸線的接收端反射回源端的反射波到達源端之前,這時需要使用端接匹配技術,否則會在傳輸線上引起振鈴 。

傳輸線的端接原則:如果負載反射系數或源反射系數二者任一為零,反射將被消除 。通常采用兩種策略 (1)使負載阻抗與傳輸線阻抗匹配,即并行端接;(2)使源阻抗與傳輸線阻抗匹配,即串行端接 。

從系統設計的角度,應首選策略1,因其是在負載端消除反射,即 ρL=0,因而消除一次反射,這樣可以減小噪聲、電磁干擾(EMI)及射頻干擾(RFI);而策略 2 則是在源端消除由負載端反射回來的信號,即使 ρs=0和ρL=1(負載端不加任何匹配),只是消除二次反射,在發生電平變換時,源端會出現持續時間為 2TD的半波波形,不過由于策略 2 實現簡單方便,在許多應用中也被廣泛采用 。兩種端接策略各有其優缺點,以下就簡要介紹這兩類主要的端接方案 。

1.1 并行端接

并行端接主要是在盡量靠近負載端的位置加上拉和/或下拉阻抗以實現終端的阻抗匹, 根據不同的應用環境,并行端接又可分為以下幾種類型 :

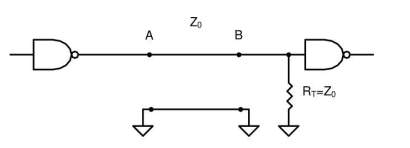

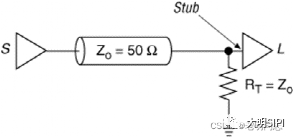

(1) 簡單的并行端接

這種端接方式是簡單地在負載端加入一下拉到地的電阻 RT(RT=Z0)來實現匹配, 如圖所示。采用此端接的條件是驅動端必須能夠提供輸出高電平時的驅動電流以保證通過端

接電阻的高電平電壓滿足門限電壓要求。在輸出為高電平狀態時,這種并行端接電路消耗的流過大,對于50Ω的端接負載,維持 TTL 高電平消耗電流高達48mA,因此一般器件很難靠地支持這種端接電路。

(2) 戴維寧并行端接

戴維寧(Thevenin)端接即分壓器型端接, 如圖所示。

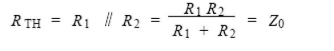

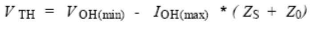

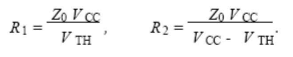

它采用上拉電阻R1和下拉電阻R2構成端接電阻,通過R1和R2吸收反射。R1和R2阻的選取由下面的條件決定 。R1的最大值由可接受的信號的最大上升時間(是 RC 充放電時常數的函數)決定,R1的最小值由驅動源的吸電流數值決定。R2的選擇應滿足當傳輸線斷開時電路邏輯高電平的要求。戴維寧等效阻抗可表示為:

戴維南電壓VTH為:

VTH的選擇必須確保驅動器的輸出高電平IOH和低電平的lOL電流在驅動器的性能指標圍以內,其值可按下式確定

R1的作用是幫助驅動器更加容易到達邏輯高狀態,這就需通過從Vcc向負載注入電流來實現。R2的作用是幫助驅動器更加容易到達邏輯低狀態,這通過R2向地釋放電流來實現 。恰當地選取R1和R2的值可以加強驅動器的扇出能力,并且淡化由于信號占空比不一致而導致的功耗的改變。

戴維南終端匹配技術的優點在于,在這種匹配方式下,終端匹配電阻同時還作為上拉電和下拉電阻來使用,因而提高了系統的噪聲容限,降低了對源端器件驅動能力的要求 。這種方案能夠很好地抑制過沖 。

戴維南終端匹配的缺點就是無論邏輯狀態是高還是低,在Vcc到地之間都會有一個常量直流電流存在,因而會導致終端匹配電阻中有靜態的直流功耗,信號負載為電容時,相對于有匹配的信號線而言,戴維南終端匹配技術同樣會改善信號的質量,使得信號的擺動縮小 。

電壓(在三態總線上的戴維寧電壓)接近轉換門限電壓, 這在CMOS器件中會產生更大的功,這是由于PMOS和NMOS都是可導的,在Vcc和地之間就有電流路徑 。另外, 與未端接的情況相比,戴維寧端接減小了接容性負載時信號的斜率,容性負載和電阻增加了 RC時間常數,致了驅動器輸出電壓的上升 。

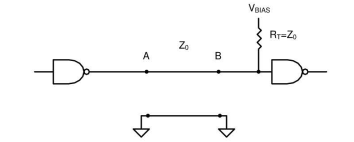

(3) 主動并行端接

在此端接策略中 ,端接電阻RT(RT=Z0)將負載端信號拉至一偏移電壓Vbias,如圖示Vbias的選擇依據是使輸出驅動源能夠對高低電平信號有汲取電流能力。這種端接方式需要一個具有吸、灌電流能力的獨立的電壓源來滿足輸出電壓的跳變速度的要求 。

在此端接方案中,如偏移電壓Vbias為正電壓,輸入為邏輯低電平時有 DC 直流功率損耗,如偏移電壓Vbisd為負電壓,則輸入為邏輯高電平時有直流功率損耗 。

(4)并行 AC 端接

如圖所示,并行 AC 端接使用電阻和電容網絡 (串聯 RC)作為端接阻抗。

端接電阻R要小于等于傳輸線阻抗Z0,電容 C 必須大于100pF,推薦使用0.1uF 的多層瓷電容。電容有阻低頻通高頻的作用, 因此電阻 R 不是驅動源的直流負載, 故這種端接方無任何直流功耗。

可見電容C 的選擇很復雜.電容值太小會導致RC 時間常數過小,這樣一來該RC 電路就似于一個尖銳信號沿發生器,從而引入信號的過沖與下沖, 一般電容值需大于 100pF,另一面, 較大的電容值會帶來更大的功率消耗,通常情況下,要確保RC 時間常數大于該傳輸線負載延時的兩倍,即

其中:CD為接收器的分布電容, C0為PCB 傳輸線的內在電容。

理想的電容值將隨著傳輸線阻抗,邊沿速率,預期的信號質量的變化而變化 。這個值不是最關鍵的,但是測試表明,對于 FCT 邏輯,100pF的電容值能夠得到很好的折衷,將電容值增加到200PF會改善信號的質量,但是卻以功率損耗為代價。

把電容值減小到 47PF,降低功率損耗,但是信號的質量會變差。值低于 47PF 會對濾波有非常高的頻率響應,對傳輸的端接是無效的。值高于 200PF,會增加功率損耗而不會有附加的信號質量的改善 。

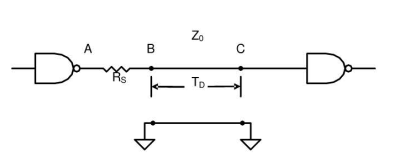

2 串行短接

串行端接是通過在盡量靠近源端的位置串行插入一個電阻Rs (典型10 Ω到 75Ω)到傳輸線中來實現的, 如圖所示。串行端接是匹配信號源的阻抗,所插入的串行電阻阻值加上驅動源的輸出阻抗應大于等于傳輸線阻抗(輕微過阻尼)。即:

這種策略通過使源端反射系數為零從而抑制從負載反射回來的信號(負載端輸入高阻,不吸收能量)再從源端反射回負載端 。

串行端接的優點在于:每條線只需要一個端接電阻,無需與電源相連接,消耗功率小 。當驅動高容性負載時可提供限流作用,這種限流作用可以幫助減小地彈噪聲 。而且相對于它的電阻類型終端匹配技術來說,串聯終端匹配技術中匹配電阻的功耗是最小的,而且串聯終端匹配技術不會給驅動器增加任何額外的直流負載,也不會在信號線與地之間引入額外阻抗。

串行端接的缺點在于 :當信號邏輯轉換時, 由于Rs的分壓作用 , 在源端會出現半波幅度的信號,這種半波幅度的信號沿傳輸線傳播至負載端,又從負載端反射回源端,持續時間為2TD ( TD為信號源端到終端的傳輸延遲),這意味著沿傳輸線不能加入其它的信號輸入端,因為在上述2TD時間內會出現不正確的邏輯態。

并且由于在信號通路上加接了元件,增加了 RC時間常數從而減緩了負載端信號的上升時間,因而不適合用于高頻信號通路(如高速時鐘等)。

另外,采用這種匹配技術時,很難將串聯匹配電阻調整到一個非常合適的值,因為許多驅動器都是非線性的,如TTL 器件,其輸出阻抗隨著器件邏輯狀態的變化而變化, 所以串聯匹配電阻只能選擇二個適中的值。

注:對于短的傳輸線,當最小數字脈沖寬度長于傳輸線的時間延遲( TD)時,源終端是合乎要求的,因為它消除了驅動器電流部分并聯接地的要求。對于長的傳輸線,當數字脈沖寬度小于傳輸線延遲時間(TD)時, 負載終端是較好的。因為負載端的反射將反射回源頭端,并干擾沿線傳播的信號,反射必須在負載端消除。

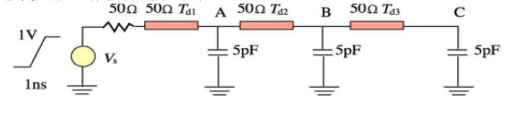

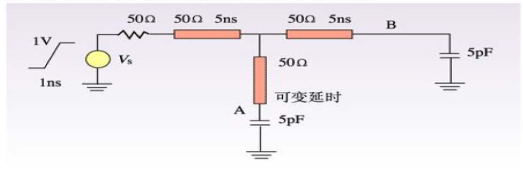

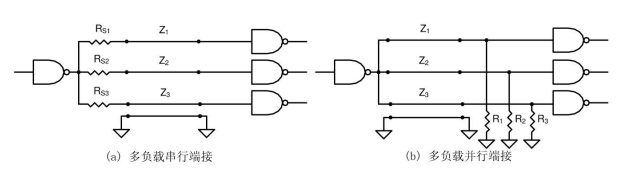

3 多負載端接技術

在實際電路中常常會遇到單一驅動源驅動多個負載的情況,這時需要根據負載情況及電的布線拓撲結構來確定端接方式和使用端接的數量。一般情況下可以考慮以下兩種方案。

如果多個負載之間的距離較近,可通過一條傳輸線與驅動端連接,負載都位于這條傳輸的終端,這時只需要二個端接電路。如采用串行端接,則在傳輸線源端加入一串行電阻即可,圖a所示。

如采用并行端接(以簡單并行端接為例),則端接應置于離源端距離遠的負載處,同時,線網的拓撲結構應優先采用菊花鏈的連接方式,如圖b所示 。

如果多個負載之間的距離較遠,需要通過多條傳輸線與驅動端連接,這時每個負載都需一個端接電路。如采用串行端接,則在傳輸線源端每條傳輸線上均加入一串行 電阻,如圖a所示。如采用并行端接(以簡單并行端接為例),則應在每一負載處都進行端接,如圖b所示 。

在采用匹配的時候,但要確保匹配元件盡量靠近源端或負載端,這樣可以減少誘導電感,匹配更為有效。

4 不同工藝器件的端接策略

阻抗匹配與端接技術方案隨著互聯長度和電路中邏輯器件的家族在不同也會有所不同,只有針對具體情況, 使用正確適當的端接方法才能有效地減小信號反射 。

一般來說,對于一個CMOS工藝的驅動源,其輸出阻抗值較穩定且接近傳輸線的阻抗值,因此對于CMOS器件使用串行端接技術就會獲得較好的效果 。而TTL工藝的驅動源在輸出邏輯高電平和低電平時其輸出阻抗有所不同,這時,使用并行戴維寧端接方案則是一種較好的策略 。

ECL 器件一般都具有很低的輸出阻抗,因此,在ECL電路的接收端使用一下拉端接電阻(下拉電平需要根據實際情況選取)來吸收能量則是ECL電路的通用端接技術。

當然, 上述方法也不是絕對的,具體電路上的差別、 網絡拓撲結構的選取、 接收端的負數等都是可以影響端接策略的因素, 因此在高速電路中實施電路的端接方案時 , 需要根據體情況通過分析仿真來選取合適的端接方案以獲得最佳的端接效果 。

-

驅動器

+關注

關注

53文章

8267瀏覽量

146796 -

信號完整性

+關注

關注

68文章

1415瀏覽量

95571 -

TTL電平

+關注

關注

1文章

116瀏覽量

12046 -

PCB走線

+關注

關注

3文章

134瀏覽量

13962 -

EMI設計

+關注

關注

0文章

44瀏覽量

10504

發布評論請先 登錄

相關推薦

信號完整性學習筆記之常用端接技術

信號完整性學習筆記之常用端接技術

評論