共源共柵Cascode以及級聯(lián)Cascade的優(yōu)缺點是什么?

共源共柵Cascode以及級聯(lián)Cascade是常用的放大電路架構,它們在不同應用場合中具有不同的優(yōu)缺點。在本文中,我們將就這些架構列舉其優(yōu)點和缺點,并對其性能進行分析。

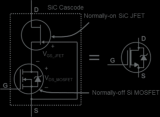

一、共源共柵Cascode

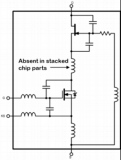

共源共柵Cascode電路是一個雙級放大電路,由一個源連雙極晶體管(MOSFET)和一個柵連MOSFET組成。該電路可以提高放大電路的增益和線性度,減小MOSFET對電路帶來的影響和節(jié)省電源。共源共柵Cascode架構的優(yōu)點有以下幾個:

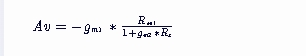

1.較高的增益:由于共源共柵Cascode可以增加電路的工作點,因此可以有效提高其增益。其中,共源極的電壓被提高,當電流正向帶通時,真空管會nose up(即增加電流)。而通過共柵極的電壓使結果更不會被擊穿。

2.較小的電容:共源共柵Cascode的結構比傳統(tǒng)電路更加平穩(wěn),這意味著電壓變化相對更小,從而減小了由于消耗電容器帶來的噪聲。因此,CASCODE電路內部電容體積變小,減少了由電容產生的干擾信號。

3.阻止電荷注入:在電路中,MOSFET會受到電路中其他元件反向電流的影響,導致電荷注入到MOSFET晶體管管的門源電容。但是,共源共柵Cascode架構中,在電路中的MOSFET門源兩端之間增加了電容,以阻止電荷注入進入MOSFET晶體管管的門源電容,從而有效提高了電路的穩(wěn)定性。

4.減小功耗:由于共源共柵Cascode電路具有雙級放大的特點,因此可以在不影響增益的情況下減少對電源的消耗。這是由電路結構本身所決定的。在電路不需要額外的工作時,將其完全關閉是易于實現(xiàn)的。

但是,共源共柵Cascode也存在一些缺點:

1.復雜的基準電路:由于共源共柵Cascode電路本身較為復雜,在實現(xiàn)基準電路時,需要對其進行調節(jié),以使其工作點處于合適的狀態(tài)。

2.高導通電阻:共源共柵Cascode電路通常具有較高的導通電阻,因此可能需要額外的電源來推動電路,以達到預期的性能。

3.較高的雜散噪聲:由于共源共柵Cascode電路需要使用較高的放大電路,所以在大幅放大時,可能會出現(xiàn)一定的雜散噪聲。這是由于電路的感受器不足所造成的。

二、級聯(lián)Cascade

級聯(lián)Cascade也是常用的放大電路架構。與共源共柵Cascode架構不同,級聯(lián)Cascade架構由多個單級放大電路組成,每個單級放大電路都獨立放大電路信號。級聯(lián)Cascade架構的優(yōu)點有以下幾個:

1.較高的帶寬:級聯(lián)Cascade電路是由多個單級放大器電路串聯(lián)組成的,其輸出加入到下一個單級放大電路的輸入中。由于每個單級放大器電路的增益不太一樣,可以大幅度擴展電路的帶寬。

2.較高的增益:由于級聯(lián)Cascade電路具有多級放大器電路的特點,因此可以在不損失增益的情況下增加電路的線性度。由于多個單級放大器電路的組合,級聯(lián)Cascade電路能夠放大的信號的振幅可以達到很高。

3.較低的雜散噪聲:級聯(lián)Cascade電路可以大幅度擴展電路的帶寬,因此在實現(xiàn)電路的同時降低了電路的雜散噪聲。這是由于電路需要使用更少的電容和電感來實現(xiàn)同樣的性能。

但是,級聯(lián)Cascade電路也存在一些缺點:

1.較復雜的設計:在實現(xiàn)級聯(lián)Cascade電路時,需要特別注意電路的每個分支,以便正確配置電路的增益與帶寬。對于不同分支放大器之間的互相影響需要進行調整。

2.高功耗:由于級聯(lián)Cascade電路是由多個單級放大器電路組成的,因此其功耗可能會高于單個放大器電路。此外,由于電路包含多個放大級別,因此其實現(xiàn)設計中對電路的功率需求可能會比較嚴格。

3.較大的面積:由于級聯(lián)Cascade電路是由多個單級放大器電路組成的,因此其面積通常比單個放大器電路大得多。此外,多個單放大器電路需要緊密排列起來,以便在電路實現(xiàn)設計中獲得最大的性能。

綜上所述,共源共柵Cascode和級聯(lián)Cascade是常用的放大電路架構。在不同的應用場合中,選擇不同的經(jīng)典電路架構是很重要的。在應用中,我們需要根據(jù)電路結構和組件特性選擇合適的電路結構和組件。在不斷實踐和總結中,提高電路的設計能力和效果。

-

電容器

+關注

關注

64文章

6479瀏覽量

101383 -

MOSFET

+關注

關注

148文章

7816瀏覽量

217216 -

晶體管

+關注

關注

77文章

9907瀏覽量

140143

發(fā)布評論請先 登錄

相關推薦

安森美SiC cascode JFET并聯(lián)設計的挑戰(zhàn)

安森美SiC Cascode JFET的背景知識和并聯(lián)設計

Nexperia共源共柵氮化鎵(GaN)場效應晶體管的高級SPICE模型

評論