1、引言

本應(yīng)用筆記為系統(tǒng)開(kāi)發(fā)者概述了開(kāi)發(fā)板特性的硬件實(shí)現(xiàn)。開(kāi)發(fā)板特性為供電電源、時(shí)鐘管理、復(fù)位控制、自舉模式設(shè)置和調(diào)試管理。

本文檔詳細(xì)介紹了如何使用 STM32U575xx 和 STM32U585xx 微控制器(也稱為STM32U575/585)。其中介紹了使用這些 MCU開(kāi)發(fā)應(yīng)用程序所需的最少硬件資源。

本文還包括了詳細(xì)的參考設(shè)計(jì)原理圖,說(shuō)明了其主元件、接口和模式。本文檔適用于基于 Arm?的 STM32U575/585 微控制器。

2、電源管理

2.1 電源

STM32U575/585 器件要求 1.71 至 3.6 V 的工作電壓電源(VDD)。

下面列出的獨(dú)立電源可用于特定外設(shè):

? VDD = 1.71 V 至 3.6 V

VDD 是為 I/O、內(nèi)部穩(wěn)壓器和系統(tǒng)模擬信號(hào)(如復(fù)位、電源管理和內(nèi)部時(shí)鐘)供電的外部電源。VDD 通過(guò)VDD 引腳從外部提供。

? VDDA = 1.58 V (COMPs) / 1.6 V (DACs/OPAMPs) / 1.62 V (ADCs) / 1.8 V (VREFBUF) 至 3.6 V

VDDA 是為 A/D 轉(zhuǎn)換器、D/A 轉(zhuǎn)換器、電壓參考緩沖器、運(yùn)算放大器和比較器供電的外部模擬電源。VDDA 電壓電平獨(dú)立于 VDD 電壓。不使用這些外設(shè)時(shí),VDDA 引腳必須優(yōu)先連接至 VDD 電壓電源。

提示 如果 VDDA 引腳保持為高阻抗或連接至 VSS,則可施加到 I/O(具有"_a" I/O 結(jié)構(gòu))上的最大輸入電壓將降低(參見(jiàn)器件數(shù)據(jù)手冊(cè)以了解更多詳細(xì)信息)。

? VDDSMPS = 1.71 V 至 3.6 V

VDDSMPS 是為 SMPS 降壓轉(zhuǎn)換器供電的外部電源。它通過(guò) VDDSMPS 引腳從外部提供,且必須連接到與VDD 引腳相同的電源。

? VLXSMPS

VLXSMPS 引腳是開(kāi)關(guān) SMPS 降壓轉(zhuǎn)換器輸出。

? VDD11

VDD11 是通過(guò)內(nèi)部 SMPS 降壓轉(zhuǎn)換器 VLXSMPS 引腳提供的數(shù)字內(nèi)核電源。僅出現(xiàn)在具有內(nèi)部 SMPS 的封裝上的兩個(gè) VDD11 引腳連接至總量為 4.7 μF(典型值)的外部電容。此外,每個(gè) VDD11 引腳需要一個(gè) 100 nF陶瓷電容。

? VCAP

VCAP 是來(lái)自內(nèi)部 LDO 穩(wěn)壓器的數(shù)字內(nèi)核電源。VCAP 引腳(一個(gè)或兩個(gè))僅出現(xiàn)在只具有 LDO(無(wú)SMPS)的封裝上,需要連接至總量為 4.7 μF(典型值)的外部電容。此外,每個(gè) VCAP 引腳需要一個(gè) 100nF 陶瓷電容。

提示 – 如果有兩個(gè) VCAP 引腳(UFBGA169 封裝),則每個(gè)引腳必須連接至 2.2 μF 電容(總量約為 4.4 μF)(最大 4.7 μF)。每個(gè) VCAP 還需要一個(gè) 100 nF 陶瓷電容。

– SMPS 電源引腳(VLXSMPS、VDD11、VDDSMPS、VSSSMPS)僅在具有 SMPS 的封裝上可用。在此類封裝中,STM32U575/585 器件并聯(lián)嵌入了兩個(gè)穩(wěn)壓器(一個(gè) LDO 和一個(gè) SMPS),以便為數(shù)字外設(shè)提供VCORE 電源。VDD11 引腳上需要總 4.7 μF 的外部電容和 2.2 μH 線圈。此外,每個(gè) VDD11 引腳需要一個(gè)100 nF 陶瓷電容。

– Flash 由 VCORE 和 VDD 供電。

? VDDUSB = 3.0 V 至 3.6 V

VDDUSB 為外部獨(dú)立電源,為 USB 收發(fā)器供電。VDDUSB 電壓電平獨(dú)立于 VDD 電壓。不使用 USB 時(shí),VDDUSB 引腳必須優(yōu)先連接至 VDD 電壓電源。

提示如果 VDDUSB 引腳保持為高阻抗或連接至 VSS,則可施加到 I/O(具有"_u" I/O 結(jié)構(gòu))上的最大輸入電壓將降低(參見(jiàn)器件數(shù)據(jù)手冊(cè)以了解更多詳細(xì)信息)。

? VDDIO2 = 1.08 V 至 3.6 V

VDDIO2 是為 14 個(gè) I/O (port G[15:2])供電的外部電源。VDDIO2 電壓級(jí)別與 VDD 電壓無(wú)關(guān),不使用 PG[15:2]時(shí),最好連接到 VDD。

提示 在小封裝上,VDDA、VDDIO2 或 VDDUSB 獨(dú)立電源可能不作為專用引腳出現(xiàn),且內(nèi)部連接至 VDD 引腳。如果產(chǎn)品上不支持某功能,則該功能也不會(huì)出現(xiàn)。

? VBAT = 1.65 V 至 3.6 V(保證功能降至 VBOR_VBAT 最小值,參見(jiàn)產(chǎn)品數(shù)據(jù)手冊(cè))

當(dāng) VDD 掉電時(shí)(通過(guò)電源開(kāi)關(guān)),VBAT 為 RTC、TAMP、外部時(shí)鐘 32 kHz 振蕩器、備份寄存器和可選備份SRAM 提供電源。

? VREF- 和 VREF+

VREF+ 為 ADC 和 DAC 的輸入?yún)⒖茧妷骸J鼓軙r(shí),它還是內(nèi)部電壓參考緩沖器(VREFBUF)的輸出。當(dāng)ADC 和 DAC 不使能時(shí),VREF+引腳可接地。

內(nèi)部電壓參考緩沖器支持四個(gè)輸出電壓,可利用 VREFBUF_CSR 寄存器中的 VRS[2:0]字段進(jìn)行配置:

– VREF+大約為 1.5 V。這要求 VDDA ≥ 1.8 V。

– VREF+大約為 1.8 V。這要求 VDDA ≥ 2.1 V。

– VREF+大約為 2.048 V。這要求 VDDA ≥ 2.4 V。

– VREF+大約為 2.5 V。這要求 VDDA ≥ 2.8 V。

VREF- 和 VREF+ 引腳并非在所有封裝上可用。當(dāng)不可用時(shí),它們分別與 VSSA 和 VDDA 引腳綁定。

當(dāng) VREF+引腳與 VDDA 在一個(gè)封裝中互相綁定時(shí),內(nèi)部 VREFBUF 不可用且必須禁用。

VREF- 必須始終等于 VSSA。

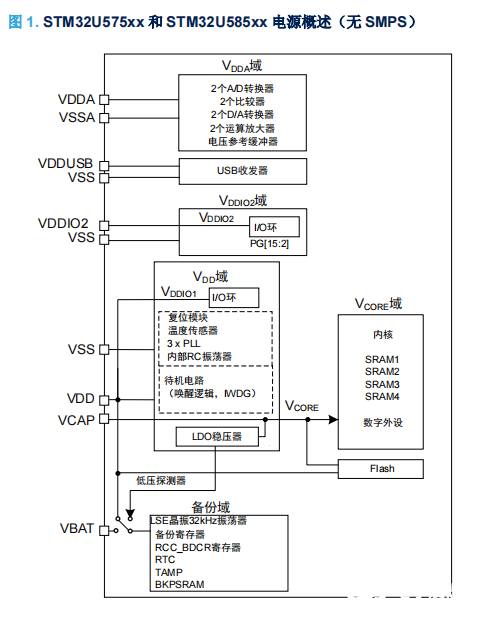

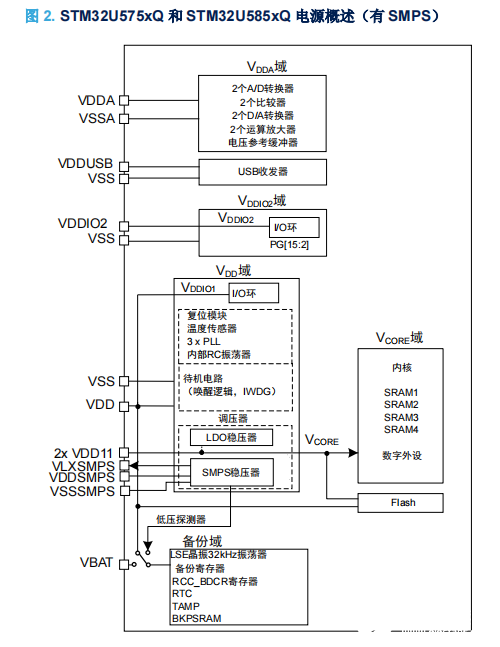

下圖顯示了 STM32U575/585 器件電源概述,具體取決于 SMPS 存在性。

在無(wú) SMPS 的器件中,I/O 和系統(tǒng)模擬外設(shè)(如 PLL 和復(fù)位模塊)由 DD 電源供電。為數(shù)字外設(shè)和存儲(chǔ)器供電的VCORE 電源由 LDO 生成。

提示 如果選定的封裝具有 SMPS 降壓轉(zhuǎn)換器選項(xiàng),但 SMPS 不被應(yīng)用程序使用(而是使用嵌入式 LDO),則建議設(shè)置 SMPS 電源引腳,如下所示:

? 將 VDDSMPS 和 VLXSMPS 連接至 VSS

? 將 VDD11 引腳通過(guò)兩個(gè)(2.2 μF + 100 nF)電容連接至 VSS(如在正常模式下)

2.1.1 獨(dú)立模擬外設(shè)電源

為了提高 ADC 和 DAC 轉(zhuǎn)換精度、擴(kuò)展供電的靈活性,模擬外設(shè)配有獨(dú)立電源,可以單獨(dú)濾波并屏蔽 PCB 上的噪聲。

模擬外設(shè)的電壓電源輸入在單獨(dú)的 VDDA 引腳上可用。VSSA 引腳提供了獨(dú)立的電源接地連接。

VDDA 電源電壓可與 VDD 不同。復(fù)位后,由 VDDA 供電的模擬外設(shè)是邏輯隔離且電隔離的,因而不可用。當(dāng) VDDA電源存在時(shí),使用這些外設(shè)前,必須通過(guò)設(shè)置 PWR_SVMCR 寄存器中的 ASV 位,解除此隔離。

VDDA 電源可由模擬電壓監(jiān)測(cè)(AVM)監(jiān)控,并與兩個(gè)閾值(AVM1 為 1.6 V,而 AVM2 為 1.8 V)進(jìn)行比較。有關(guān)更多詳細(xì)信息,請(qǐng)參見(jiàn)器件數(shù)據(jù)手冊(cè)和參考手冊(cè)的“外設(shè)電壓監(jiān)測(cè)(PVM)”部分。

當(dāng)使用單供電時(shí),VDDA 引腳可外部連接至同一 VDD 電源,為得到無(wú)噪聲的 VDD 參考電壓,需通過(guò)外部濾波電路。

ADC 和 DAC 參考電壓

為確保低電壓輸入和輸出上的更好精度,用戶可將 VREF+連接至一個(gè)獨(dú)立的、低于 VDDA 的參考電壓源。

對(duì)于模擬輸入 (ADC)或輸出 (DAC)信號(hào), VREF+為最高電壓,以滿量程值表示。VREF+可由外部參考或VREFBUF(可以輸出可配置電壓:1.5、1.8、2.048 或 2.5 V)來(lái)提供。VREFBUF 還可通過(guò) VREF+引腳為外部元件提供電壓。

有關(guān)更多信息,請(qǐng)參見(jiàn)器件數(shù)據(jù)手冊(cè)和參考手冊(cè)的“電壓參考緩沖器(VREFBUF)”部分。

2.1.2 獨(dú)立 I/O 電源軌

來(lái)自端口 G(PG[15:2])的一些 I/O 由單獨(dú)的電源軌供電。此軌的電源范圍為 1.08 V 至 3.6 V,可通過(guò) VDDIO2 引腳外部提供。VDDIO2 電壓電平完全獨(dú)立于 VDD 或 VDDA。

VDDIO2 引腳僅可用于一些封裝(參見(jiàn)數(shù)據(jù)手冊(cè)中的引腳排列詳細(xì)信息,以了解 I/O 列表)。

復(fù)位后,由 VDDIO2 供電的 I/O 是邏輯隔離且電隔離的,因而不可用。當(dāng) VDDIO2 電源存在時(shí),從 PG[15:2]使用任一I/O 前,必須通過(guò)設(shè)置 PWR_SVMR 寄存器中的 IO2SV 位,解除此隔離。

VDDIO2 電源由 VDDIO2 電壓監(jiān)測(cè)(IO2VM)監(jiān)控且與內(nèi)部參考電壓(3/4 VREFINT,約為 0.9 V)進(jìn)行比較。有關(guān)更多詳細(xì)信息,請(qǐng)參見(jiàn)器件數(shù)據(jù)手冊(cè)和參考手冊(cè)的“外設(shè)電壓監(jiān)測(cè)(PVM)”部分。

2.1.3 獨(dú)立的 USB 收發(fā)器電源

USB 收發(fā)器通過(guò)一個(gè)單獨(dú)的電源 VDDUSB 供電。VDDUSB 范圍從 3.0 V 到 3.6V,完全獨(dú)立于 VDD 或 VDDA。

復(fù)位后,由 VDDUSB 供電的 USB 功能是邏輯隔離且電隔離的,因而不可用。當(dāng) VDDUSB 電源存在時(shí),使用 USB OTG 外設(shè)前,須通過(guò)設(shè)置 PWR_SVMR 寄存器中的 USV 位,解除此隔離。

VDDUSB 電源由 USB 電壓監(jiān)測(cè)(UVM)監(jiān)控且與內(nèi)部參考電壓(VREFINT,約為 1.2 V)進(jìn)行比較。有關(guān)更多詳細(xì)信息,請(qǐng)參見(jiàn)器件數(shù)據(jù)手冊(cè)和產(chǎn)品參考手冊(cè)的“外設(shè)電壓監(jiān)測(cè)(PVM)”部分。

2.1.4 電池備份域

為了在 VDD 掉電時(shí),還能保留備份寄存器的內(nèi)容,且為 RTC 供電,可將 VBAT 引腳連接到電池或者其他備用電源上。

VBAT 引腳為 RTC、TAMP、LSE 振蕩器和 PC13 到 PC15 I/O 供電,允許 RTC 在主電源關(guān)閉時(shí)也可工作。

當(dāng)在 PWR_BDCR1 寄存器中設(shè)置 BREN 位時(shí),可通過(guò) VBAT 引腳為備份 SRAM 供電。

VBAT 電源的開(kāi)關(guān)由復(fù)位模塊中內(nèi)置的掉電復(fù)位電路進(jìn)行控制。

Caution:

? 在 tRSTTEMPO(VDD 啟動(dòng)時(shí))或 PDR(下電復(fù)位)檢測(cè)期間,VBAT 和 VDD 之間的電源開(kāi)關(guān)仍連接到 VBAT引腳。

? 在啟動(dòng)階段,如果 VDD 的建立時(shí)間小于 tRSTTEMPO(有關(guān) tRSTTEMPO 的值,參見(jiàn)數(shù)據(jù)手冊(cè))且 VDD > VBAT+ 0.6 V,會(huì)有電流經(jīng)由 VDD 引腳和電源開(kāi)關(guān)(VBAT)之間連接的內(nèi)部二極管注入 VBAT 引腳。如果連接到VBAT 引腳的電源/電池?zé)o法承受此注入電流,則強(qiáng)烈建議在該電源與 VBAT 引腳之間連接一個(gè)低壓降二極管。如果沒(méi)有使用任何外部電池,建議將該 VBAT 引腳連接到帶有 100 nF 外部去耦電容的 VDD 上。

通過(guò) VDD 對(duì)備份域供電時(shí)(模擬開(kāi)關(guān)連接到 VDD 引腳),以下引腳可用:

? PC13、PC14 和 PC15,可用作 GPIO 引腳

? PC13、PC14 和 PC15——三個(gè)引腳可由 RTC 或 LSE 進(jìn)行配置(參見(jiàn)參考手冊(cè)的 RTC 部分)

? 下列引腳,由 TAMP 配置為篡改引腳:

– PE3(TAMP_IN6/TAMP_OUT3)

– PE4(TAMP_IN7/TAMP_OUT8)

– PE5(TAMP_IN8/TAMP_OUT7)

– PE6(TAMP_IN3/TAMP_OUT6)

– PC13(TAMP_IN1/TAMP_OUT2)

– PA0(TAMP_IN2/TAMP_OUT1)

– PA1(TAMP_IN5/TAMP_OUT4)

– PC5(TAMP_IN4/TAMP_OUT5)

提示

? 由于電源開(kāi)關(guān)僅能傳遞有限的電流(3 mA),因此使用輸出模式的 PC13 到 PC15 I/O 受限:速率必須限制在2 MHz,最大負(fù)載為 30 pF。這些 I/O 不能作為電流源使用(如,驅(qū)動(dòng) LED)。

? 在 VDD 下,TAMP_OUTx 引腳(PE3、PE4、PE5、PE6、PA0、PA1、PC5)與其連接到的 GPIO 保持相同的速度特性。但是,在 VBAT 下,TAMP_OUTx 引腳的速度必須限制為 500 kHz。

? 在 VDD 或 VBAT 下,PC13 引腳的速度必須始終限制為 2 MHz。

備份域訪問(wèn)

系統(tǒng)復(fù)位后,備份域(RCC_BDCR、PWR_BDCR1、RTC、TAMP、備份寄存器及備份 SRAM)將受到保護(hù),以防止意外的寫訪問(wèn)。要使能對(duì)備份域的訪問(wèn),請(qǐng)按以下步驟進(jìn)行操作:

1. 通過(guò)在 RCC_AHB3ENR 寄存器中設(shè)置 PWREN 位,使能電源接口時(shí)鐘。

2. 在 PWR_DBPR 寄存器中設(shè)置 DBP 位,使能對(duì)備份域的訪問(wèn)。

VBAT 電池充電

當(dāng) VDD 存在時(shí),可通過(guò) 5 kΩ 或 1.5 kΩ 的內(nèi)部電阻為 VBAT 上的外部電池供電,具體取決于 PWR_BDCR2 寄存器中的 VBRS 位。

可通過(guò)在 PWR_BDCR2 中設(shè)置 VBE 位來(lái)使能電池充電。在 VBAT 模式下自動(dòng)禁用。

2.1.5 調(diào)壓器

STM32U575/585 器件并聯(lián)嵌入了以下內(nèi)部調(diào)節(jié)器,以便為數(shù)字外設(shè)、SRAM1/2/3/4 和嵌入式 Flash 存儲(chǔ)器提供VCORE 電源:

? SMPS 降壓轉(zhuǎn)換器

? LDO(線性電壓穩(wěn)壓器)

可以在應(yīng)用程序運(yùn)行時(shí)進(jìn)行選擇,具體取決于應(yīng)用需求。SMPS 可降低功耗,但 SMPS 產(chǎn)生的噪音可能會(huì)影響一些外設(shè)行為,需要應(yīng)用程序在運(yùn)行外設(shè)時(shí)切換至 LDO,以達(dá)到最佳性能。

除了待機(jī)電路和備份域,LDO 或 SMPS 可用于所有電壓調(diào)節(jié)范圍(范圍 1/2/3/4)、所有停止模式(停止 0/1/2/3)和待機(jī)模式(有 SRAM2)(參見(jiàn)參考手冊(cè)中的“低功耗模式總結(jié)”表)。

無(wú) SMPS 的 STM32U575/585 器件僅嵌入了 LDO 穩(wěn)壓器,該穩(wěn)壓器可控制所有電壓調(diào)節(jié)范圍和功耗模式。

動(dòng)態(tài)電壓調(diào)節(jié)管理

LDO 和 SMPS 穩(wěn)壓器可提供四種不同的電壓(電壓調(diào)節(jié)),且可在所有停止模式下工作。這兩種穩(wěn)壓器均可在以下范圍操作:

? 范圍 1(1.2 V、160 MHz),高性能:提供 1.2 V 的典型輸出電壓,且在系統(tǒng)時(shí)鐘頻率高達(dá) 160 MHz 時(shí)使用。

? 范圍 2(1.1 V、110 MHz),中/高性能:提供 1.1 V 的典型輸出電壓,且在系統(tǒng)時(shí)鐘頻率高達(dá) 110 MHz 時(shí)使用。

? 范圍 3(1.0 V、55 MHz),低/中功率:提供 1.0 V 的典型輸出電壓,且在系統(tǒng)時(shí)鐘頻率高達(dá) 55 MHz 時(shí)使用。

? 范圍 4(0.9 V、25 MHz),低功率:提供 0.9 V 的典型輸出電壓,且在系統(tǒng)時(shí)鐘頻率高達(dá) 25 MHz 時(shí)使用。

通過(guò) PWR_VOSR 寄存器中的 VOS[1:0]字段選擇電壓調(diào)節(jié)。

Caution:

在將范圍 1 和范圍 2 中的系統(tǒng)時(shí)鐘頻率增加至超過(guò) 50 MHz 之前,必須啟用EPOD(嵌入式功率分配)加速器且使其就緒(有關(guān)在電壓調(diào)節(jié)范圍之間切換的順序,參見(jiàn)參考手冊(cè))。

2.1.6 I/O 模擬開(kāi)關(guān)的供電

一些 I/O 嵌入模擬開(kāi)關(guān),用于模擬外設(shè)(ADC、COMP、DAC)和 TSC(觸摸感應(yīng)控制器)功能。默認(rèn)情況下,這些開(kāi)關(guān)由 VDDA 供電,但可以由 VDDA 升壓器或 VDD 供電,具體取決于SYSCFG_CFGR1 寄存器中 ANASWVDD和 BOOSTEN 位的配置。

建議在 VDDA、VDDA 升壓器和 VDD 之間以最高電壓值為 I/O 開(kāi)關(guān)供電。

提示 如果可能,選擇噪音通常較小的 VDDA 或 VDDA 升壓器,而非 VDD。TSC 功能的模擬開(kāi)關(guān)由 VDD 供電。

2.2 電源方案

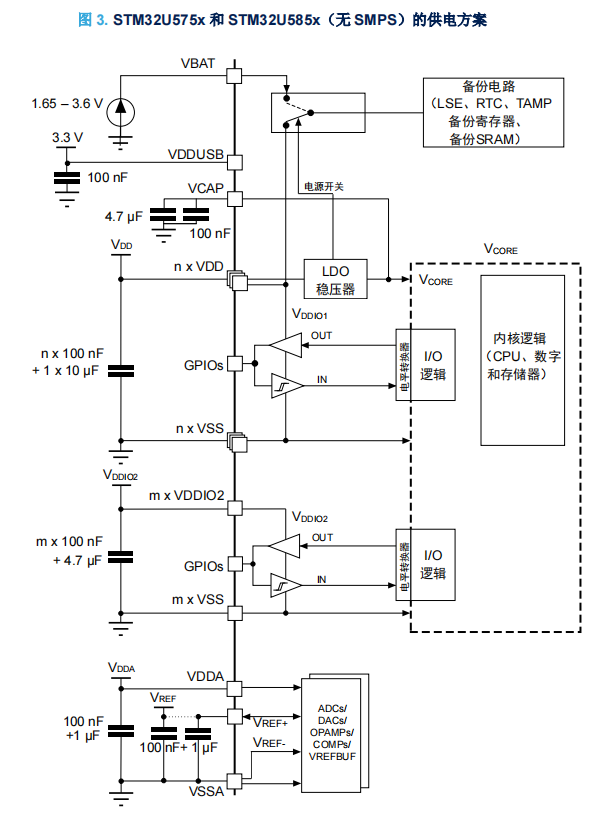

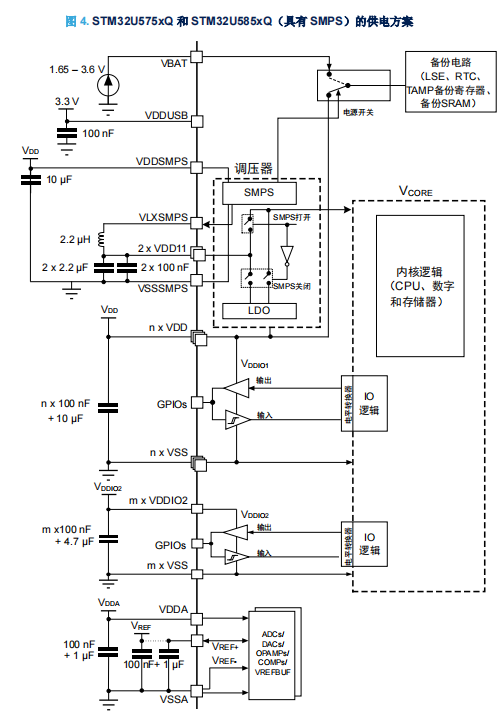

器件通過(guò)穩(wěn)定的 VDD 電源供電,如下所述:

? VDD 引腳必須連至帶有外部去耦電容的 VDD:封裝的 10 μF(典型值,最低 4.7 μF)單個(gè)鉭電容或陶瓷電容,及每個(gè) VDD 引腳的 100 n 陶瓷電容。

? VDD11 引腳僅出現(xiàn)在有 SMPS 的封裝上。SMPS 降壓轉(zhuǎn)換器需要在 VLXSMPS 和 VDD11 引腳之間連接一個(gè)2.2 μH(典型值)外部陶瓷線圈。此外,將 VDD11 引腳上的兩個(gè) 2.2 μF 電容連接到 VSSSMPS 引腳。接著,需要在每個(gè) VDD11 引腳和接地之間連接一個(gè) 100 nF 陶瓷電容。

? VCAP 引腳僅出現(xiàn)在標(biāo)準(zhǔn)封裝(無(wú) SMPS)上。它需要將一個(gè) 4.7 μF(典型值)外部去耦電容連接至 VSS。如果有兩個(gè) VCAP 引腳(UFBGA169 封裝),則每個(gè) VCAP 引腳必須連接至 2.2 μF(典型值)電容(最大4.7 μF)。此外,需要在每個(gè) VCAP 引腳和接地之間連接一個(gè) 100 nF 陶瓷電容。

? VDDA 引腳必須連至兩個(gè)外部去耦電容,100 nF 陶瓷電容和 1 μF 鉭電容或陶瓷電容。可采用更多措施過(guò)濾數(shù)字噪聲:VDDA 可通過(guò)鐵氧體磁環(huán)連至 VDD。

? VDDIO2 引腳必須連接至 4.7 μF 的外部去耦電容、鉭電容或陶瓷電容。此外,每個(gè) VDDIO2 引腳需要一個(gè)外部 100 nF 陶瓷電容。

? VDDUSB 引腳必須連接至外部 100 nF 陶瓷電容。

? VREF+引腳可通過(guò)外部電壓參考提供。這種情況下,必須在此引腳上連接外部 100 nF + 1 μF 鉭或陶瓷電容。它也可由 VREFBUF 內(nèi)部供電。這種情況下,此引腳上必須連接外部 100 nF + 1 μF(典型值)電容。

? VBAT 引腳可連接至外部電池來(lái)保持備份域內(nèi)容:

– 當(dāng) VDD 存在時(shí),可通過(guò) 5 kΩ 或 1.5 kΩ 的內(nèi)部電阻為 VBAT 上的外部電池充電。這種情況下,用戶可以根據(jù)預(yù)期的放電時(shí)間插入一個(gè)電容(建議 1 μF)。

– 如果沒(méi)有使用任何外部電池,建議將該 VBAT 引腳連接到帶有 100 nF 外部去耦電容的 VDD 上。

? VDDUSB 引腳在出現(xiàn)在封裝中時(shí)可以連接至 100 nF 的陶瓷電容。

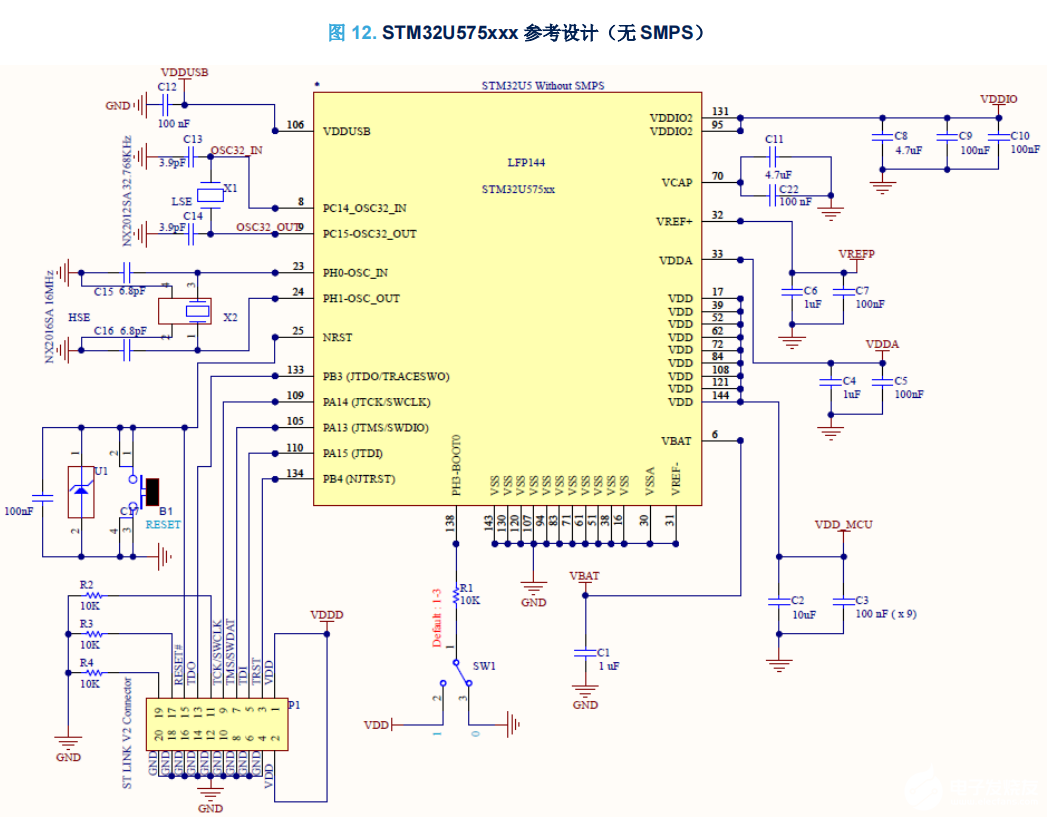

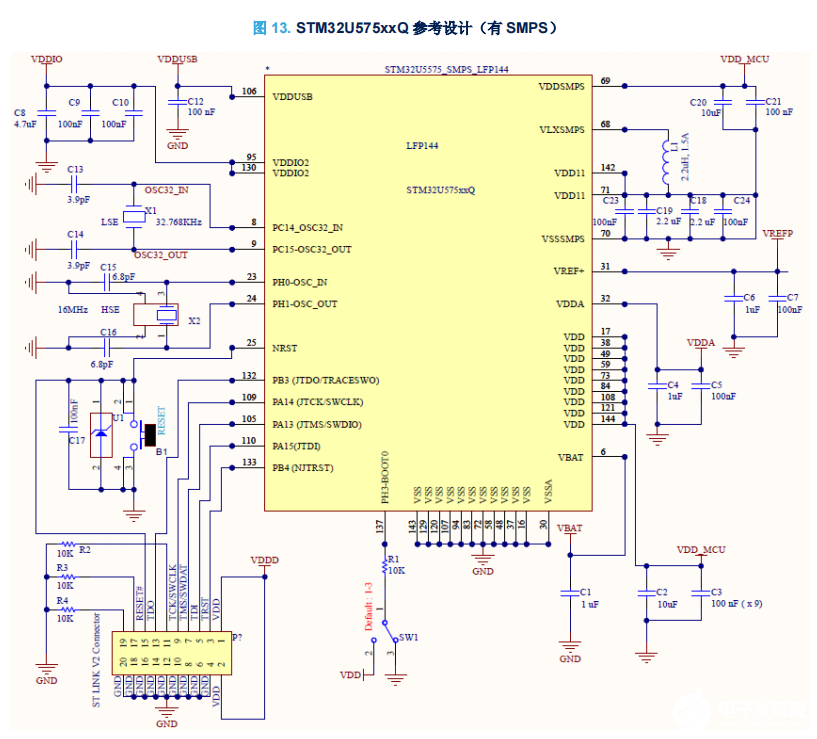

下圖詳細(xì)介紹了有 SMPS 和無(wú) SMPS 封裝的供電方案。

Caution:

如果有兩個(gè) VCAP 引腳(UFBGA169 封裝),則每個(gè)引腳必須連接至 2.2 μF(典型值)電容(總量約為 4.4μF)。

提示

? SMPS 和 LDO 穩(wěn)壓器同時(shí)提供 VCORE 電源,具體取決于應(yīng)用需求。但是,同時(shí)只能有其中一個(gè)穩(wěn)壓器為有效。當(dāng) SMPS 有效時(shí),它在通過(guò) SMPS VLXSMPS 輸出引腳提供的兩個(gè) VDD11 引腳上向VCORE 饋電。然后,在每個(gè) VDD11 引腳上需要一個(gè) 2.2 μH 線圈和 2.2 μF 電容。LDO 在有效時(shí)向 VCORE 供電并使用VDD11 引腳上的相同去耦電容對(duì)其進(jìn)行調(diào)節(jié)。

? 需要在每個(gè) VDD11 引腳/焊球附近添加一個(gè) 100 nF 的去耦電容。

2.3 VDDA、VDDUSB、VDDIO2 和 VDD 之間的供電排序

2.3.1 電源隔離

器件具有強(qiáng)大的復(fù)位系統(tǒng),該系統(tǒng)可確保主電源(VDD)在釋放 MCU 復(fù)位之前達(dá)到有效的工作范圍。

此復(fù)位系統(tǒng)還負(fù)責(zé)隔離獨(dú)立的電源域:VDDA、VDDUSB、VDDIO2 和 VDD。此復(fù)位系統(tǒng)由 VDD 供電且在 VDD 達(dá)到最低電壓(在最差條件下為 1 V)之前不工作。

為了避免在可用電源和 VDD(或接地)之前泄漏電流,在下電期間必須先將 VDD 供應(yīng)至 MCU,最后再釋放(有容差)(參見(jiàn)第 2.3.3 節(jié) )。

2.3.2 一般要求

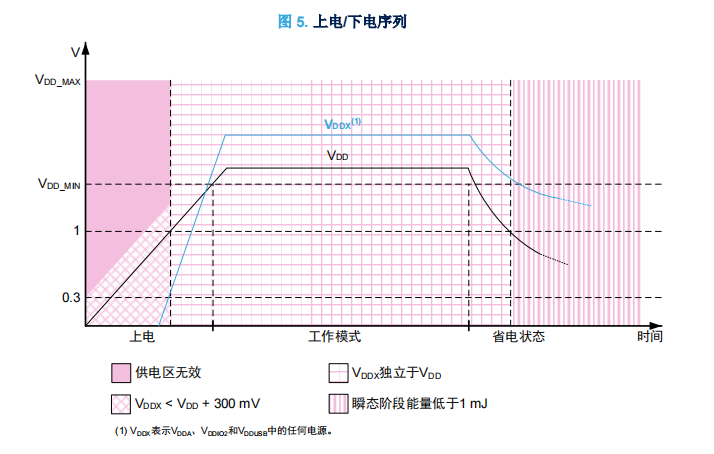

在上電和下電階段,必須遵守以下電源序列要求:

? 當(dāng) VDD 低于 1 V 時(shí),其他電源(VDDA、VDDIO2 和 VDDUSB)必須保持低于 VDD + 300 mV。

? 當(dāng) VDD 超過(guò) 1 V 時(shí),所有電源均為獨(dú)立。

提示 VBAT 是獨(dú)立的電源且沒(méi)有限制與 VDD。所有電源干線可連接到一起。

2.3.3 下電階段的特定條件

在下電階段,VDD 僅在為 MCU 提供的能量仍低于 1 mJ 時(shí)暫時(shí)低于其他電源。這使外部去耦電容在下電瞬態(tài)階段以不同的時(shí)間常量放電(參見(jiàn)圖 5)。

VDDX(VDDA、VDDIO2 或 VDDUSB)電源軌必須在 DD 之前關(guān)閉。

提示 在下電瞬態(tài)階段,VDDX 可仍臨時(shí)超過(guò) VDD(參見(jiàn)圖 5)。

下電階段向 MCU 提供能量的計(jì)算示例

如果 VDDX 上的去耦電容總和為 10 μF 且 VDD 降至 1 V 以下,而 VDDX 仍為 3.3 V,則去耦電容中的剩余能量為:

E = ? C x V2 = ? x 10-5 x 3.32 = 0.05 mJ

去耦電容中的剩余能量低于 1 mJ,因此,可接受 MCU 對(duì)其進(jìn)行吸收。

2.4 復(fù)位和電源監(jiān)控

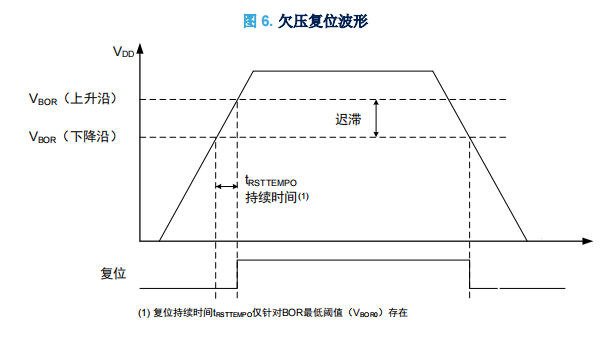

2.4.1 欠壓復(fù)位(BOR)

器件具有欠壓復(fù)位(BOR)電路。除關(guān)斷模式外,BOR 在所有功耗模式下均激活,且不可禁用。BOR 監(jiān)測(cè)備份域電源電壓,即在存在時(shí)為 VDD,不存在時(shí)為 VBAT。

通過(guò)選項(xiàng)字節(jié),可對(duì) 5 個(gè) BOR 閾值進(jìn)行選擇。

上電期間,BOR 將使器件保持復(fù)位狀態(tài),直到電源電壓 VDD 達(dá)到指定的 VBORx 閾值。當(dāng) VDD 降至所選閾值以下時(shí),將使器件復(fù)位。當(dāng) VDD 高于 VBORx 上限時(shí),釋放器件復(fù)位,系統(tǒng)可以啟動(dòng)。

有關(guān)欠壓復(fù)位閾值的詳細(xì)信息,參見(jiàn)數(shù)據(jù)手冊(cè)的電氣特性部分。

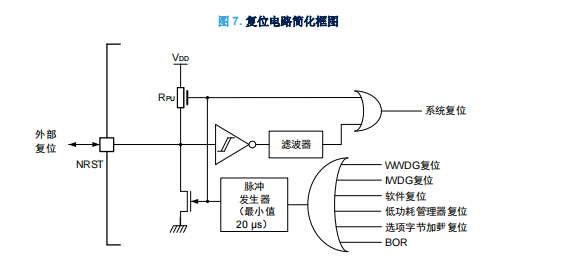

2.4.2 系統(tǒng)復(fù)位

除了寄存器 RCC_CSR 中的復(fù)位標(biāo)志和備份域中的寄存器外,系統(tǒng)復(fù)位會(huì)將其它全部寄存器都復(fù)位為復(fù)位值。

只要發(fā)生以下事件之一,就會(huì)產(chǎn)生系統(tǒng)復(fù)位(參見(jiàn)參考手冊(cè)以了解更多詳細(xì)信息):

? NRST 引腳低電平(外部復(fù)位)

? 窗口看門狗事件(WWDG 復(fù)位)

? 獨(dú)立看門狗事件(IWDG 復(fù)位)

? 軟件復(fù)位

? 低功耗模式安全復(fù)位

? 選項(xiàng)字節(jié)加載復(fù)位

? 欠壓復(fù)位

這些源均作用于 NRST 引腳,該引腳在時(shí)延階段中始終保持低電平。通過(guò)啟動(dòng)選項(xiàng)字節(jié)選擇復(fù)位服務(wù)入口向量。

芯片內(nèi)部的復(fù)位信號(hào)會(huì)向 NRST 引腳上輸出一個(gè)低電平脈沖。脈沖發(fā)生器可確保每個(gè)內(nèi)部復(fù)位源的復(fù)位脈沖都至少持續(xù) 20 μs。對(duì)于外部復(fù)位,在 NRST 引腳處于低電平時(shí)產(chǎn)生復(fù)位脈沖。

內(nèi)部復(fù)位情況下,內(nèi)部上拉 RPU 失效,從而節(jié)約功耗。

2.4.3 備份域復(fù)位

只要發(fā)生以下事件之一,就會(huì)產(chǎn)生備份域復(fù)位:

? 軟件復(fù)位,通過(guò)在 RCC_BDCR 寄存器中設(shè)置 BDRST 位來(lái)觸發(fā)

? 在電源 VDD 和 VBAT 都已掉電后,其中任何一個(gè)又再上電

備份域復(fù)位僅影響 LSE 振蕩器、RTC 和 TAMP、備份寄存器、備份 SRAM、RCC_BDCR 和 PWR_BDCR1 寄存器。

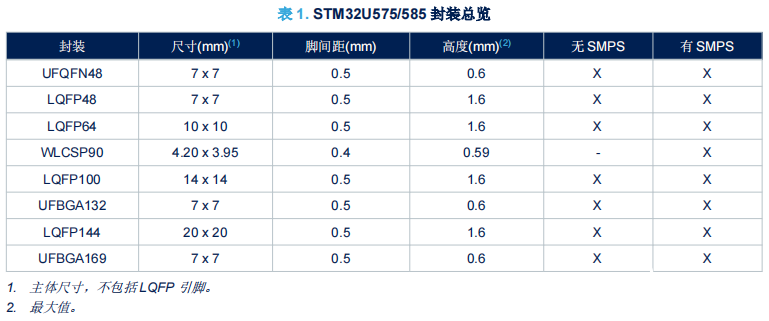

3、封裝

3.1 封裝總覽

封裝選擇必須考慮一些主要取決于應(yīng)用的限制。

下面匯總了最常見(jiàn)的一些限制:

? 需要的接口數(shù)量:部分封裝可能缺乏某些接口。某些接口組合在有的封裝上可能沒(méi)有。

? PCB 技術(shù)限制:窄間距和高焊球密度可能要求更多的 PCB 層數(shù)和更高級(jí)的 PCB。

? 封裝高度

? 可用的 PCB 面積

? 噪聲發(fā)射或者高速接口的信號(hào)完整性

? 更小的封裝通常具有更好的信號(hào)完整性。由于窄間距和高焊球密度需要多層 PCB,這樣可以有更好的電源/地分布,因此這一點(diǎn)得到進(jìn)一步增強(qiáng)。

? 與其它器件的兼容性

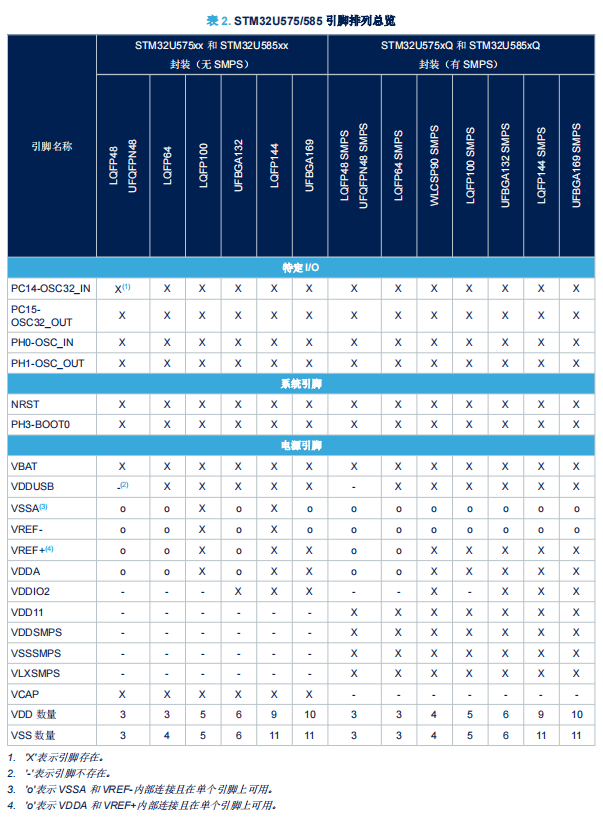

3.2 引腳排列總覽

Caution:在上表的幾乎所有電源引腳中,有 SMPS 和無(wú) SMPS 的 STM32U575/585 封裝彼此無(wú)法兼容。

示例:在有 SMPS 的封裝上,VDDIO2 為引腳號(hào) 130。而在無(wú) SMPS 的封裝上,引腳 130 映射到VSS 引腳。這意味著在 SMPS 插座上安裝傳統(tǒng)封裝時(shí),系統(tǒng)短路。

4、時(shí)鐘

可以使用下列時(shí)鐘源來(lái)驅(qū)動(dòng)系統(tǒng)時(shí)鐘 (SYSCLK):

? HSI16:高速內(nèi)部 16 MHz RC 振蕩器時(shí)鐘

? MSIS:多種速率內(nèi)部 RC 振蕩器時(shí)鐘

? HSE:高速外部晶振或時(shí)鐘,從 4 到 50 MHz

? PLL1 時(shí)鐘從復(fù)位中啟動(dòng)后,MSIS 用作系統(tǒng)時(shí)鐘源,配置為 4 MHz。

器件具有以下附加時(shí)鐘源:

? MSIK:多種速率內(nèi)部 RC 振蕩器時(shí)鐘,用于外設(shè)內(nèi)核時(shí)鐘

? LSI:32 kHz 低速內(nèi)部 RC,該 RC 用于驅(qū)動(dòng)獨(dú)立看門狗,也可選擇提供給 RTC 用于停機(jī)和待機(jī)模式下的自動(dòng)喚醒

? LSE:32.768 kHz 低速外部晶振或時(shí)鐘,用于驅(qū)動(dòng)實(shí)時(shí)時(shí)鐘(rtc_ck)

? HSI48:內(nèi)部 48 MHz RC,該 RC 用于潛在驅(qū)動(dòng) OTG FS、SDMMC 和 RNG

? SHSI:安全高速內(nèi)部 RC,該 RC 用于驅(qū)動(dòng)安全 AES (SAES)。

? PLL2 和 PLL3 時(shí)鐘

對(duì)于每個(gè)時(shí)鐘源來(lái)說(shuō),在未使用時(shí)都可單獨(dú)開(kāi)啟或者關(guān)閉,以降低功耗。多個(gè)預(yù)分頻器可用于配置 AHB 和 APB 頻率域,最大頻率為 160 MHz。

4.1 HSE 時(shí)鐘

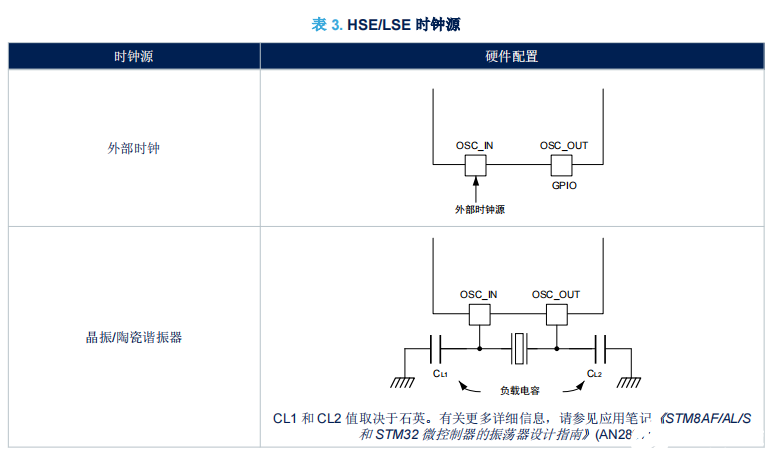

高速外部時(shí)鐘信號(hào)(HSE)有以下幾個(gè)時(shí)鐘源:

? HSE 外部晶振/陶瓷諧振器

? HSE 用戶外部時(shí)鐘,提供 OSC_IN 引腳

諧振器和負(fù)載電容必須盡可能地靠近振蕩器的引腳,以盡量減小輸出失真和起振穩(wěn)定時(shí)間。負(fù)載電容值必須根據(jù)所選振蕩器的不同做適當(dāng)調(diào)整。

4.1.1 外部晶振/陶瓷諧振器(HSE 晶振)

4 到 50 MHz 外部振蕩器的優(yōu)點(diǎn)是可以生成一個(gè)精度非常高的主時(shí)鐘。相關(guān)的硬件配置如表 3 所示。有關(guān)詳細(xì)信息,請(qǐng)參見(jiàn)數(shù)據(jù)手冊(cè)的電氣特性部分。

4.1.2 外部時(shí)鐘源(HSE 旁路)

在此模式下,必須提供外部時(shí)鐘源,頻率高達(dá) 50 MHz。必須使用占空比約為 40%至 60%的外部時(shí)鐘信號(hào)(方波、正弦波或三角波)來(lái)驅(qū)動(dòng) OSC_IN 引腳,具體取決于頻率(參考數(shù)據(jù)手冊(cè)),同時(shí) OSC_OUT 引腳可用作 GPIO

使用(請(qǐng)參見(jiàn)表 3)。

提示 有關(guān)引腳可用性的詳細(xì)信息,請(qǐng)參見(jiàn)數(shù)據(jù)手冊(cè)的引腳排列部分。要最大程度降低功耗,建議采用方波信號(hào)。

4.2 HSI16 時(shí)鐘

HSI16 時(shí)鐘信號(hào)是從 16 MHz 內(nèi)部 RC 振蕩器生成的。HSI16 RC 振蕩器以低成本提供時(shí)鐘源(無(wú)需使用外部元件)。它還比 HSE 晶振具有更快的啟動(dòng)時(shí)間。但即使校準(zhǔn)后,頻率也不如外部晶振或陶瓷諧振器的頻率精度高。

HSI16 時(shí)鐘還可作為備份時(shí)鐘源(輔助時(shí)鐘)使用,以防 HSE 晶振發(fā)生故障。

有關(guān)更多詳細(xì)信息,請(qǐng)參見(jiàn)參考手冊(cè)的“時(shí)鐘安全系統(tǒng)(CSS)”部分。

4.3 MSI(MSIS 和 MSIK)時(shí)鐘

MSI 由四個(gè)內(nèi)部 RC 振蕩器組成:MSIRC0 (48 MHz)、MSIRC1 (4 MHz)、MSIRC2 (3.072 MHz)和 MSIRC3 (400kHz)。每個(gè)振蕩器提供一個(gè)預(yù)分頻器,從而提供 1、2、3 或 4 分頻。

由這些分頻振蕩器生成兩個(gè)輸出時(shí)鐘:

? MSIS,可選擇作為系統(tǒng)時(shí)鐘

? MSIK,可由一些外設(shè)選擇作為內(nèi)核時(shí)鐘

可由軟件分別使用 RCC_ICSCR1 寄存器中的 MSISRANGE [3:0]和 MSIKRANGE [3:0]字段(且 MSIRGSEL = 1)來(lái)調(diào)整 MSIS 和 MSIK 頻率范圍。提供十六個(gè)頻率范圍,由四個(gè)內(nèi)部 RC 生成(參見(jiàn)參考手冊(cè)以了解更多詳細(xì)信息)。

如果 HSE 晶振發(fā)生故障,則 MSI 時(shí)鐘還可作為備份時(shí)鐘源(輔助時(shí)鐘)(參見(jiàn)參考手冊(cè)中的“時(shí)鐘安全系統(tǒng)(CSS)”部分)。

MSI 振蕩器可提供一個(gè)低成本(無(wú)外部元件)低功耗的時(shí)鐘源。此外,當(dāng)和 LSE 一起用于 PLL 模式時(shí),MSI 可提供一個(gè)非常精確的時(shí)鐘源,該時(shí)鐘源可用于 USB OTG-FS 外設(shè),并且向 PLL 反饋,使系統(tǒng)以最大速率 160 MHz 運(yùn)行。

利用 LSE 進(jìn)行硬件自動(dòng)校準(zhǔn)(PLL 模式)

當(dāng)應(yīng)用中存在 32.768 kHz 外部振蕩器時(shí),MSIS 或 MSIK 可配置為 PLL 模式。此模式已啟用,如下所示:

? 對(duì)于 MSIS:在 RCC_CR 寄存器中將 MSIPLLEN 位置為 1

? 對(duì)于 MSIK:在 RCC_CR 寄存器中將 MSIPLLEN 位置為 0

如果 MSIS 和 MSIK 范圍是從同一 MSIRC 源生成的,則 PLL 模式應(yīng)用于 MSIS 和 MSIK。當(dāng)配置為 PLL 模式時(shí),MSIS 或 MSIK 可利用 LSE 自動(dòng)校準(zhǔn)。該模式可用于所有 MSI 頻率范圍。48 MHz 時(shí),處于 PLL 模式的 MSIK 可用于 USB OTG FS 器件,不需要外部高速晶振。

關(guān)于如何測(cè)量 MSI 頻率偏移的更多詳細(xì)信息,參見(jiàn)參考手冊(cè)的“利用 TIM15/TIM16/TIM17 的內(nèi)部/外部時(shí)鐘測(cè)量”部分。

4.4 LSE 時(shí)鐘

LSE 晶振是 32.768 kHz 低速外部晶振或陶瓷諧振器(參見(jiàn)表 3)。它為 RTC(實(shí)時(shí)時(shí)鐘)外設(shè)提供低功耗且精度高的時(shí)鐘源,用于時(shí)鐘/日歷或其他定時(shí)功能。

使用 RCC_BDCR 寄存器中的 LSEDRV[1:0]位,可在運(yùn)行時(shí)更改晶振驅(qū)動(dòng)強(qiáng)度,以實(shí)現(xiàn)穩(wěn)定性、短啟動(dòng)時(shí)間和低功耗之間的最佳平衡。

外部時(shí)鐘源(LSE 旁路)

在此模式下,必須提供頻率高達(dá) 1 MHz 的外部時(shí)鐘源。必須使用占空比約為 50%的外部時(shí)鐘信號(hào)(方波、正弦波或三角波)來(lái)驅(qū)動(dòng) OSC32_IN 引腳,同時(shí) OSC32_OUT 引腳可以作為 GPIO 使用(參見(jiàn)表 3)。

5、自舉配置

5.1 啟動(dòng)模式選擇

啟動(dòng)時(shí),可通過(guò) BOOT0 引腳、nBOOT0 和NSBOOTADDx[24:0]/SECBOOTADD0[24:0]選項(xiàng)字節(jié)來(lái)選擇啟動(dòng)存儲(chǔ)器地址,啟動(dòng)地址包括:

? 從用戶 Flash 存儲(chǔ)器中的任何地址啟動(dòng)

? 從系統(tǒng)存儲(chǔ)器啟動(dòng)(自舉程序)

? 從嵌入式 SRAM 中的任何地址啟動(dòng)

? 從根安全服務(wù)(RSS)啟動(dòng)

BOOT0 值可能來(lái)自 PH3-BOOT0 引腳或選項(xiàng)位,具體取決于在需要時(shí)釋放 GPIO 焊盤的用戶選項(xiàng)位的值。

當(dāng)通過(guò)復(fù)位 TZEN 選項(xiàng)位(TZEN = 0)禁用 TrustZone?時(shí),啟動(dòng)空間如下表中詳述。

當(dāng)通過(guò)設(shè)置 TZEN 選項(xiàng)位(TZEN = 1)啟用 TrustZone 時(shí),啟動(dòng)空間必須位于安全區(qū)域。SECBOOTADD0[24:0]選項(xiàng)字節(jié)用于選擇啟動(dòng)安全內(nèi)存地址。可通過(guò)設(shè)置 BOOT_LOCK 選項(xiàng)位選擇唯一的啟動(dòng)條目選項(xiàng)。所有其他啟動(dòng)選項(xiàng)將被忽略。

下表詳細(xì)介紹了啟用 TrustZone 時(shí)的自舉模式。

5.2 嵌入式加載程序和 RSS

嵌入式自舉程序位于系統(tǒng)存儲(chǔ)器中,由意法半導(dǎo)體在生產(chǎn)階段編程。它被用來(lái)通過(guò)使用下列串行接口之一重新編程:

? USART:引腳 PA9/PA10 上的 USART1,引腳 PA2/PA3 上的 USART2,引腳 PC10/PC11 上的 USART3

? I2C:引腳 PB6/PB7 上的 I2C1,引腳 PB10/PB11 上的 I2C2 和引腳 PC0/PC1 上的 I2C3

? SPI:引腳 PA4/PA5/PA6/PA7 上的 SPI1、引腳 PB12/PB13/PB14/PB15 上的 SPI2 和引腳 PB5/PG9/PG10/PG12 上的 SPI3

? 引腳 PB8/PB9 上的 FDCAN1

? 引腳 PA11/PA12 上的 USB,通過(guò) DFU(器件固件升級(jí))在器件模式中使用

有關(guān) STM32 加載程序的更多詳細(xì)信息,請(qǐng)參見(jiàn)應(yīng)用筆記《STM32 微控制器系統(tǒng)存儲(chǔ)器自舉模式》(AN2606)。

RSS(根安全服務(wù))嵌入在名為“安全信息塊”的 Flash 存儲(chǔ)區(qū),在 ST 生產(chǎn)期間編程。

例如,RSS 使用 RSS 擴(kuò)展固件(RSSe SFI)啟用 SFI(安全固件安裝)。當(dāng)生產(chǎn)被分包給第三方時(shí),該特性允許客戶保護(hù)燒寫到 STM32 器件的固件的機(jī)密性。參照應(yīng)用筆記安全固件安裝(SFI)概述(AN4992)。

在通過(guò) TZEN 選項(xiàng)位啟用 TrustZone 后,RSS 在所有器件上可用。

6、調(diào)試管理

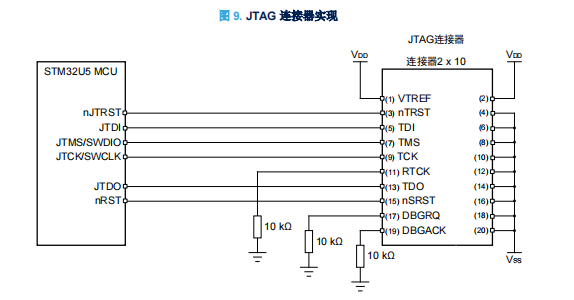

串行線/JTAG 調(diào)試端口(SWJ-DP)是 Arm 標(biāo)準(zhǔn) CoreSight?調(diào)試端口。

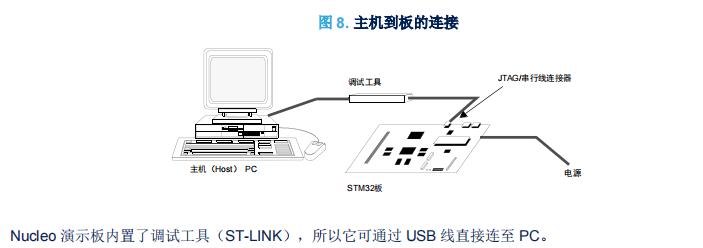

主機(jī)/目標(biāo)接口為連接主機(jī)與應(yīng)用板的硬件設(shè)備。此接口由三部分組成:硬件調(diào)試工具、串行線連接器,以及連接主機(jī)與調(diào)試工具的電纜。

下圖顯示了主機(jī)到開(kāi)發(fā)板的連接。

6.1 SWJ-DP(串行線和 JTAG 調(diào)試端口)

SWJ-DP 整合了:

? JTAG?DP,提供用于連接到 AHP-AP 端口的 5 引腳標(biāo)準(zhǔn) JTAG 接口

? SW-DP,提供用于連接到 AHP-AP 端口的 2 引腳(時(shí)鐘+數(shù)據(jù))接口

在 SWJ-DP 中,SW-DP 的 2 個(gè) JTAG 引腳與 JTAG-DP 的 5 個(gè) JTAG 引腳中的部分引腳復(fù)用。

提示 所有 SWJ-DP 端口 IO 都可以通過(guò)軟件重新配置為其他功能,不過(guò)在這種情況下不能再進(jìn)行調(diào)試。

6.2 引腳排列和調(diào)試端口引腳

器件的不同封裝有不同的有效引腳數(shù)。因此,一些與引腳可用性有關(guān)的功能可能會(huì)因封裝不同而不同。

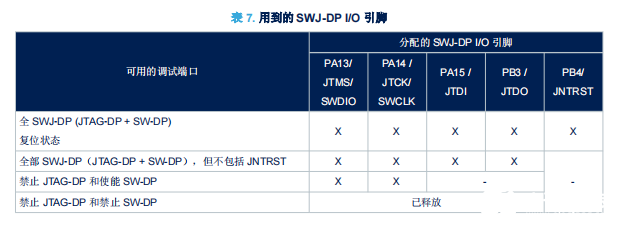

6.2.1 SWJ-DP 引腳

五個(gè)引腳被用作 SWJ-DP 的輸出,作為 GPIO(通用 I/O)的復(fù)用功能。所有封裝(如下表詳述)都提供這些引腳。

6.2.2 靈活的 SWJ-DP 引腳分配

復(fù)位(SYSRESETn 或 PORESETn)后,將用于 SWJ-DP 的全部 5 個(gè)引腳指定為專用引腳,可供調(diào)試工具立即使用。

提示 除非由調(diào)試工具明確編程,否則不分配跟蹤輸出。

下表顯示釋放一些引腳的多種可能性(有關(guān)更多詳細(xì)信息,參見(jiàn)參考手冊(cè))。

6.2.3 JTAG 引腳上的內(nèi)部上拉和下拉電阻

JTAG 輸入引腳不得懸空,因?yàn)檫@些引腳直接連接到用于控制調(diào)試模式功能的觸發(fā)器。還必須特別注意SWCLK/TCK 引腳,該引腳直接連接到一些觸發(fā)器的時(shí)鐘。

為避免 I/O 電平浮空,器件在 JTAG 輸入引腳上嵌入以下內(nèi)部電阻:

? JNTRST:內(nèi)部上拉

? JTDI:內(nèi)部上拉

? JTMS/SWDIO:內(nèi)部上拉

? TCK/SWCLK:內(nèi)部下拉

用戶軟件釋放 JTAG I/O 后,GPIO 控制器便會(huì)重新對(duì)其進(jìn)行控制,然后,軟件可將這些 I/O 作為標(biāo)準(zhǔn) GPIO。

GPIO 控制寄存器的復(fù)位狀態(tài)會(huì)將 I/O 置于以下同等狀態(tài):

? JNTRST:輸入上拉

? JTDI:輸入上拉

? JTMS/SWDIO:輸入上拉

? JTCK/SWCLK:輸入下拉

? JTDO:輸入浮空

提示 JTAG IEEE 標(biāo)準(zhǔn)建議在 TDI、TMS 和 nTRST 上增加上拉電阻,但對(duì) TCK 沒(méi)有特殊建議。然而,就器件而言,針對(duì) JTCK 采用了集成的下拉電阻。由于帶有上拉和下拉電阻,因此無(wú)需添加外部電阻。

6.2.4 使用標(biāo)準(zhǔn) JTAG 連接器的 SWJ-DP 連接

下圖顯示了器件和標(biāo)準(zhǔn) JTAG 連接器之間的連接。

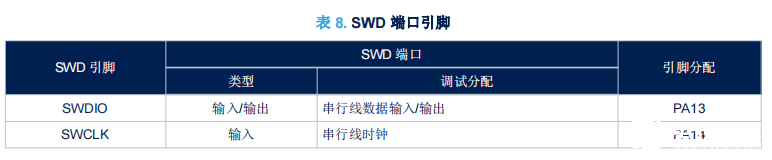

6.3 串行線調(diào)試 (SWD) 引腳分配

所有封裝(如下表詳述)都提供相同的 SWD 引腳分配。

復(fù)位后,將用于 SWD 的引腳指定為專用引腳,可供調(diào)試工具立即使用。但是,MCU 為禁用 SWD 提供了可能,因此可釋放相關(guān)引腳供 GPIO 使用。

有關(guān)如何禁用 SWD 端口的更多詳細(xì)信息,請(qǐng)參見(jiàn)參考手冊(cè)的“I/O 引腳復(fù)用功能復(fù)用器和映射”部分。

6.3.1 SWD 引腳上的內(nèi)部上拉和下拉

用戶軟件釋放 SWD I/O 后,GPIO 控制器便會(huì)控制它。GPIO 控制寄存器的復(fù)位狀態(tài)會(huì)將 I/O 置于同等狀態(tài):

? SWDIO:復(fù)用功能上拉

? SWCLK:復(fù)用功能下拉

由于帶有上拉和下拉電阻,因此無(wú)需添加外部電阻。

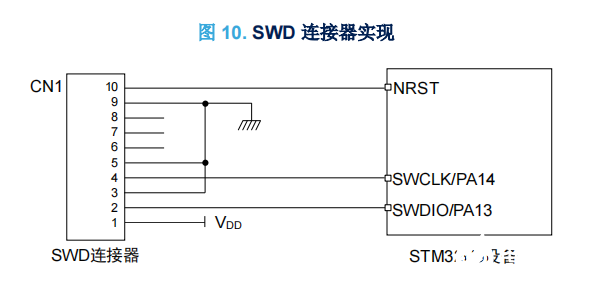

6.3.2 使用標(biāo)準(zhǔn) SWD 連接器的 SWD 端口連接

下圖顯示了器件和標(biāo)準(zhǔn) SWD 連接器之間的連接。

7、建議

7.1 PCB(印刷電路板)

由于技術(shù)原因,最好使用多層 PCB 的單獨(dú)一層專用于接地(VSS),另一層專用于 VDD 供電。

這提供了不錯(cuò)的去耦和屏蔽效果。對(duì)于很多應(yīng)用,由于經(jīng)濟(jì)原因不能使用此類板。在這種情況下,主要要求就是要確保接地和供電有良好的結(jié)構(gòu)。

7.2 元件位置

PCB 的初始布局必須將電路分為不同模塊:

? 高電流電路

? 低電壓電路

? 數(shù)字元件電路

? 根據(jù)電路的 EMI 影響分離電路,以降低因 PCB 上的交叉耦合產(chǎn)生的噪音

7.3 接地和供電

必須遵守與接地相關(guān)的以下規(guī)則:

? 使每個(gè)塊(噪聲、低電平敏感、數(shù)字或其他)單獨(dú)接地。

? 將所有接地返回為一個(gè)點(diǎn)。

? 避免出現(xiàn)環(huán)路(或確保其具有最小面積)。

為提高模擬性能,用戶必須對(duì) VDD 和 VDDA 使用單獨(dú)的電源,將去耦電容放置在離器件盡可能近的位置。

供電(VSS、VDD、VSSA、VDDA、VDDUSB、VDDIO2 或 VDDSMPS)必須靠近地線實(shí)現(xiàn),以最小化供電環(huán)的面積。這是因?yàn)楣╇姯h(huán)起到了天線及 EMI 主發(fā)收的作用。所有無(wú)元件的 PCB 區(qū)域都必須填充額外的接地,以創(chuàng)造屏蔽環(huán)境(尤其是當(dāng)使用單層 PCB 時(shí))。

7.4 去耦

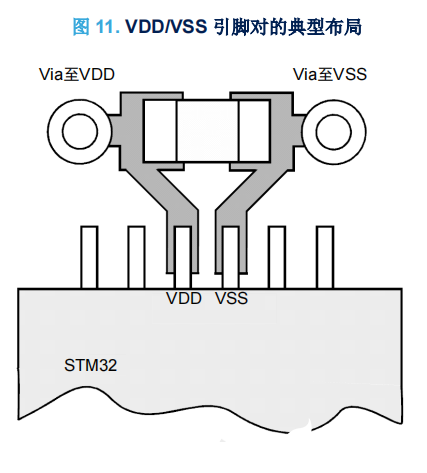

所有供電和接地引腳都必須適當(dāng)連至供電電源。這些連接(包括焊盤、線和過(guò)孔)都必須有盡可能低的阻抗。典型情況下,這可通過(guò)使用粗的線寬做到,最好在多層 PCB 中使用專用供電層。

此外,每個(gè)供電電源對(duì)都必須使用濾波陶瓷電容(100 nF)及約 10 μF 的鉭電容或陶瓷電容去耦,兩個(gè)電容并聯(lián)在器件上。

在某些封裝中,多個(gè) VDD 引腳使用同一個(gè) VSS 引腳,而不是一對(duì)電源引腳(每個(gè) VDD 對(duì)應(yīng)一個(gè)VSS)。這種情況下,電容必須處于每個(gè) VDD 引腳和公共 VSS 引腳之間。這些電容必須放置在 PCB 盡可能接近適當(dāng)引腳的位置,或在這些引腳下面 PCB 的底層。其典型值為 10 至 100 nF,但準(zhǔn)確值取決于應(yīng)用需要。

下圖顯示了這種 VDD/VSS 引腳對(duì)的典型布局。

7.5 其它信號(hào)

當(dāng)設(shè)計(jì)應(yīng)用時(shí),可通過(guò)仔細(xì)研究以下幾點(diǎn)來(lái)提高 EMC 性能:

? 臨時(shí)擾動(dòng)會(huì)永久影響運(yùn)行過(guò)程的信號(hào)(中斷和握手選通信號(hào)就是這個(gè)情況,但 LED 指令不是這個(gè)情況)

對(duì)于這些信號(hào),可使用周圍接地跟蹤、更短的長(zhǎng)度、無(wú)噪聲、附近敏感跟蹤(串?dāng)_影響)提高 EMC 性能。

對(duì)于數(shù)字信號(hào),兩個(gè)邏輯狀態(tài)必須達(dá)到可能的最佳電氣邊界。建議使用慢速施密特觸發(fā)器消除寄生狀態(tài)。

? 噪聲信號(hào)(例如:時(shí)鐘)

? 敏感信號(hào)(例如:高阻)

7.6 不使用的 I/O 和特性

所有微控制器都是為多種應(yīng)用設(shè)計(jì)的,通常一個(gè)應(yīng)用不會(huì)使用 100 %的 MCU 資源。

為了提高 EMC 性能和避免額外功耗,器件不使用的功能必須禁用且與時(shí)鐘樹(shù)斷開(kāi)連接,如下所示:

? 不使用的時(shí)鐘源必須禁用。

? 不使用的 I/O 不得浮空。

? 不使用的 I/O 引腳必須由軟件配置為模擬輸入,且必須通過(guò)外部或內(nèi)部上拉或下拉連接到固定邏輯電平 0 或1,或使用軟件配置為輸出模式。

8、參考設(shè)計(jì)

8.1 說(shuō)明

下圖中顯示的參考設(shè)計(jì)基于 LQFP144 中的 STM32U575/585 器件。使用第 8.2 節(jié) 中給出的引腳對(duì)應(yīng)關(guān)系,可將不同封裝的任何 STM32U575/585 器件定制此參考設(shè)計(jì)。

時(shí)鐘

兩個(gè)時(shí)鐘源用于 MCU(參見(jiàn)第 4 節(jié) 以了解更多詳細(xì)信息):

? LSE:X2 - 32.768 kHz 晶振用于嵌入式 RTC

? HSE:X1– 16 MHz 晶振,用于 MCU

更多詳細(xì)信息,參見(jiàn)第 4 節(jié) 。

復(fù)位

復(fù)位信號(hào)在第 8.2 節(jié) 中顯示的參考設(shè)計(jì)圖中為低電平有效。

復(fù)位源包括:

? 復(fù)位按鈕(B1)

? 調(diào)試工具通過(guò)連接器 CN1 連接

更多詳細(xì)信息,參見(jiàn)第 2.4 節(jié) 。

自舉模式

用戶可以在板上添加一個(gè)開(kāi)關(guān),以更改自舉選項(xiàng)。

更多詳細(xì)信息,參見(jiàn)第 5 節(jié) 。

提示 當(dāng)從待機(jī)模式喚醒時(shí),BOOT 引腳被采樣,且用戶必須注意其值。

SWD 接口

參考設(shè)計(jì)顯示了 STM32U575/585 器件和標(biāo)準(zhǔn) SWD 連接器之間的連接。

更多詳細(xì)信息,參見(jiàn)第 6 節(jié) 。

提示 建議連接復(fù)位引腳,以便能從工具復(fù)位應(yīng)用。

電源

更多詳細(xì)信息,參見(jiàn)第 2 節(jié) 。

8.2 元件參考

下表列出了 STM32U5 參考設(shè)計(jì)的組件(基于 STM32U5 Nucleo 板):

? 包括在無(wú) SMPS 的 STM32U575xx 器件上(參見(jiàn)圖 12)

? 包括在有 SMPS 的 STM32U575xxQ 器件上(參見(jiàn)圖 13)

來(lái)源:STM32單片機(jī)

免責(zé)聲明:本文為轉(zhuǎn)載文章,轉(zhuǎn)載此文目的在于傳遞更多信息,版權(quán)歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權(quán)問(wèn)題,請(qǐng)聯(lián)系小編進(jìn)行處理

審核編輯 黃宇

-

微控制器

+關(guān)注

關(guān)注

48文章

7570瀏覽量

151623 -

mcu

+關(guān)注

關(guān)注

146文章

17178瀏覽量

351675 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

5081瀏覽量

97696

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

STM32U575為什么無(wú)法通過(guò)LPTIM3將MCU從STOP2模式喚醒?

課程上線 | STM32單片機(jī)入門教程(1)基于HAL庫(kù)的多核心開(kāi)發(fā)(F1/F4/G0/U5)

應(yīng)用筆記 | STM32U575/585 MCU 硬件開(kāi)發(fā)入門

應(yīng)用筆記 | STM32U575/585 MCU 硬件開(kāi)發(fā)入門

評(píng)論