概述

BAP(BIST Access Port),即內建自測試訪問接口,主要用于In System Test,它要求芯片在已經部署到產品中,甚至芯片正在運行中,可對芯片的memory進行在線、實時地進行測試和診斷。

通常情況下,配置MBIST控制器,需要通過TAP接口啟動TAP控制器,通過IjtagNetwork來對相關TDR進行配置,隨后TDR使能相關信號對MBIST控制器進行配置,并啟動MBIST邏輯進行測試。

而BAP內建自測試訪問接口提供了不同于IjtagNetwork的串行訪問方式,可不經過IjtagNetwork,用BAP接口直接對MBIST控制器進行配置,由于不再使用IjtagNetwork的串行配置方式,沒有了shift cycle,大大縮短了測試時間,代價是需要在BAP接口和BAP控制器之間引入額外的連接。

BAP Architecture

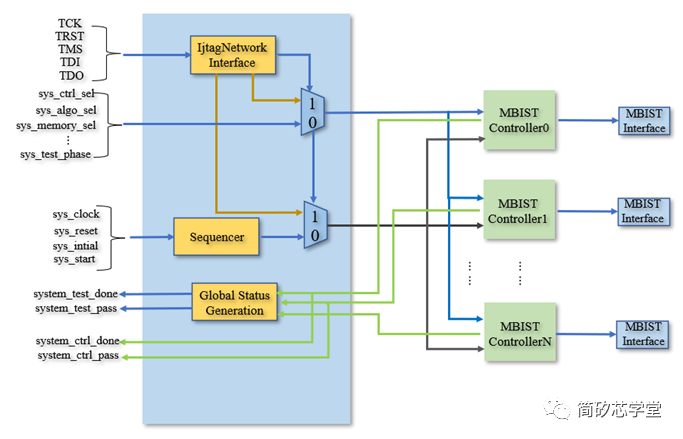

BAP 存儲器訪問架構由兩部分組成:IjtagNetwork訪問接口以及BAP的直接訪問接口。BAP的連接是由用戶配置的,直接連接到Function 邏輯。

圖1 BAP存儲器訪問架構

BAP的組成和功能

BAP的直接訪問接口由兩部分組成:Sequencer和Global Status Generation。

(1) Sequencer的功能是為MBIST Controller提供時鐘、復位、初始化、配置和start啟動信號,BAP內的sequencer能夠以低延遲的協議啟動和定制存儲器測試;在這種實現方式中,使用單個sequencer可以最小化BAP的門面積;sequencer的時鐘,sys_clock的頻率,應該和ijtag_tck相當,頻率較低,確保生成的控制信號能夠以正確的順序到達MBIST Controller;

(2) Global Status Generation的功能是采集來自于MBIST Controller的輸出信號,這些信號顯示了對存儲器的測試是否完成、是否通過或者測試失敗。

BAP的控制方式

BAP提供了2種對MBIST Controller的控制方式:

(1) 通過TAP接口、TAP Controller以及IjtagNetwork對掛載在IjtagNetwork下的TDRs進行配置,TDRs的輸出信號連接到MBIST Controller,從而實現對MBIST Controller的初始化、配置和啟動,完成對Memory進行測試;

(2) 通過BAP的直接訪問接口(Direct Access Interface)來直接控制MBIST Controller,完成對MBIST Controller的初始化、配置和啟動,完成對Memory的測試,而BAP的直接訪問接口(Direct Access Interface)的信號來自Function的系統信號。

BAP的其他特性

BAP直接訪問接口提供了配置存儲器測試的基礎選項,可以改變測試算法和操作,用戶可以選擇使用哪個控制器,決定在哪個step和去對哪個Memory進行測試。例如,如果分配的測試時間有限,可以利用這種靈活性,通過選擇具有很少指令的短算法,或者僅在一個控制器上執行MBIST測試。

BAP 直接訪問接口支持低延遲的協議配置MBIST控制器,執行GO/NoGo測試,監控測試通過的狀態。

Repair的分析也可以通過BAP的直接訪問接口進行,分析結果通過訪問BISR控制器可以用來進行軟件、硬件的增量修復。

BAP的配置方法

BAP的pin的創建和插入是由DFT spec配置的,通過指定 DFT spec中的屬性:direct_access 為 on,創建 出BAP的直接訪問接口(Direct Access interface)。

MemoryBist{

BistAccessPort {

DirectAccessOptions{

direct_access: on;

}

}

}

對于高級的In-System-Test的用法,使用DFT spec中的ExecutionSelection 字段,根據需求配置系統端的端口。

BAP的時鐘連接結構

BAP為每個Functional 時鐘創建一個Sequencer,這樣可以進一步減少開啟停止控制器的時間需求,可以更精確地在同一時鐘域中約束Sequencer到MBIST 控制器的關鍵路徑。

BAP 直接訪問接口支持兩種不同的時鐘方案,如何選擇依賴于in-system-test是如何執行的,每種方案對sys_clock的連接和信號都有不同的影響。時鐘源可以通過 DFT spec中的 direct access clock source字段進行配置,而時鐘連接則使用Connection下DirectAccess/CLockDomain字段進行配置。

(1) 當direct access clock source 被指定為 common時,將在BAP中創建一個Test Sequencer,管理與控制器相連接的Memory Test。對于此設置,必須指定Sequencer與系統時鐘的連接;

圖2 創建一個總的Sequencer

(2) 當direct access clock source 指定為 per bist clock domain時,將在BAP內部為每個MBIST時鐘域創建一個單獨的Sequencer,每個Sequencer的sys_clock會自動連接到 對應時鐘域的MBIST的時鐘。

圖3 每個時鐘域創建一個單獨的Sequencer

(圖2、圖3參考來源:Tessent MemoryBIST User’s Manual)

sys_test_done和sys_test_pass信號的采樣

對于單個和多個sequencer的實現方式,采樣sys_test_done/sys_test_pass的信號輸出有略微不同。

對于單個sequencer的情況,全局的sys_test_done,sys_test_pass狀態信號,以及每個controller的sys_ctrl_pass和sys_ctrl_done狀態信號是不會寄存在BAP接口中的。這些信號直接來自于各個MBIST Controller的DONE和GO信號,可能來自不同的時鐘域。

針對這種情況,需要考慮怎樣在Function邏輯中捕獲這些信號去避免潛在的跨時鐘域的問題。可使用由sys_test_clock或者其他合適的Function時鐘驅動的同步單元對sys_test_done和sys_test_pass輸出做同步。

針對多個sequencer的情況,不用考慮PASS、DONE的同步問題。

總結

本文主要介紹了BAP直接訪問接口的概念、架構、控制方式、配置方法、時鐘連接結構和sys_test_done/sys_test_pass信號的采樣。BAP提供了相比IjtagNetwork更加便捷、非串行的對MBIST的配置方式。該方式大大縮短了測試時間,提高了DFT的效率。

-

控制器

+關注

關注

112文章

16402瀏覽量

178589 -

存儲器

+關注

關注

38文章

7514瀏覽量

164004 -

時鐘源

+關注

關注

0文章

93瀏覽量

16002 -

時鐘驅動器

+關注

關注

0文章

33瀏覽量

13862 -

DFT設計

+關注

關注

0文章

10瀏覽量

8897

發布評論請先 登錄

相關推薦

菱沃鉑MCU的時鐘配置

如何將時鐘頻率和周期值傳遞PWM配置結構

L220 MBIST控制器技術參考手冊

CoreLink 2級MBIST控制器L2C-310技術參考手冊

ARM L210 MBIST控制器技術參考手冊

Cortex-A9 MBIST ControllerTechnical Reference

STM32入坑(七)使用HSI配置系統時鐘

78M6610+LMU/BAP - (Maxim Integrated) - PMIC - 能量計量

MBIST BAP的配置方法與時鐘連接結構

MBIST BAP的配置方法與時鐘連接結構

評論