實(shí)現(xiàn)原理概括

diag.2-1 原理框圖

diag.2-2 總電路圖

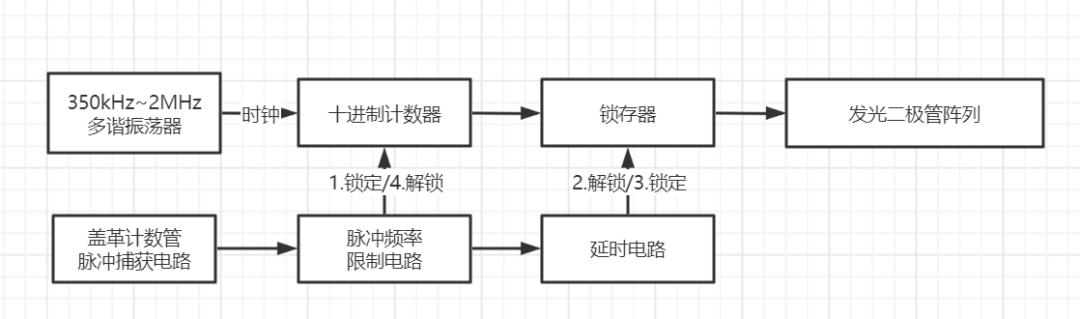

由七個(gè)模塊組成。多諧振蕩器 不間斷地產(chǎn)生350kHz~2MHz的時(shí)鐘脈沖,蓋革計(jì)數(shù)器無輸入時(shí),***十進(jìn)制計(jì)數(shù)器 ***做0,1,2,3...9,0,1,2...的周期性計(jì)數(shù)。

脈沖捕獲電路 捕獲并處理蓋革計(jì)數(shù)管的短暫脈沖信號(hào),觸發(fā) 脈沖頻率限制電路 。該電路立即鎖定十進(jìn)制計(jì)數(shù)器,并拒絕接收下一個(gè)輸入信號(hào),防止信號(hào)跳變對(duì)讀數(shù)造成的影響。這時(shí),十進(jìn)制計(jì)數(shù)器的輸出值即電路產(chǎn)生的隨機(jī)數(shù)。

同時(shí),延時(shí)電路 激活,在數(shù)百納秒后解鎖 鎖存器 ,1~2秒后重新鎖定,使鎖存器在十進(jìn)制計(jì)數(shù)器輸出值業(yè)已鎖死時(shí)保存脈沖輸入時(shí)計(jì)數(shù)器的輸出值。發(fā)光二極管陣列顯示這個(gè)數(shù)字。

自此又?jǐn)?shù)百納秒后,脈沖頻率限制電路解鎖計(jì)數(shù)器,并允許接收蓋革計(jì)數(shù)管的下一個(gè)信號(hào)。

** 由于蓋革計(jì)數(shù)管何時(shí)產(chǎn)生脈沖是高度隨機(jī)的,十進(jìn)制計(jì)數(shù)器何時(shí)停止計(jì)數(shù)也高度隨機(jī)**,這是實(shí)現(xiàn)真隨機(jī)性的核心原理。

在七個(gè)模塊中,十進(jìn)制計(jì)數(shù)器選用CD4017芯片,鎖存器選用74HC573芯片。下面對(duì)除發(fā)光二極管陣列外的四個(gè)模塊進(jìn)行解釋分析。

脈沖捕獲電路

diag.2-3 蓋革計(jì)數(shù)管脈沖捕獲電路

訂正:RV3阻值當(dāng)為200k

與上期推文的實(shí)驗(yàn)電路類似地,J3接蓋革計(jì)數(shù)管陰極,脈沖經(jīng)R23、R18分壓,C4耦合后再經(jīng)D13整流,接入電壓比較器正極。R19、RV3通過分壓調(diào)制一個(gè)基準(zhǔn)電壓,接比較器負(fù)極。R22是上拉電阻。

脈沖超過基準(zhǔn)電壓時(shí),U9輸出高電平,低于基準(zhǔn)電壓時(shí)輸出低電平,以此完成對(duì)蓋革計(jì)數(shù)管脈沖的數(shù)字化,并徹底濾除雜波。

脈沖頻率限制電路

蓋革計(jì)數(shù)管產(chǎn)生脈沖的時(shí)刻是高度隨機(jī)的,但其平均間隔時(shí)間取決于當(dāng)?shù)乇镜纵椛鋸?qiáng)度。如果輻射強(qiáng)度過高,則脈沖間隔過短,將對(duì)讀數(shù)效果造成很大影響。因此有必要限制脈沖頻率。

diag.2-4 脈沖頻率限制電路原理圖

圖中,U6A是與(AND)門芯片74HC08的一個(gè)單元,U5是時(shí)基集成電路NE555,PULSE接脈沖捕獲電路。

未出現(xiàn)脈沖時(shí),C3經(jīng)由R4、D3快速充電至VCC。Q輸出高電平,U6A pin3為低電平,DC對(duì)地表現(xiàn)為高阻。

輸入脈沖時(shí),U6A pin3翻轉(zhuǎn)為高電平,TH出現(xiàn)上升沿,U5內(nèi)部電路動(dòng)作,使Q輸出低電平, 這時(shí)無論P(yáng)ULSE是否出現(xiàn)高電平,U6A pin3始終保持低電平,從而阻斷了電路對(duì)下一個(gè)蓋革管脈沖的響應(yīng),下面稱這一階段為不應(yīng)期。

與此同時(shí),DC對(duì)地短路,D3截止,C3經(jīng)由D4、RV2向地放電,直至TR電位下降到低于1/3 VCC。然后,DC對(duì)地高阻,D4截止,C3通過R4、D3快速充電,Q也翻轉(zhuǎn)為高電平, 使U6A pin3的電位又由PULSE決定,即允許電路響應(yīng)下一個(gè)蓋革管脈沖。

U8是非(NOR)邏輯門芯片74HC04。電路處于不應(yīng)期時(shí),圖中U8的兩個(gè)單元都輸出高電平,觸發(fā)后續(xù)模塊。

延時(shí)鎖存電路

diag.2-5 延時(shí)電路原理圖(以紅框標(biāo)注)

延時(shí)電路用以 在前級(jí)電路已鎖定計(jì)數(shù)器一段時(shí)間后,使數(shù)據(jù)進(jìn)入鎖存器 。

結(jié)合前一節(jié)的講解,PULSE產(chǎn)生高電平時(shí),C3將進(jìn)入一個(gè)放—充電周期,其兩極板電壓如下圖所示:

gra.2-1 C3兩極板電壓

如圖,在約430ms時(shí)刻PULSE產(chǎn)生高電平,C3開始緩慢放電。1.8s時(shí)刻C3極板電壓低于閾值,電路控制C3快速充電。故430ms時(shí)計(jì)數(shù)器鎖定,1.8s時(shí)計(jì)數(shù)器解鎖。

延時(shí)電路中U7是電壓比較器芯片LM393,A/B兩單元構(gòu)成窗口比較器,當(dāng)C3極板電壓小于4V、大于2.5V時(shí),U6:B pin3輸出高電平。為了防止電路在C3充電時(shí)再度觸發(fā),引入另一個(gè)與門單元U6C,于是,只有在C3電壓介于2.5~4V之間,且脈沖限制電路處于不應(yīng)期時(shí),延時(shí)電路才輸出高電平。

由于電容放電時(shí)間較長(zhǎng),延時(shí)電路輸出高電平比前級(jí)電路滯后一些:

gra.2-2 延時(shí)電路輸出波形(紅線標(biāo)志)

這一滯后保證了鎖存器解鎖時(shí),計(jì)數(shù)器輸出值已經(jīng)穩(wěn)定,因此保證了LED陣列示數(shù)不會(huì)跳變。

變頻多諧振蕩器

diag.2-6 變頻多諧振蕩器原理圖

訂正:RV1阻值當(dāng)為2k

多諧振蕩器采用邏輯門方案,U4是四聯(lián)CMOS高速與非(NAND)門芯片,U4:A/B/C指其包含的三個(gè)與非門。

電路開始工作時(shí),由于SW1斷開。U4:A pin3必定處于高電平,故U4B pin4/5都處于高電平,故U4B pin6處于低電平,C1充電至下正上負(fù)。鑒于U4A pin2寄生電容充電時(shí)間極短,R1上很快無電流經(jīng)過,U4A pin2與C1下端等勢(shì),電位記為φ。

SW1閉合后瞬間,U4A pin1/2全為高電平,故pin3翻轉(zhuǎn)為低電平,U4B pin6翻轉(zhuǎn)為高電平。C1電荷不能立即釋放,故C1下端電位提升至2φ。U4A pin2很快又與C1下端等勢(shì),此時(shí)C1通過RV1、U4B放電,電勢(shì)能轉(zhuǎn)化為RV1上的熱能,C1、U4A pin2電勢(shì)不斷下降,直至低于芯片閾值0.5φ左右,此時(shí)U4A pin3翻轉(zhuǎn)為高電平,U4B pin6翻轉(zhuǎn)為低電平,C1下端電位降低至-0.5φ,又充電直至C1下端提升至0.5φ,U4A pin3又翻轉(zhuǎn)為低電平,如此反復(fù),形成振蕩。

gra.2-3 C1下端電位-時(shí)間曲線

gra.2-4 C1下端電位、U4B pin6電位-時(shí)間曲線

由圖可知,該芯片U4A pin2在上升沿、下降沿的閾值其實(shí)不同。不過我也懶得改前面寫的。

電路中RV1是電位器。改變RV1的阻值,可以改變C1充放電時(shí)間,即改變電路振蕩頻率。RV1取1kΩ、C1取1nF時(shí)計(jì)算頻率為369kHz,理論上RV1短路時(shí)電路頻率無窮大,但考慮到邏輯門延遲、下級(jí)電路的計(jì)數(shù)器延遲等因素,這種諧振器的頻率最高為2MHz。

-

發(fā)光二極管

+關(guān)注

關(guān)注

13文章

1211瀏覽量

66877 -

延時(shí)電路

+關(guān)注

關(guān)注

8文章

85瀏覽量

47330 -

鎖存器

+關(guān)注

關(guān)注

8文章

918瀏覽量

41907 -

CD4017

+關(guān)注

關(guān)注

10文章

99瀏覽量

49285 -

多諧振蕩器

+關(guān)注

關(guān)注

14文章

213瀏覽量

38051

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【assingle分享】labview隨機(jī)數(shù)發(fā)生器

【總結(jié)】LabVIEW隨機(jī)數(shù)發(fā)生器

一種基于FPGA的真隨機(jī)數(shù)發(fā)生器設(shè)計(jì)與實(shí)現(xiàn)

真隨機(jī)數(shù)發(fā)生器在信息安全系統(tǒng)中的應(yīng)用

如何制作方法簡(jiǎn)單的真隨機(jī)數(shù)發(fā)生器

怎么設(shè)計(jì)基于USB和FPGA的隨機(jī)數(shù)發(fā)生器驗(yàn)證平臺(tái)?

隨機(jī)數(shù)發(fā)生器的相關(guān)資料分享

學(xué)習(xí)筆記 | 基于FPGA的偽隨機(jī)數(shù)發(fā)生器(附代碼)

基于FPGA的真隨機(jī)數(shù)發(fā)生器設(shè)計(jì)

真隨機(jī)數(shù)發(fā)生器的容差分析

基于FPGA的偽隨機(jī)數(shù)發(fā)生器設(shè)計(jì)方案

【STM32】隨機(jī)數(shù)發(fā)生器詳解

FPGA的偽隨機(jī)數(shù)發(fā)生器學(xué)習(xí)介紹

基于多級(jí)反饋環(huán)形振蕩器的真隨機(jī)數(shù)發(fā)生器設(shè)計(jì)

如何在FPGA中實(shí)現(xiàn)隨機(jī)數(shù)發(fā)生器

評(píng)論