我一直以為SPI比IIC難的,因為可能是因為使用了比較“重型”的傳感器才會搭配這個接口。

但是今天用FPGA寫了一個簡單的移位寄存器,感覺不一樣,甚至是不對勁。

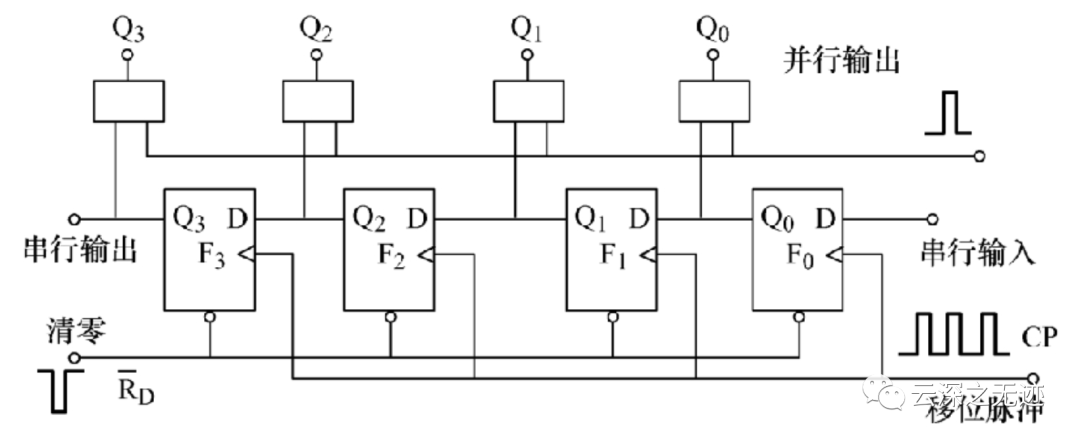

移位寄存器按照移位方向可分為左移位寄存器、右移位寄存器、雙向移位寄存器。

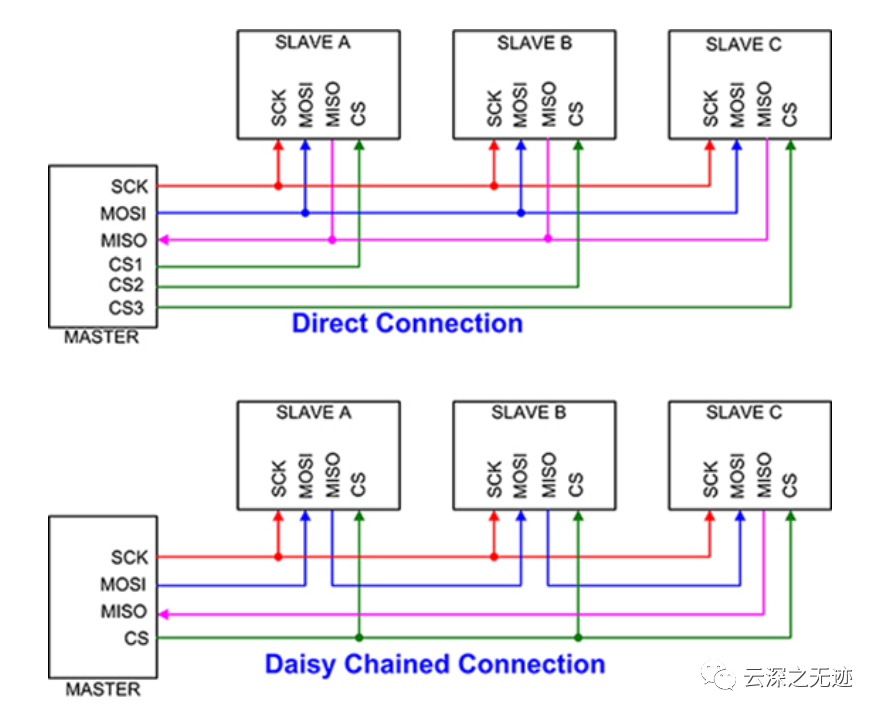

這個圖記住,菊花鏈也跑不了

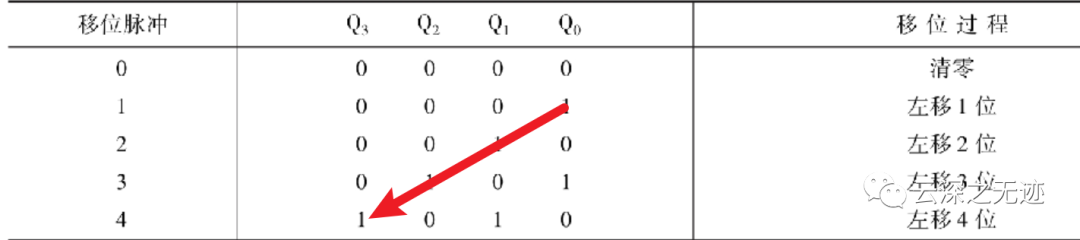

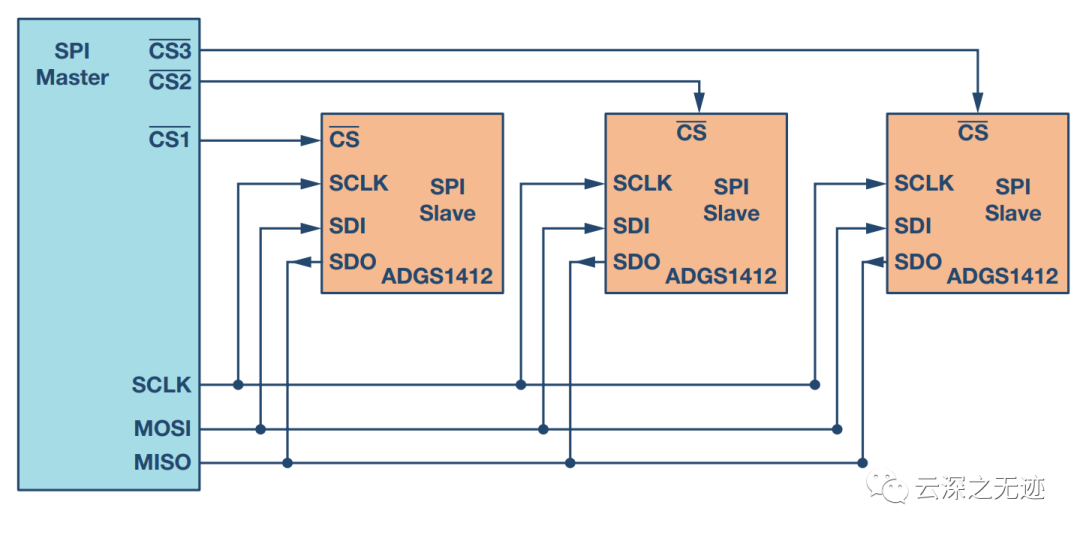

這個是STM32F103的主從設備的示意

MOSI腳相互連接,MISO腳相互連接。這樣,數據在主和從之間串行地傳輸(MSB位在前)。通信總是由主設備發起。主設備通過MOSI腳把數據發送給從設備,從設備通過MISO引腳回傳數據。這意味全雙工通信的數據輸出和數據輸入是用同一個時鐘信號同步的;時鐘信號由主設備通過SCK腳提供。

其實最近一段時間我頻繁在機器人系統里面,比如FPGA和ARM的控制核之間,發現它們之間的交互都是使用SPI。也就是說設計人員需要具有簡單的設備到設備數字接口的微控制器、外設和傳感器,以便可以高速處理任意長度的數據,并且省去與協議相關的復雜編程任務。

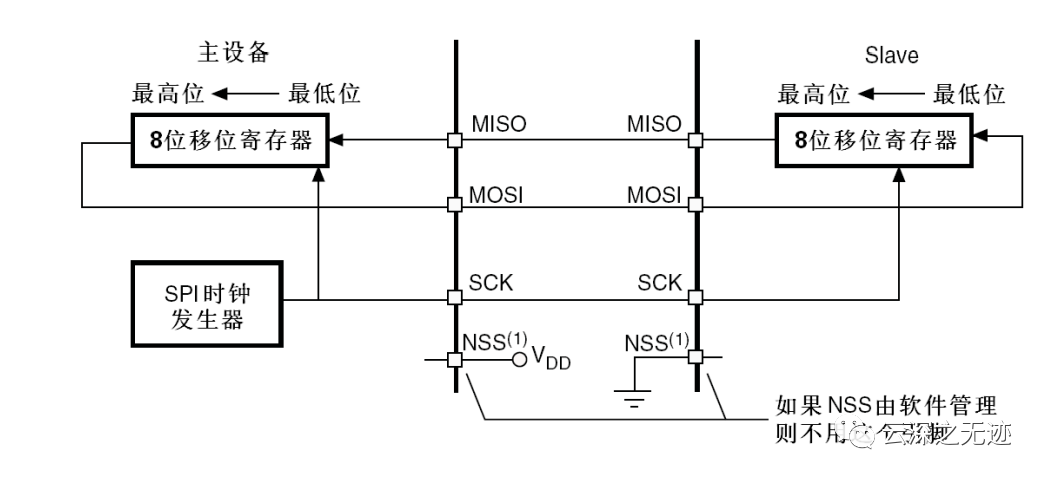

基本SPI全雙工連接使用兩條數據線(MOSI、MISO)、一條時鐘線 (SCK) 和一條片選線 (CS)。從設備上的MOSI有時標記為從設備數據輸入 (SDI)。MISO可標記為從設備數據輸出 (SDO)。

兩種處理多個從設備連接的配置。直接連接方式下每個從設備需要一個片選信號。菊花鏈連接方式僅使用一個片選信號,并將所有數據集中在一條線上。

主要看箭頭,多個從機

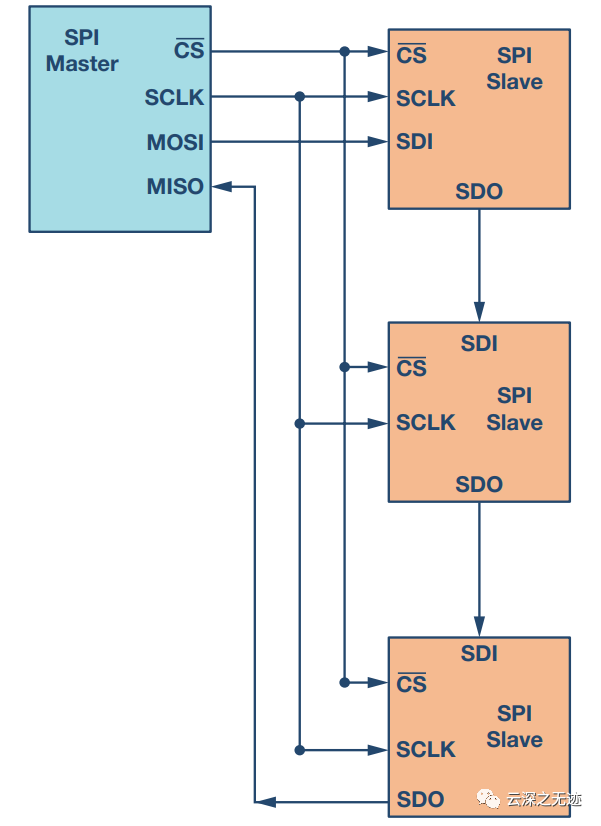

菊花鏈

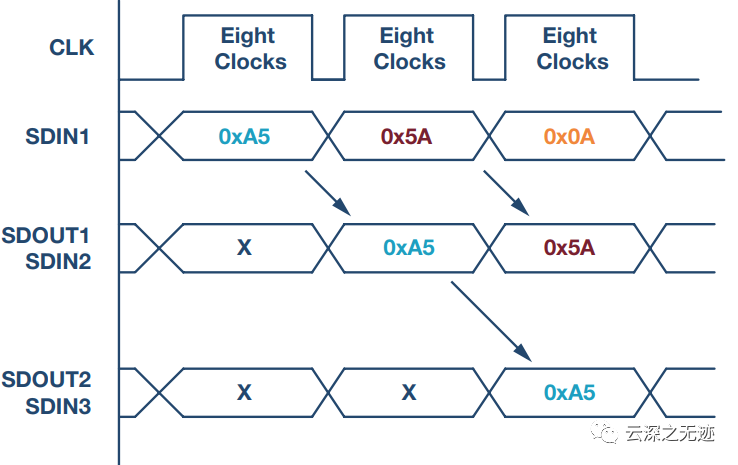

在菊花鏈模式下,所有從機的片選信號連接在一起,數據從一個 從機傳播到下一個從機。在此配置中,所有從機同時接收同一SPI 時鐘。

來自主機的數據直接送到第一個從機,該從機將數據提供 給下一個從機,依此類推。使用該方法時,由于數據是從一個從機傳播到下一個從機,所以 傳輸數據所需的時鐘周期數與菊花鏈中的從機位置成比例。

在圖所示的8位系統中,為使第3個從機能夠獲得數據,需要24個 時鐘脈沖,而常規SPI模式下只需8個時鐘脈沖。

一般Master設備就是我們的MCU,Master 設備會根據將要交換的數據來產生相應的時鐘脈沖(Clock Pulse),時鐘脈沖組成了時鐘信號(Clock Signal) ,時鐘信號通過時鐘極性 (CPOL) 和 時鐘相位 (CPHA) 控制著兩個 SPI 設備間何時數據交換以及何時對接收到的數據進行采樣,來保證數據在兩個設備之間是同步傳輸的。

SPI 設備間的數據傳輸之所以又被稱為數據交換,是因為 SPI 協議規定一個 SPI 設備不能在數據通信過程中僅僅只充當一個 "發送者(Transmitter)" 或者 "接收者(Receiver)"。

在每個 Clock 周期內,SPI 設備都會發送并接收一個 bit 大小的數據(不管主設備好還是從設備),相當于該設備有一個 bit 大小的數據被交換了。一個 Slave 設備要想能夠接收到 Master 發過來的控制信號,必須在此之前能夠被 Master 設備進行訪問 (Access)。所以,Master 設備必須首先通過 SS/CS pin 對 Slave 設備進行片選, 把想要訪問的 Slave 設備選上。

在數據傳輸的過程中,每次接收到的數據必須在下一次數據傳輸之前被采樣。如果之前接收到的數據沒有被讀取,那么這些已經接收完成的數據將有可能會被丟棄,導致 SPI 物理模塊最終失效。

因此,在程序中一般都會在 SPI 傳輸完數據后,去讀取 SPI 設備里的數據, 即使這些數據(Dummy Data)在我們的程序里是無用的(雖然發送后緊接著的讀取是無意義的,但仍然需要從寄存器中讀出來)。

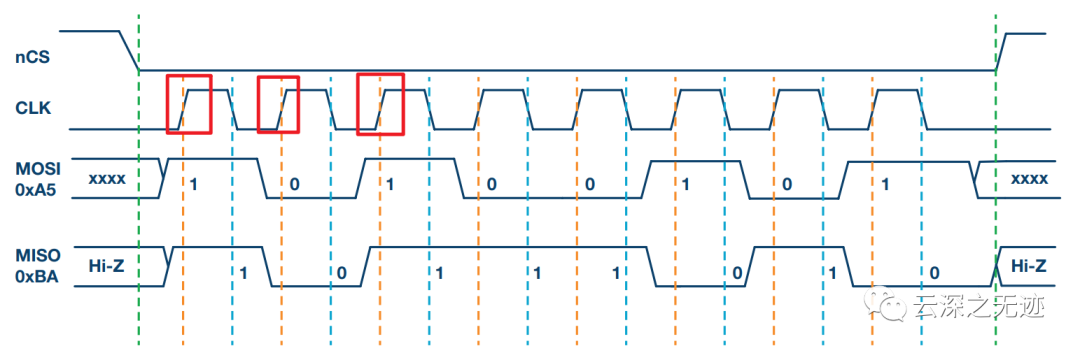

在SPI通信期間,數據的發送(串行移出到MOSI/SDO總線上)和接收(采樣或讀入總線(MISO/ SDI)上的數據)同時進行。

所以捏SPI沒有讀和寫的說法,因為實質上每次SPI是主從設備在交換數據。也就是說,你發一個數據必然會收到一個數據;你要收一個數據必須也要先發一個數據。

就像IIC一樣,SPI也是需要找到誰在通訊的,比較費引腳,必須有一個片選的腳。來自主機的片選信號用于選擇從機。這通常是一個低電平有效信號,拉高時從機與SPI總線斷開連接。當使用多個從機時,主機需要為每個從機提供單獨的片選信號。

要開始SPI通信,主機必須發送時鐘信號,并通過使能CS信號選擇從機。片選通常是低電平有效信號。

因此,主機必須在該信號上發送邏輯0以選擇從機。SPI是全雙工接口,主機和從機可以分別 通過MOSI和MISO線路同時發送數據。

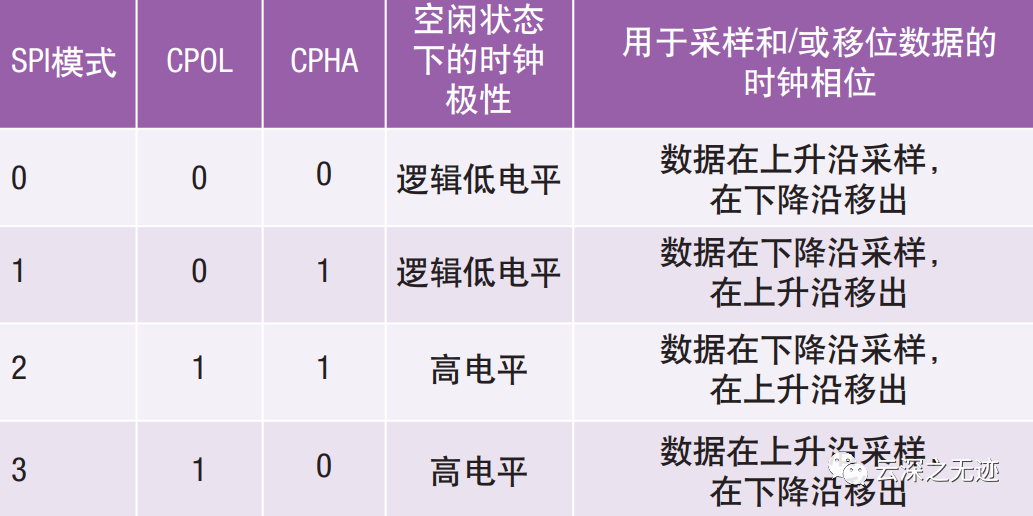

在SPI中,主機可以選擇時鐘極性和時鐘相位。

在空閑狀態期間,CPOL位設置時鐘信號的極性。空閑狀態是指傳輸開始時CS為 高電平且在向低電平轉變的期間,以及傳輸結束時CS為低電平且 在向高電平轉變的期間。

CPHA位選擇時鐘相位。根據CPHA位的狀態,使用時鐘上升沿或下降沿來采樣和/或移位數據。主機必須根據從機的要求選擇時鐘極性和時鐘相位。根據CPOL和CPHA位的選擇,有四種SPI模式可用。

數據顯示在MOSI和MISO線上。傳輸的開始和結束用綠色虛線表示,采樣邊沿用橙色虛線表示,移位邊沿用藍色虛線表示。

SPI模式0,CPOL = 0,CPHA = 0:CLK空閑狀態 = 低電平,數據在上升沿采樣,并在下降沿移出。

一采樣,一移位。

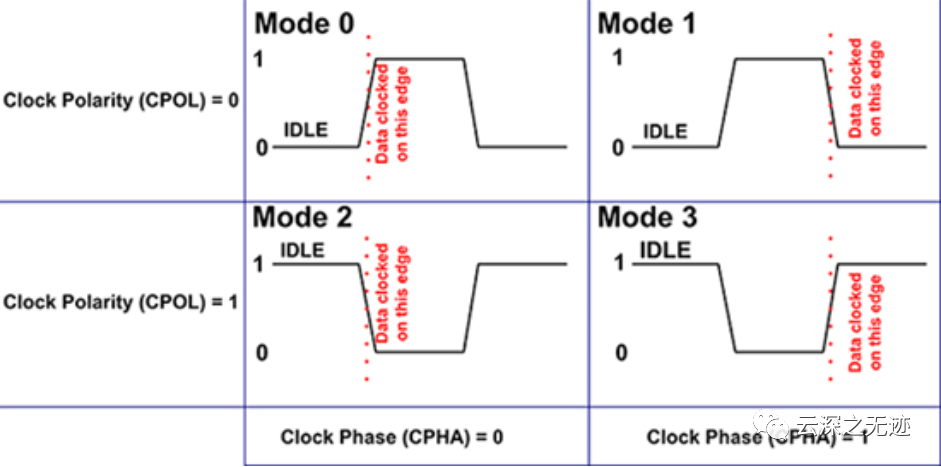

由主設備控制并生成時鐘。時鐘的兩個屬性分別是時鐘極性 (CPOL) 和時鐘相位 (CPHA)。這些屬性控制從設備相對數據進行計時的有效時鐘邊沿。CPOL = 0時,將時鐘設為在邏輯0位置空閑。CPOL = 1時,時鐘在邏輯1位置空閑。CPHA = 0時,數據在上升沿計時,CPHA = 1時,數據在下降沿計時(圖3)。

SPI時鐘模式選擇確定了進行數據采樣的有效時鐘邊沿。

主設備中的CPOL和CPHA線路設置決定了時鐘極性以及進行數據計時的有效邊沿。模式1是最常用的模式,但設計人員同樣可以使用其他三種模式。

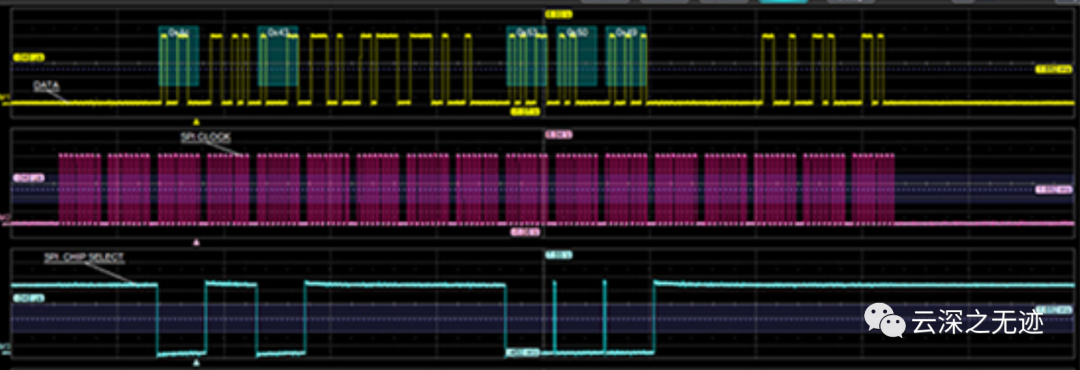

上面的軌跡是數據線,中間的軌跡是時鐘,底部的軌跡是片選信號。數據軌跡上的藍色覆蓋區顯示的是十六進制解碼內容。

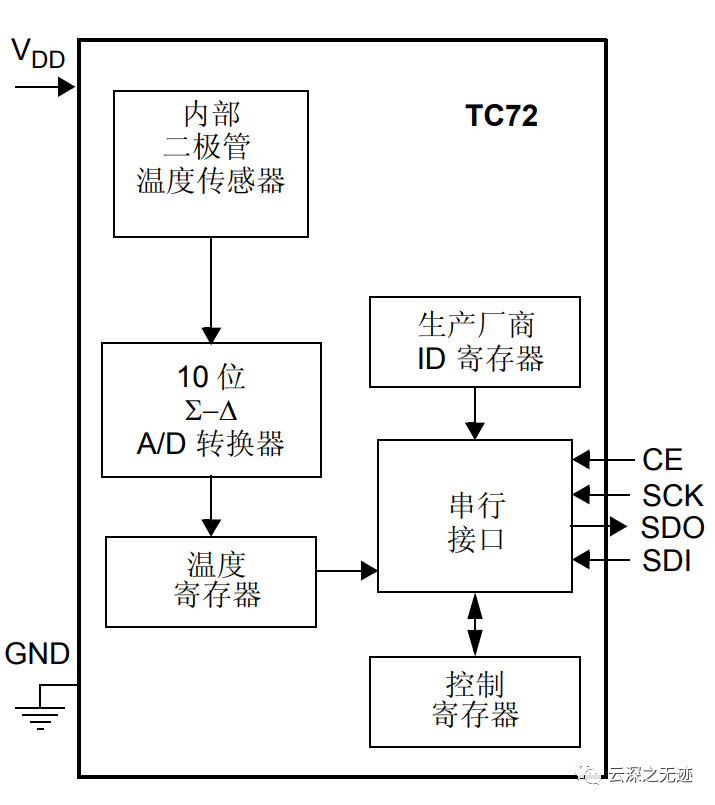

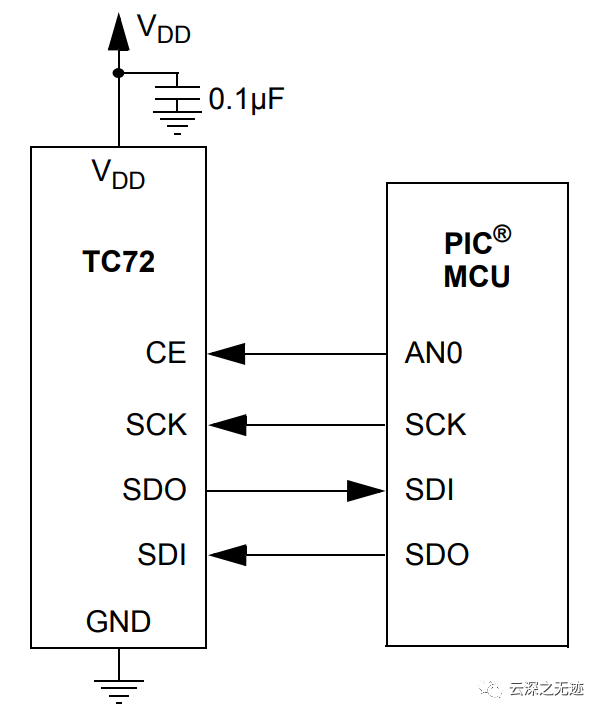

讓我來帶你看個MC的芯片手冊,看看不一樣的SPI。

一個SPI的溫度計

別問咋搞,直接街上

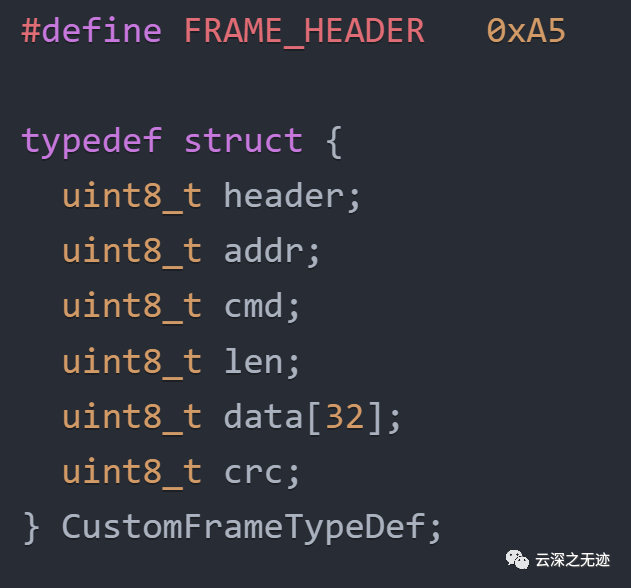

很多的時候,我們是使用傳感器直接寫,但是在機器人里面我們需要自己寫一個傳輸的協議,這個是后話。

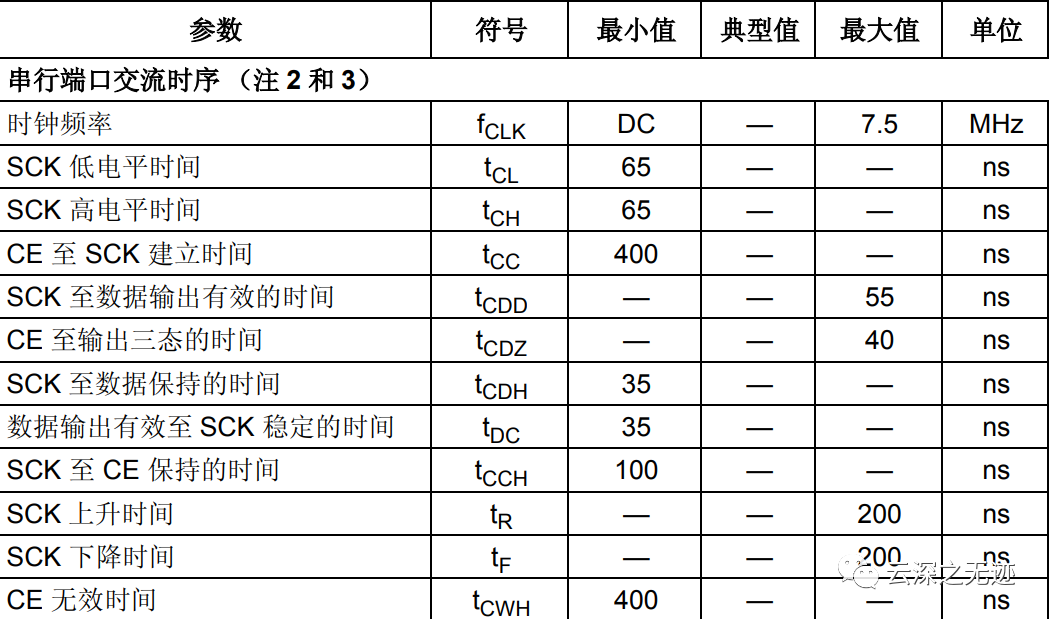

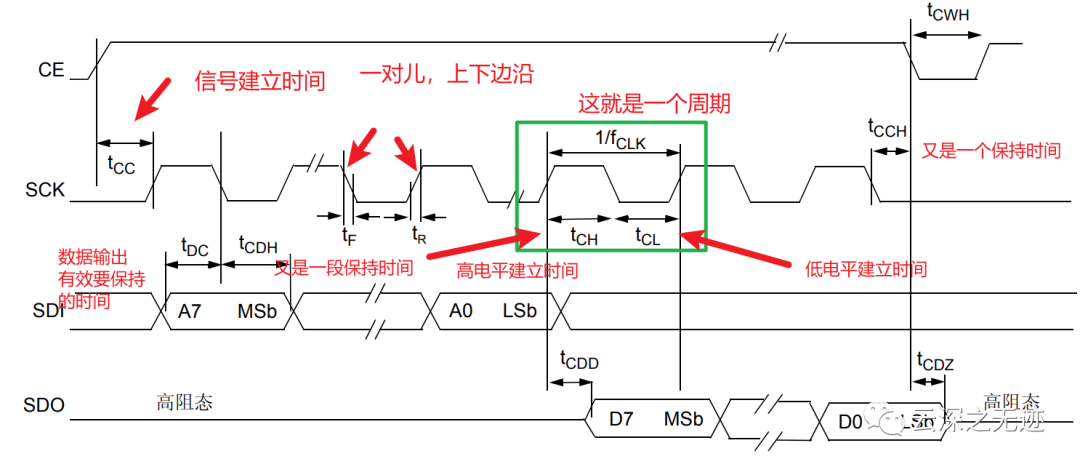

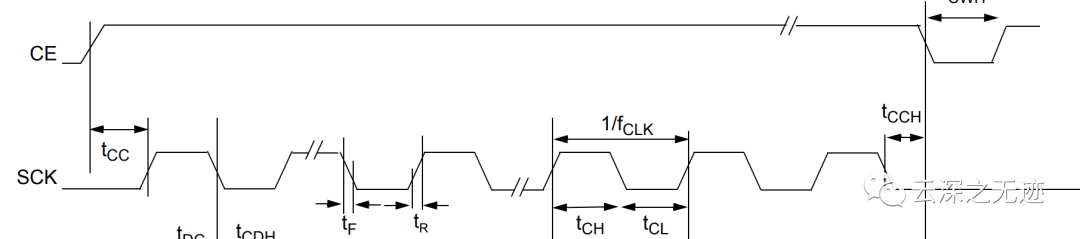

首先建立這些的時間都是ns級別,怎么說呢,俺說不明白。

說說這些東西的意思,我覺得是滿足不同人的需求,比如我現在就拿出一塊51,我就能輸出個高低電平,你能咋。

所以這些寫模擬協議的時候就有用,因為對于器件來說,我才不管什么東西插了我,反正說的通就行。

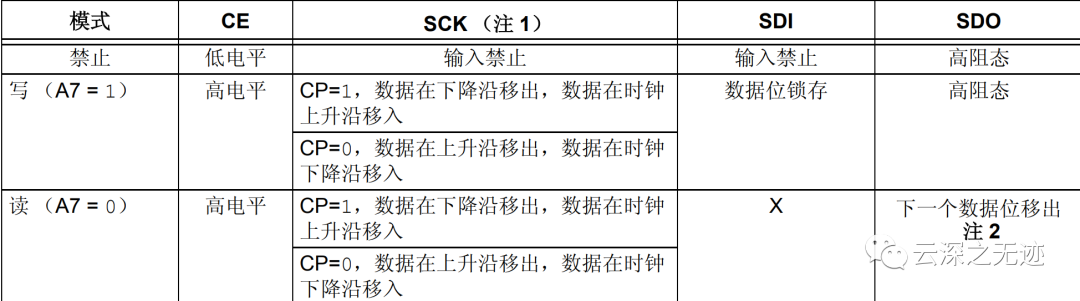

片選 (Chip Enable, CE) 、串行時鐘 (Serial Clock, SCK) 、串行數據輸入 (Serial Data Input,SDI)以及串行數據輸出(Serial Data Output, SDO )信號線。

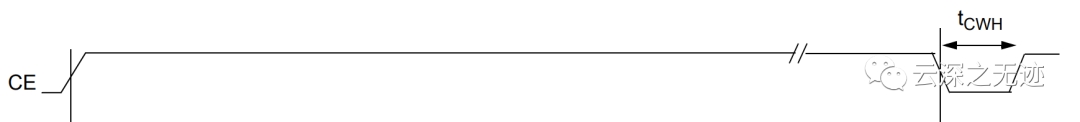

CE 輸入用于在有多個器件連接到串行時鐘和數據線時選擇器件。CE 為高電平有效,當 CE 等于邏輯高電平時,數據可以寫入器件或從器件讀出。CE 為低電平 時, SCK 輸入被禁止。

抬高的時候,就是到我啦!

CE 線的上升沿啟動讀或寫操作,而 CE 的下降沿結束讀或寫操作。

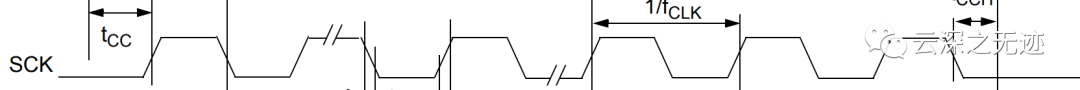

SCK 輸入由外部單片機提供,用于同步 SDI 和 SDO 線 的數據。

SDI 輸入向傳感器的控制寄存器寫入數據,而 SDO從溫度寄存器中輸出溫度數據和控制寄存器關斷位的狀態。

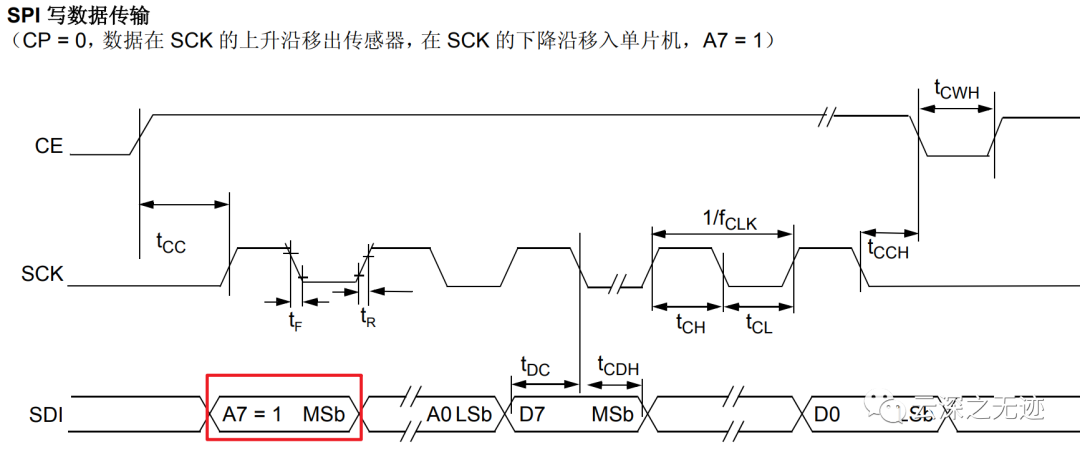

傳感器具有能在 SCK輸入信號為有效高電平或低電平時工作的能力。當 CE 信號變成高電平時,檢測到 SCK 的 無效狀態,而時鐘輸入 (CP)的極性決定數據是在系統時鐘的上升沿或下降沿移入或移出。

給出了用于傳送數據到寄存器和從寄存器移出數 據的相應時鐘邊沿。每個時鐘脈沖傳送一位數據,數據位以 8 位為一組傳送。

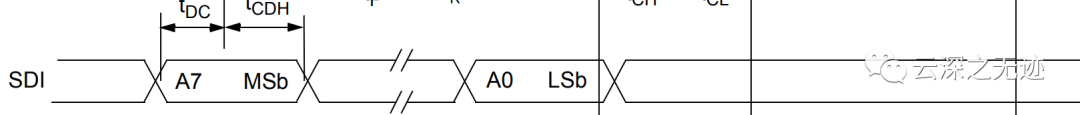

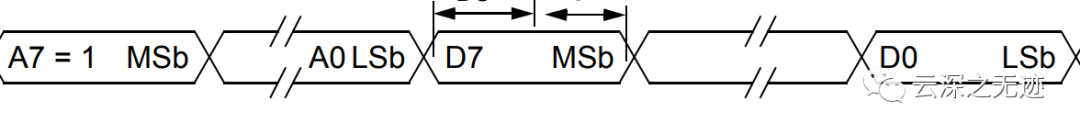

A就是地址

先發送地址字節,隨后為數據。地址的最高位 A7 決定 要進行讀操作還是寫操作。

如果 A7 =“0”,將進行一個或多個讀操作;否則 A7 = “1”,進行一個或多個寫操作。

地址+L+M

數據可以采用單字節或多字節包的方式進行傳送,如圖所示。在 3 字節包中,數據序列包括溫度數據的 MSb、溫度數據的 LSb 和緊接著的控制寄存器數據。通 過向寄存器寫入所需數據包的最高地址來啟動多字節讀功能。

這段有問題,我明天改正。

審核編輯:湯梓紅

-

傳感器

+關注

關注

2551文章

51134瀏覽量

753840 -

FPGA

+關注

關注

1629文章

21744瀏覽量

603607 -

寄存器

+關注

關注

31文章

5343瀏覽量

120426 -

接口

+關注

關注

33文章

8611瀏覽量

151236 -

SPI

+關注

關注

17文章

1707瀏覽量

91627

原文標題:嵌入式系統低速接口-SPI

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

嵌入式硬件通信接口協議中的串行通信接口-SPI

嵌入式系統低速接口SPI和UART的區別

嵌入式系統低速接口SPI講解

嵌入式系統低速接口SPI講解

評論