常見的FPGA核心電路可以歸納為五個部分:電源電路、時鐘電路、復位電路、配置電路和外設電路。下面將對各部分電路進行介紹:

1、電源電路

不同的FPGA器件、不同的應用方式會對電壓、電流有不同的需求。簡單歸納可以將FPGA器件的電壓需求分為三類:核心電壓、I/O電壓和輔助電壓。核心電壓是FPGA內部各種邏輯電路正常工作運行所需要的基本電壓,該電壓用于保證FPGA器件本身的工作。通常選定某一款FPGA器件則其核心電壓一般也是固定值,芯片手冊可查;I/O電壓即FPGA的I/O引腳工作所需的參考電壓。FPGA與ASIC最大的不同之處便是FPGA所有的可用信號引腳基本都可以作為普通I/O口使用,其電平值的高低完全由器件內部的邏輯決定,同時也受限于所供給的I/O電壓;除了核心電壓和I/O電壓以外的其他電壓便是輔助電壓。

2、時鐘電路

理想的時鐘模型是一個占空比為50%且周期固定的方波。一般情況下FPGA器件內部的邏輯會在每個時鐘周期的上升沿執行一次數據的輸入和輸出處理,而在兩個時鐘上升沿的空閑時間里,則可以用于執行各種各樣復雜的處理。FPGA器件的時鐘信號源一般來自外部,通常使用晶振產生時鐘信號,規模較大的FPGA器件內部會有專門的時鐘管理模塊用于對時鐘信號倍頻或者分頻,如PLL或DLL。同時在FPGA器件內部設計有“全局時鐘網絡”的走線池,用于控制到達不同寄存器的時間差。

3、復位電路

FPGA信號在上電之后需要有一個確定的初始狀態,以保證器件內部邏輯快速進入正常的工作狀態。因此需要一個內部復位的信號也即復位電路。阻容復位可以勝任一般的應用;而需要得到更穩定更可靠的復位信號,則可以選擇一些專用的復位芯片。FPGA器件往往有專門的復位輸入引腳。

4、配置電路

FPGA器件都支持JTAG進行在線配置。在FPGA器件內部,邊界掃描寄存器有TDI信號作為數據輸入,TDO信號作為數據輸出,形成一個很大的移位寄存器鏈。而JTAG通過整個寄存器鏈可以配置或者訪問FPGA器件的內部邏輯狀態或者各個I/O引腳的當前狀態。FPGA大都基于SRAM來實現可編程性,也即通過JTAG實現在線編程時正常接電FPGA能夠正常運行,一旦掉電,SRAM數據丟失則FPGA無法工作。所以FPGA通常需要外掛一個用于保存當前數據的PROM或者Flash芯片。

5、外設電路

FPGA擁有豐富的外設接口,可擴展性非常強,這也是很多用戶選擇它的原因。

審核編輯:湯梓紅

-

FPGA

+關注

關注

1629文章

21744瀏覽量

603606 -

電源電路

+關注

關注

48文章

998瀏覽量

65209 -

復位電路

+關注

關注

13文章

322瀏覽量

44599 -

時鐘電路

+關注

關注

10文章

236瀏覽量

50728

發布評論請先 登錄

相關推薦

FPGA實戰演練邏輯篇9:FPGA板級電路設計五要素

FPGA實戰演練邏輯篇16:FPGA核心板電路設計架構

例說FPGA連載9:FPGA板級電路設計五要素

例說FPGA連載10:能量供應——電源電路

OMAPL138 CPU核心電壓

FPGA的開發板與FPGA核心板的分別

FPGA板級電路設計的五要素

心電采集儀怎么有效抑制噪聲干擾?

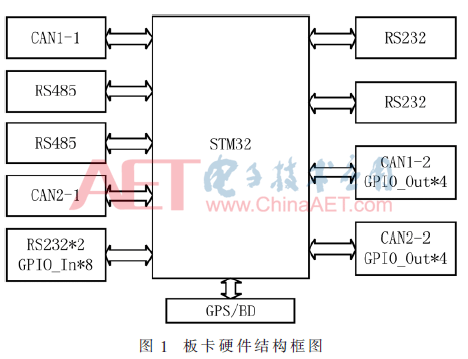

基于一種以STM32為核心電路的多源數據采集板卡設計

FPGA核心電路

FPGA核心電路

評論