通過數據路徑的逐步穿透,設計模塊,是一種常見的設計方法。而從另外一種常規思想來看,電路的另一種表現形式,是狀態的轉換。往往在設計有模式變換,且組合關系較復雜的電路時,使用狀態機描述電路,比數據路徑穿透的方法更加直接。

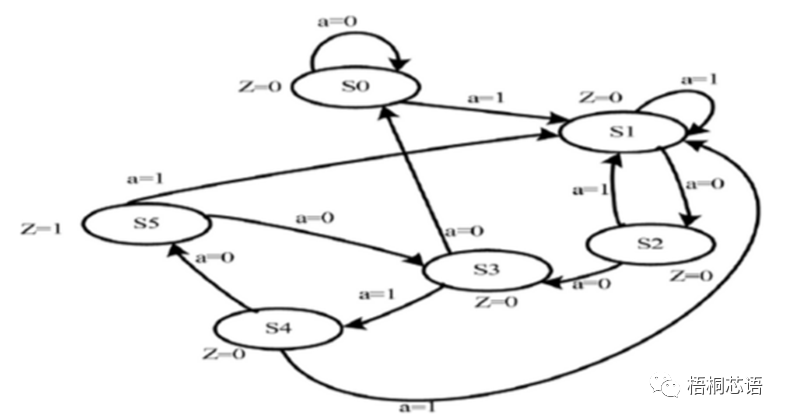

比如說,某個電路存在S0、S1、S2、S3、S4、S5六種狀態,電路上電后處于一個特定的狀態,只有當發生輸入變換時,才會切換到其他的狀態。這種電路,直觀上無法用數據路徑穿透設計,但如果使用狀態機設計,則會簡單很多。

狀態機設計,一般先把3種類型的信號(狀態)整理出來:

- 狀態信號,表示當前狀態機處于什么狀態下

- 條件信號,狀態機在不同條件下的跳轉,需要不同的信號

- 輸出信號,根據狀態的不同,輸出相應的結果

接著就可以把狀態機的狀態變化描述圖整理出來,如下圖所示:

以上狀態機的狀態信號一共6種,S0~S5,而條件信號為a。可以看出不同狀態下,a的變換決定了狀態的下一次跳轉會向哪個方向跳。這里有2個必須理解的點:

- a沒有變換的時候,無論多少個時鐘信號,狀態都會保持不變

- a的到來應該是脈沖型信號(單個時鐘周期),以確保狀態的變換是按照時鐘周期進行的。

Z則是輸出信號,在不同狀態下,其輸出會有所不同。

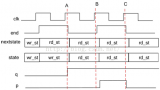

根據以上狀態圖的描述,我們可以開始用Verilog HDL進行電路描述了(狀態機跳轉圖,可視為電路圖)。一般的狀態機描述,我們稱為三段式描述,實際上就是剛才說的,分別對三種不同信號的描述。

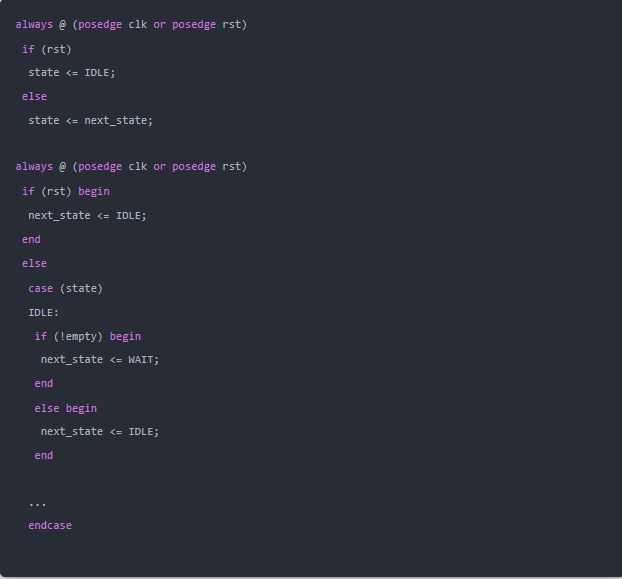

第一部分是狀態跳轉的描述,采用時序邏輯與組合邏輯分離的描述方式,將狀態信號看成寄存器:

以上狀態的定義,使用的是順序編碼,如果根據實際情況,采用格雷碼設計,跳轉頻率高的盡量減少跳轉,則可以相應減少一些功耗。

接著第二部分,描述條件對狀態的影響,屬于組合邏輯,一般來說我們用case語句結構來實現,需要注意的是,必須加上default條件,其實就是說其他條件不滿足的話,nextstate就保持在上一個狀態。如果沒有default語句,且條件不完整,則synthesis工具會生成一個鎖存器來實現case語句,那樣的話,與我們的設計初衷就不同了,要避免:

條件語句,其實也可以用數據路徑來設計,但那樣的話就會有優先級出現,需要根據實際情況來分析。

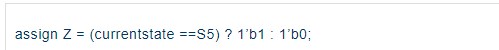

第三部分,就是根據狀態的變換,為輸出值Z賦值。根據狀態圖分析,只有處于S5的時候,Z才輸出1'b1,否則都是1'b0:

所以輸出仍然可以使用數據路徑描述方式。

由此三段式描述狀態機的方式,就完成了。至于條件a怎么來的,輸出Z又給到哪里去了,該如何進一步的設計,就需要各位看官自己吸收理解了。

-

寄存器

+關注

關注

31文章

5357瀏覽量

120685 -

變換器

+關注

關注

17文章

2101瀏覽量

109377 -

鎖存器

+關注

關注

8文章

906瀏覽量

41554 -

狀態機

+關注

關注

2文章

492瀏覽量

27578 -

HDL語言

+關注

關注

0文章

47瀏覽量

8936

發布評論請先 登錄

相關推薦

狀態機的設計方法和三段式描述

狀態機的設計方法和三段式描述

評論