MOSFET器件是數字集成電路的最小單位,因為MOSFET的開關特性和輸出曲線特性,由PMOS和NMOS組成的CMOS門電路,則為數字集成電路最基本的電路結構。而想很好地理解CMOS電路結構,必須先熟悉CMOS反相器電路及其設計和分析方法,因為其他門電路,很多分析方式都是相通的。

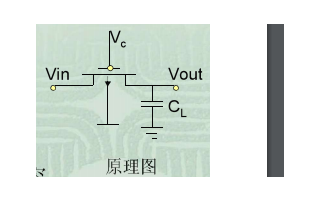

原理圖與版圖

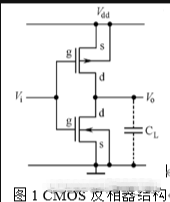

下圖所示是CMOS反相器電路的原理圖以及物理版圖。物理版圖就可以理解為MASK的圖形,之前的章節中,我們已經知道,集成電路制造就是根據圖形一層一層光刻、生長、注入而實現的,所以無論是什么電路圖,最終都必須轉換成物理版圖的圖形,交到工廠去生產。

當然因為知道生產出來的電路,是一層一層堆疊的,所以CMOS反相器電路實際剖面圖如下所示。

正常來說VDD與VBBp會連接在一起,接在VDD上,是PMOS的源端,而VBBn與GND會連接在一起,接在地上,是NMOS的源端。當然隨著工藝尺寸逐步降低,VBBp和VBBn不會與每一個門電路的VDD和GND連接,而是每幾個電路連接一個門電路,這樣做的好處是,節省面積,但因此會造成襯底偏置電壓(VBS,Substrate Biasing Voltage,偏置與襯底的電壓差)與源端產生少許電壓差,改變閾值電壓VT。一般來說VBS與VT成反比關系,也就是說VBS越大,VT越小,VBS越小VT越大。

對于數字集成電路工程師來說,知道襯底偏置電壓對VT有影響影響就好,不需要了解太多了。因為在先進工藝下,為了做好低功耗設計,有專門的Body Biasing Generator(BBG)來微調偏置電壓,以便獲得功耗與性能之間的取舍。降低VT可以提高性能,但帶來較大漏電;提高VT可以減少漏電,但會提高性能。

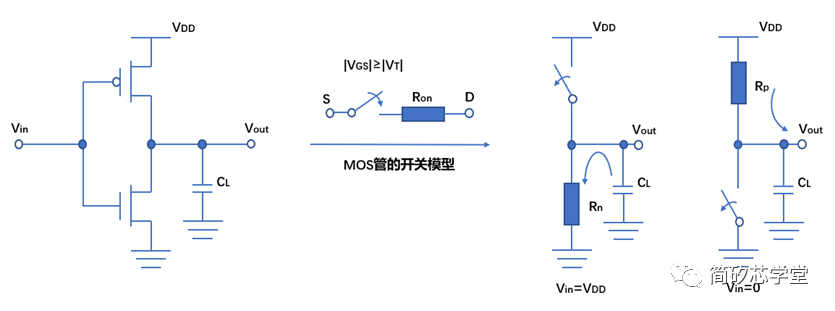

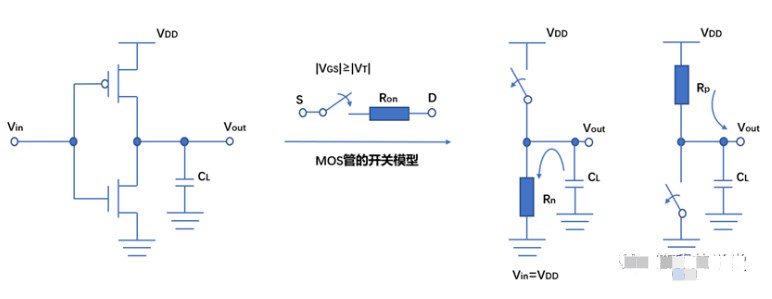

首先看CMOS反相器的電路,與之前不同的是,多了一個CL,負載電容。無論是什么CMOS門電路,其輸出一定是要驅動一個負載的,而對于CMOS門電路來說一般負載指的是金屬連線與地之間的電容,以及下一級電路輸入柵極與地之間的電容。因為MOSFET是電壓控制電流,如果把負載電壓VDD看成邏輯1,地電勢看成邏輯0,那么只是電流是無法實現邏輯傳遞的,因此負載電容在被電流充電與放電的過程中,完成其節點在VDD與地電勢之間跳變,才能真正把邏輯數值傳遞出去。

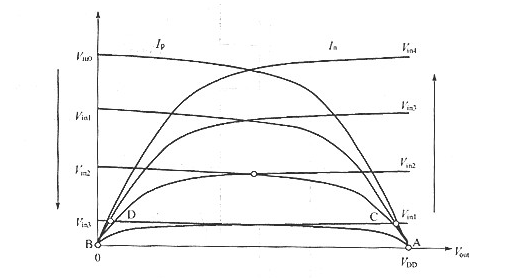

假設PMOS和NMOS使用相同的VT值,則輸入電壓改變引起輸出電壓變化的曲線(反相器轉移特性曲線)圖如下:

- A區域,Vin在0V到VTN之間,因此NMOS截止,PMOS非飽和,但沒有電流通路,因此沒有電流,輸出電壓也不會發生變化。

- B區域,Vin在VTN到1/2VDD之間,NMOS處于飽和狀態,PMOS處于非飽和狀態,對于PMOS來說,VDS不大,因此電流不大,電容放電速度比較慢。

- C區域,Vin在1/2VDD左右,NMOS和PMOS同時處于飽和狀態,放電速度突然增大,對于PMOS來說,很快達到飽和狀態(VDS增加),而NMOS很快達到非飽和狀態(VDS減少),進入D區域。

- D區域,Vin處于1/2VDD到接近(VDD-VTP)區間,NMOS處于非飽和,PMOS處于飽和狀態,對于NMOS來說,VDS不大,因此電流不大,電容放電速度較慢。

- E區域,Vin大于VDD-VTP,PMOS截止,沒有電流通路,輸出電壓也就固定在0V。

由以上特性可見,當輸入電壓為VDD的時候,輸出電壓為0V,而輸入電壓為0V時,輸出電壓為VDD,剛好相反,滿足反相器的邏輯關系。

接著我們看一下,輸入電壓與電路電流的關系:

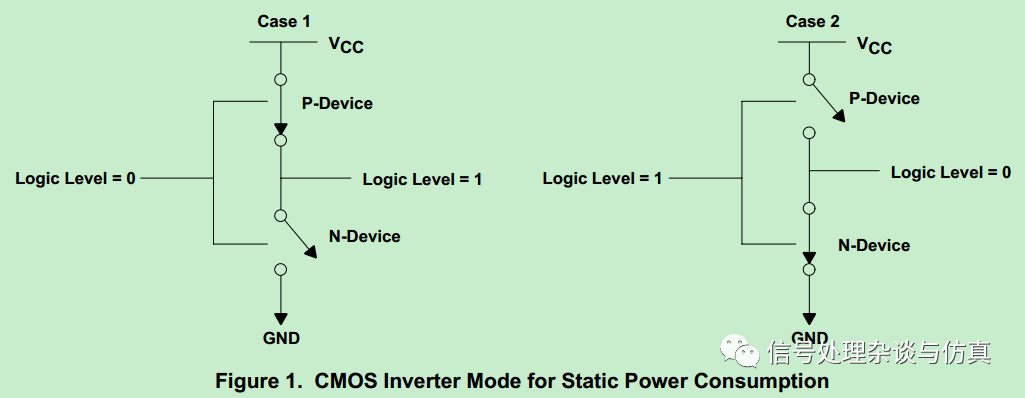

可以看出,只要輸入電壓小于nMOS的VT,或者大于VDD-|VTP|,則電路是不會產生電流的。只有在這中間區間,才會產生一個比較大的電流,特別是兩個管子都處于飽和狀態時。這樣的好處是只要電路不發生翻轉,就不會產生電流,而一旦發生翻轉,因為nMOS和pMOS的互補性,會快速實現狀態轉換,提高性能。

影響CMOS反相器特性的因素

除電源電壓外,影響反相器特性的主要有:

- NMOS和PMOS管的閾值電壓;

- NMOS的W/L和PMOS管的W/L;

- NMOS和PMOS管W/L值之比。

剛才的分析是假設nMOS和pMOS的閾值電壓一樣,但實際上可能會有偏差,如果閾值電壓不同,則會影響轉換曲線的偏移,畢竟開關的時間都不一樣了,但峰值電流不會有太大變化,也不會對充電時間有太大影響。當然實際設計的時候,我們盡量讓兩個管子的閾值相近,以便轉換過程盡可能接近于中心位置,減少對噪聲容限的影響。

同時閾值越小,中間階段越大,短路狀態也會持續越長的時間。輸出曲線斜率越平緩,輸出變化越慢。如果想減少短路狀態下的能量損耗,需要選擇VT值大一些的器件,當然對電容充電時間減少了,性能也會降低。

另一個方面,如果兩個管子寬長比越大,則電流越大,等效電阻越小,跨導越大,傳輸效率越高,對負載充電的性能越高,當然2個管子都處于飽和狀態時,電流也會越大。想獲得更快的工作頻率,更大的寬長比選擇是有必要的。

第三點,寬長比之比,是很有意思的。假設當pMOS的寬長比與nMOS寬長比是2:1的時候,傳輸曲線最陡峭的位置處于1/2 VT的位置,這是最理想的結果。

那么如果我們增加pMOS的寬長比,則曲線就會向右偏移,這意味著如果輸入電壓在VDD范圍不穩定時,輸出電壓可能發生變化,也就是偏向于VDD的噪聲容限減小了。同樣的,如果我們減小pMOS的寬長比,則曲線就會向左偏移,這意味著如果輸入電壓在地范圍不穩定,被抬升時,輸出電壓可能發生變化,也就是偏向于地的噪聲容限減小了。

為什么要用CMOS結構電路

這是一個比較奇葩的問題,因為現在已經很少,或者說在數字集成電路設計過程中,已經不會再有人問這個問題了。但是作為入門工程師來說,了解一下歷史,可以更好地展望未來。

首先我們要知道一個好的反相器應該有以下4個特質:

- 電壓擺幅:接近電源電壓好

- 高增益區電壓增益:越高越好

- 靜態電流:越小越好

- 直流噪聲容限:越大越好(轉換電平居中)

現在我們回到遠古時期,看看老古董都是什么樣子的。

有興趣的小伙伴可以把4種中古反相器都分析一下,我們這里只詳細分析以下電阻負載反相器,也就是利用電阻替代pMOS來對電容進行充電。

圖中Source與GND直接連接,因此Source電壓Vs=0;Gate上的電壓Vg就是是Vin,Drain上電壓就是Vout。因此Gate與Source電勢差Vgs=Vg-Vs=Vin-0=Vin,Drain與Source電勢差Vds=Vd-Vs=Vout-0=Vout。

Vgs<=VT時,NMOS不導通,電路沒有電流,因此Vout=VDD。

Vgs>=VT后,電路產生電流,CL開始放電,但由于VCC與Vout之間因為電阻的原因一直有通路,因此CL通過NMOS放電的同時,還會有一定的充電,Vout無法達到0V。輸入與輸出關系曲線如下圖所示:

可以看出,電阻負載反相器,在輸出邏輯0的時候,是無法達到0V的,有一個小的電壓,且同時電路中存在電流。根據好的反相器標準,電阻負載反相器電壓擺幅無法達到0V,且存在靜態電流。電阻越大,電流越小,且約接近于0V。但電阻的噪聲隨著頻率增加,是無法被接受的,除了本身性能不好外,隨著性能的要求,電阻負載反相器一定會被淘汰。

那么這些中古反相器和CMOS反相器差別的對比,如下圖所示,如果理想的反相器是目標,只有CMOS反相器是最接近于這個目標的。

反相器的直流參數

之所以說反相器的分析非常重要,是因為在芯片中反相器的應用,除了作為邏輯電路外,還會作為增大驅動能力的IO Buffer以及放大器基礎結構(放大器電路不是數字集成電路設計必須學習的)。

所以反相器的直流參數就尤為重要了,會看芯片datasheet的小伙伴應該很容易理解這些參數。

首先是VIL和VIH,分別是輸入低電平的最高值以及輸入高電平的最低值,這意味著如果給一個芯片送信號(假設芯片IO輸入是一個buffer),那么輸入的信號只有穩定在VIL以下以及VIH以上,才能夠被正確的識別到。

問題回到pMOS和nMOS的寬長比之比,小伙伴們可以思考一下,如果修改寬長比之比,對于VIL和VIH有什么影響呢?

VOL和VOH分別指輸出低電平的最高值,和輸出高電平的最低值。如果是中古反相器Buffer,那么輸出值就會與地和供電電壓VDD有一些不同,但在當今CMOS結構的電路中,基本上就是地電勢和供電電壓VDD。

VNL和VNH分別指輸入低電平抗干擾以及輸入高電平抗干擾,在保證輸出電平不變的條件下,輸入電平允許波動的范圍。它們表示門電路的抗干擾能力,這兩個值當然越大越好。VNH可以理解為驅動門的VOH-負載門的VIH,而VNL可以理解為負載門的VIL-驅動門的VOL。

所以如果要提高VNH和VNL,那么就需要盡量讓VOH和VOL接近于VDD和0V(CMOS電路驅動時,輸出擺幅滿足此要求,但連線過長,寄生電阻可能產生的壓降就會降低VOH或太高VOL,實際電路時要注意這一點),而VIH和VIL盡可能的接近于中心位置。也就是說約接近于理想反相器,那么VNH和VNL越大。

回憶一下,影響CMOS反相器特性的因素,現在可以理解,為什么我們盡量使用更大的VT值,以及配比PMOS和NMOS的寬長比,使其傳輸曲線的中心電壓處于1/2 VDD的位置了。

反相器設計如此,其實后續我們接觸到的門電路設計都會因為VNH和VNL的需要,都會希望傳輸曲線都能盡可能地靠近1/2 VDD。

-

CMOS

+關注

關注

58文章

5851瀏覽量

237149 -

MOSFET

+關注

關注

148文章

7711瀏覽量

216324 -

反相器

+關注

關注

6文章

314瀏覽量

43799 -

負載電容

+關注

關注

0文章

141瀏覽量

10626 -

PMOS管

+關注

關注

0文章

84瀏覽量

6884

發布評論請先 登錄

相關推薦

virtuoso中進行CMOS反相器和靜態寄存器的電路設計

MOS反相器和CMOS反相器的詳細資料說明

什么叫CMOS電流源(漏)反相器?它有什么優點?

為什么可以用CMOS反相器作為邏輯門電路緩沖級?

影響CMOS反相器特性的因素

TTL反相器和CMOS反相器的區別

CMOS反相器的工作原理和應用

評論