Versal器件不再有傳統(tǒng)的SEM IP;Soft Error Mitigation功能在Vitis套件中以library形式出現(xiàn),稱為XilSEM。XilSEM基本功能和之前的SEM IP類似:通過(guò)不斷地掃描,檢測(cè)出PL CRAM中出現(xiàn)的SEU翻轉(zhuǎn),上報(bào),再根據(jù)系統(tǒng)需要決定是否做糾正或者重新配置PL。根據(jù)Versal器件的特點(diǎn),XilSEM的掃描范圍進(jìn)一步擴(kuò)大,還可選擇是否掃描NPI寄存器,對(duì)PL之外的其他功能模塊的配置數(shù)據(jù)做監(jiān)測(cè)。

這篇文章介紹了如何開(kāi)啟Versal最基本的XilSEM功能。

Vivado/Vitis 2022.1

Board used: VCK190

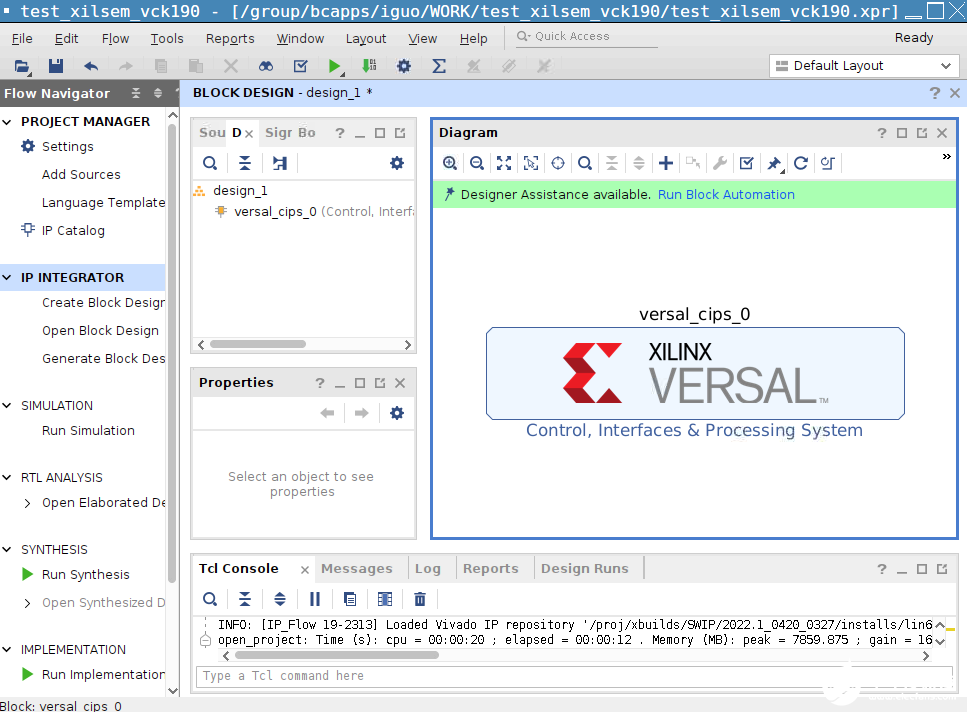

1. 首先基于VCK190開(kāi)發(fā)板,建立一個(gè)project. 創(chuàng)建Block Design并添加CIPS IP:

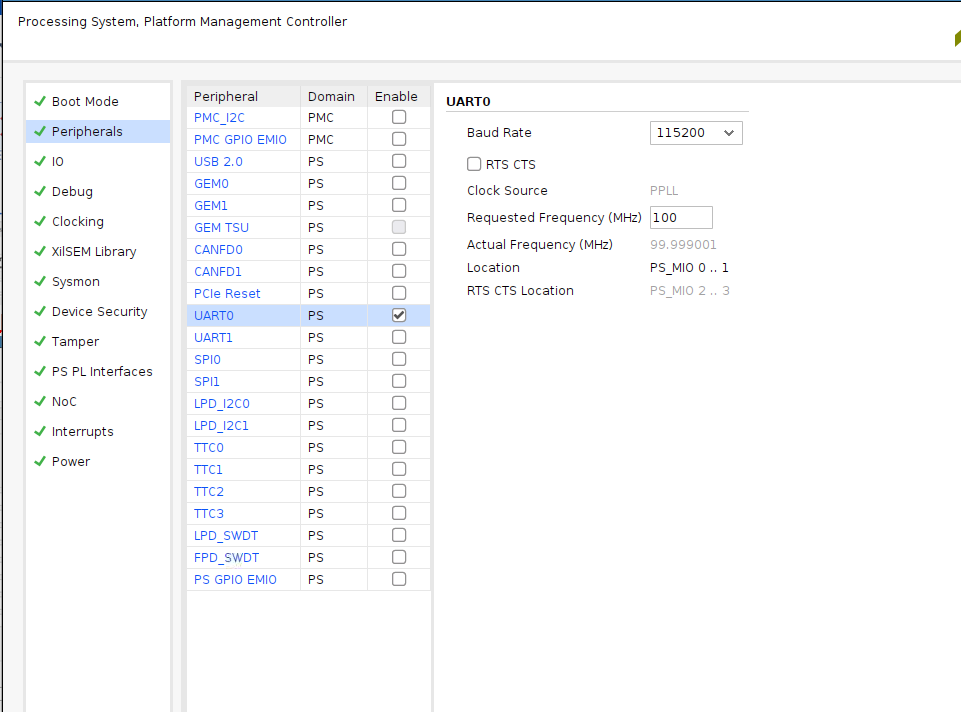

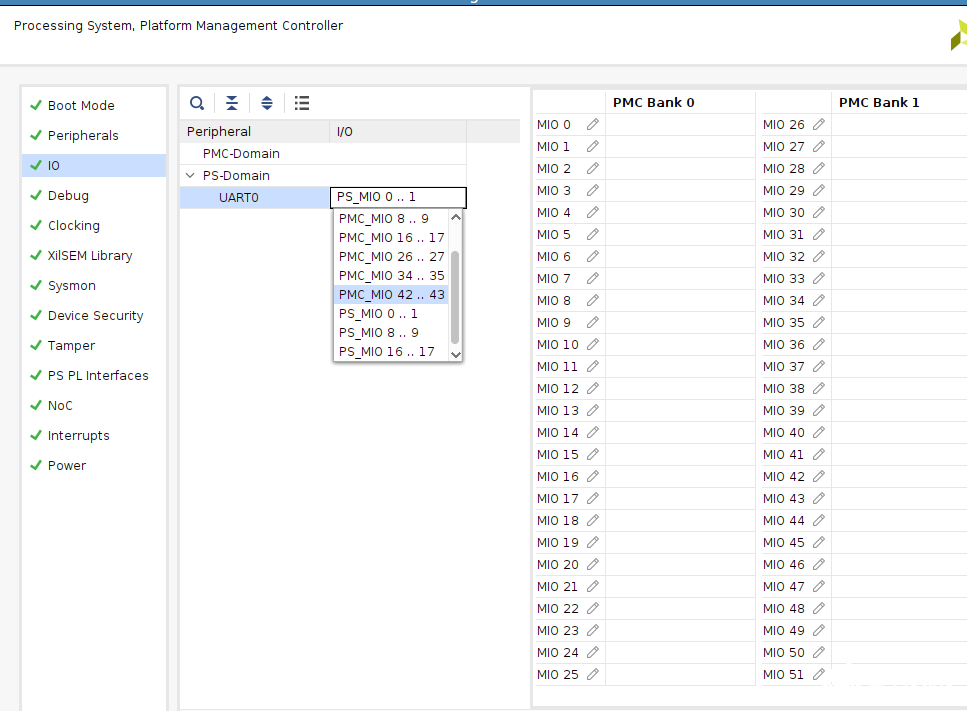

按照下圖配置PS PMC,使能串口以輸出XilSEM的log:

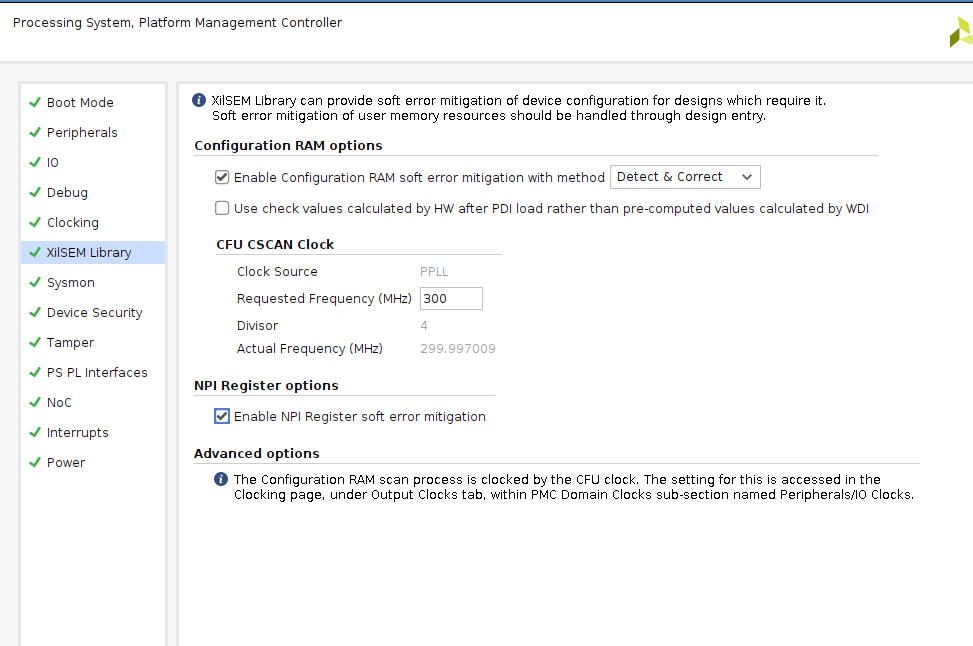

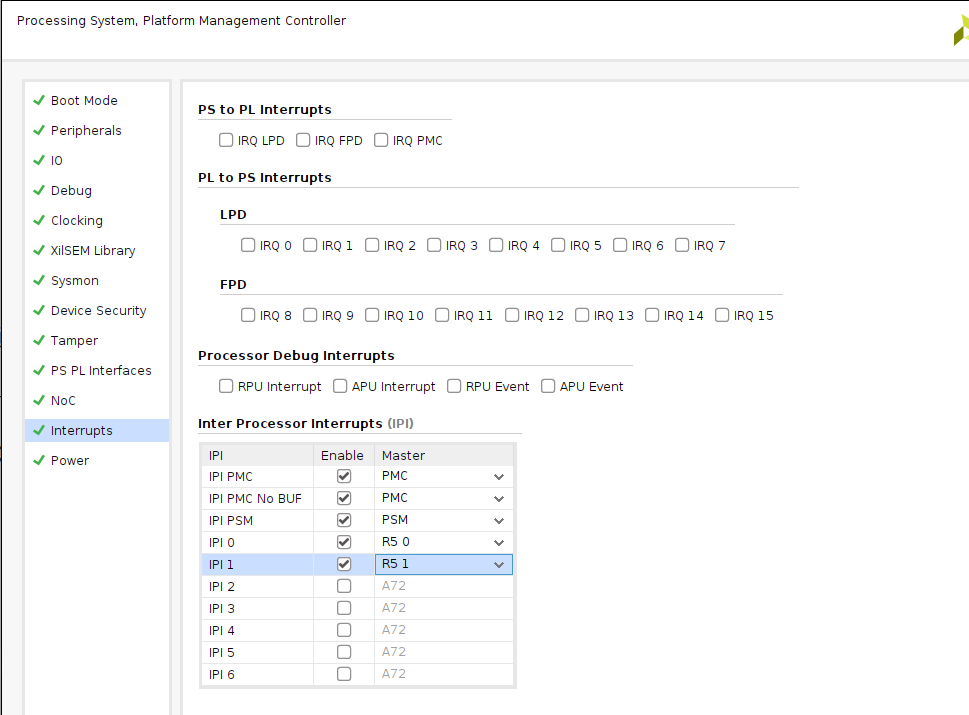

從左側(cè)選項(xiàng)中找到并使能XilSEM庫(kù),并添加中斷:

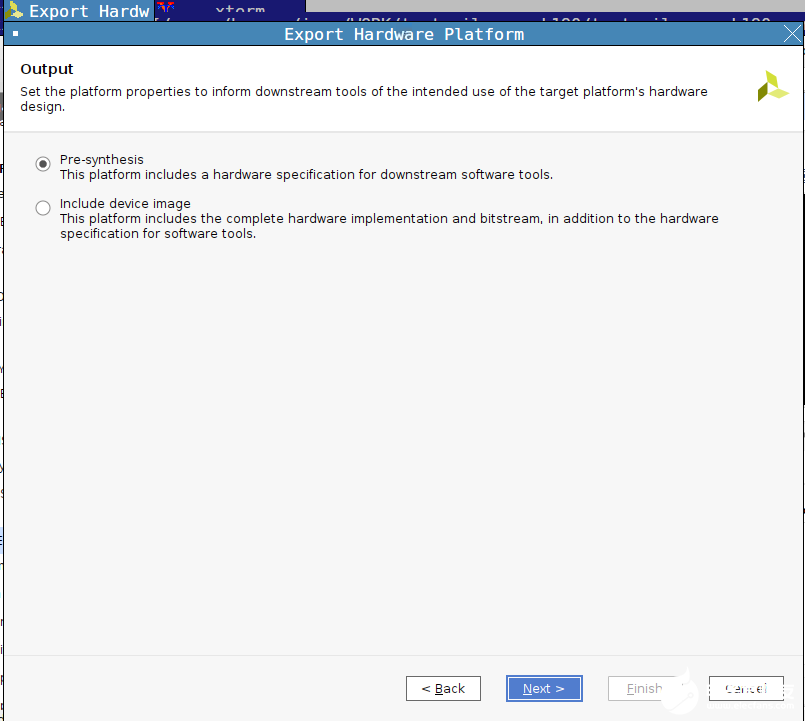

生成HDL Wrapper以及pdi文件,并將設(shè)計(jì)導(dǎo)出到Vitis中。導(dǎo)出時(shí),選擇‘Pre-synthesis’或‘Include device image’均可。

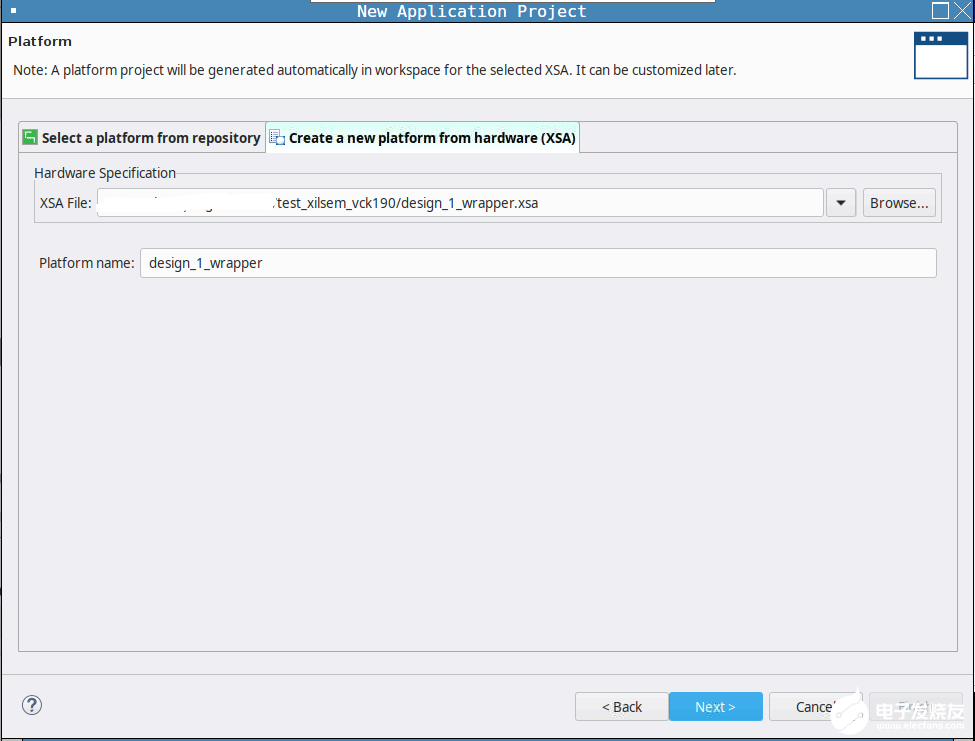

2. 打開(kāi)Vitis,基于之前生成的.xsa,建立一個(gè)新的application工程:

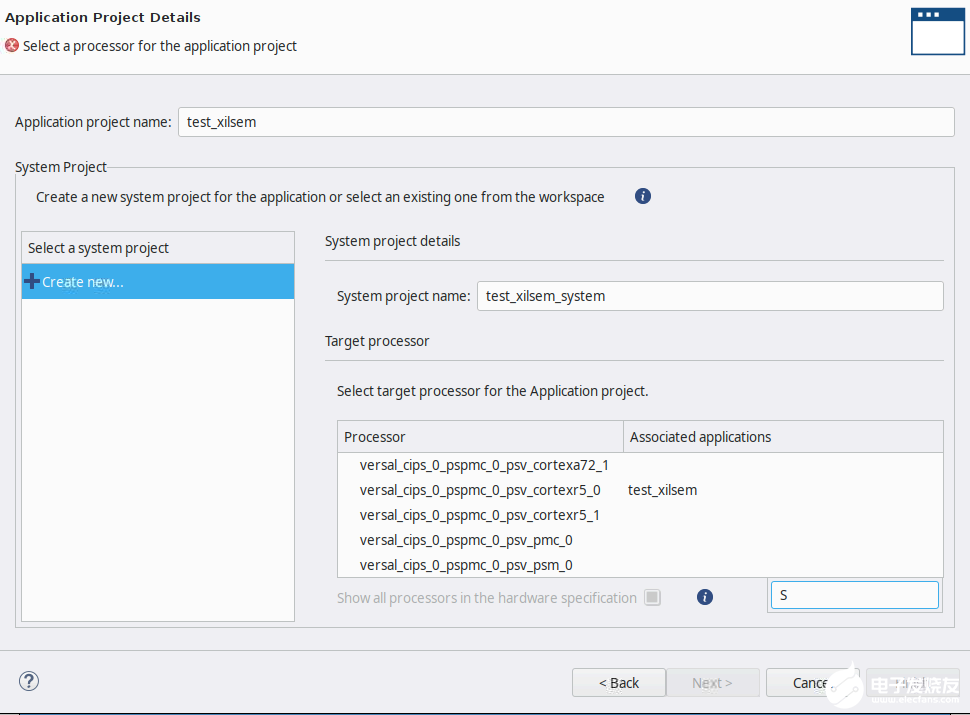

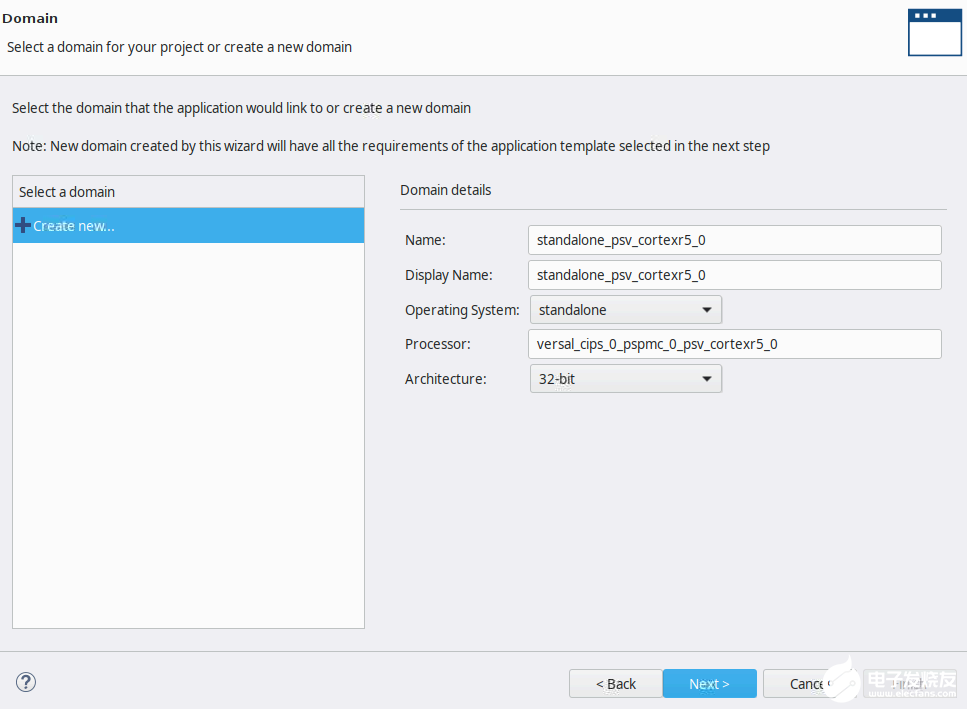

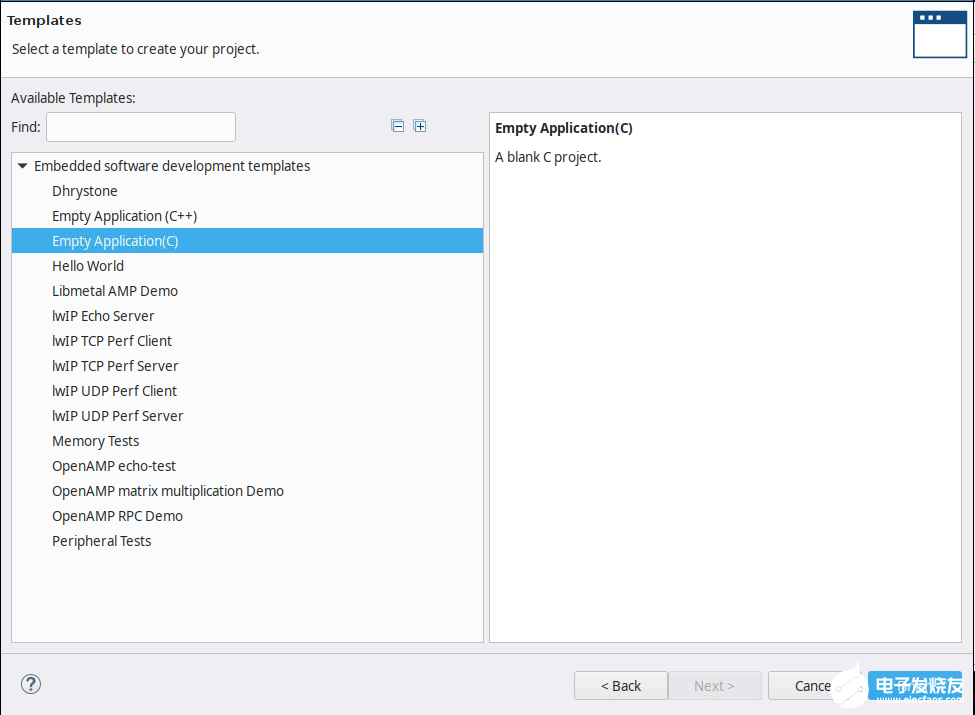

基于R5,建立一個(gè)空白Application:

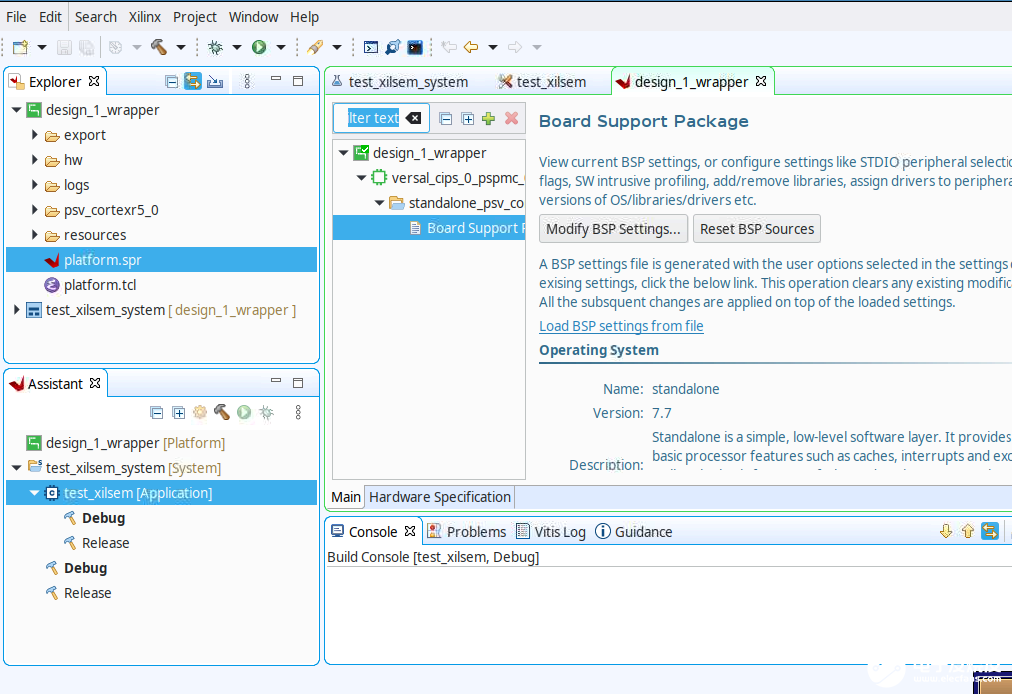

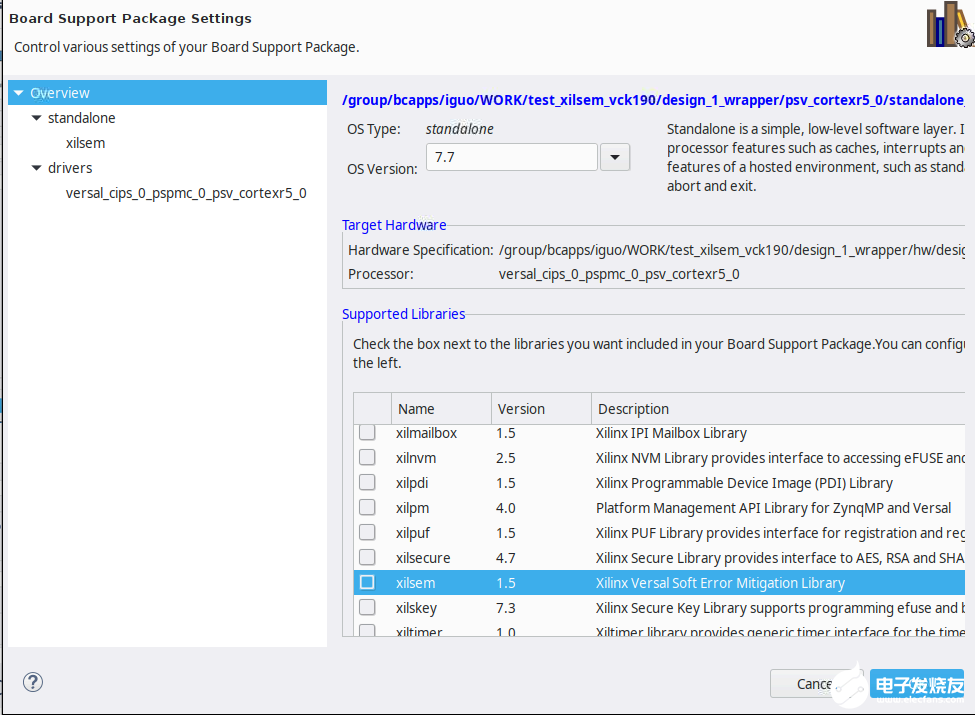

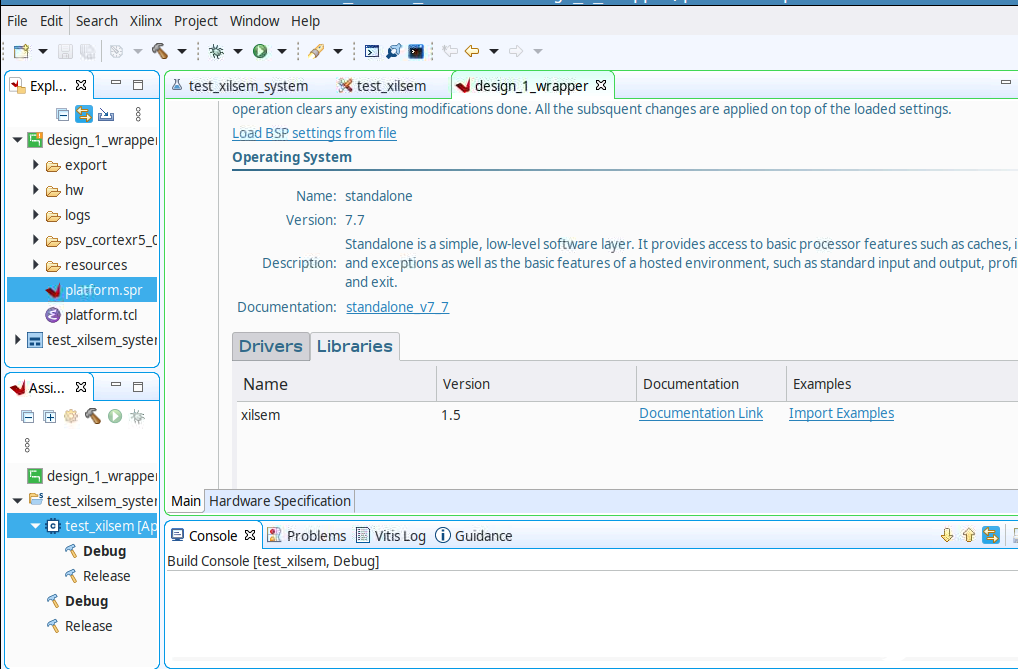

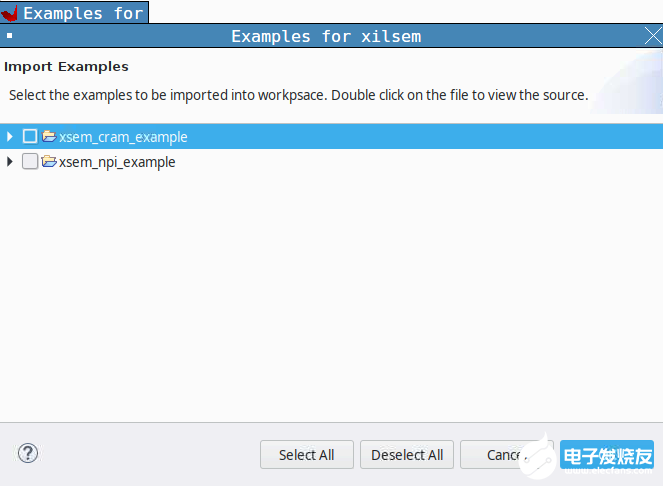

修改BSP設(shè)置,找到XilSEM庫(kù),點(diǎn)擊 ’Import Examples’, 導(dǎo)入其example:

sem_cram_example,點(diǎn)擊OK。

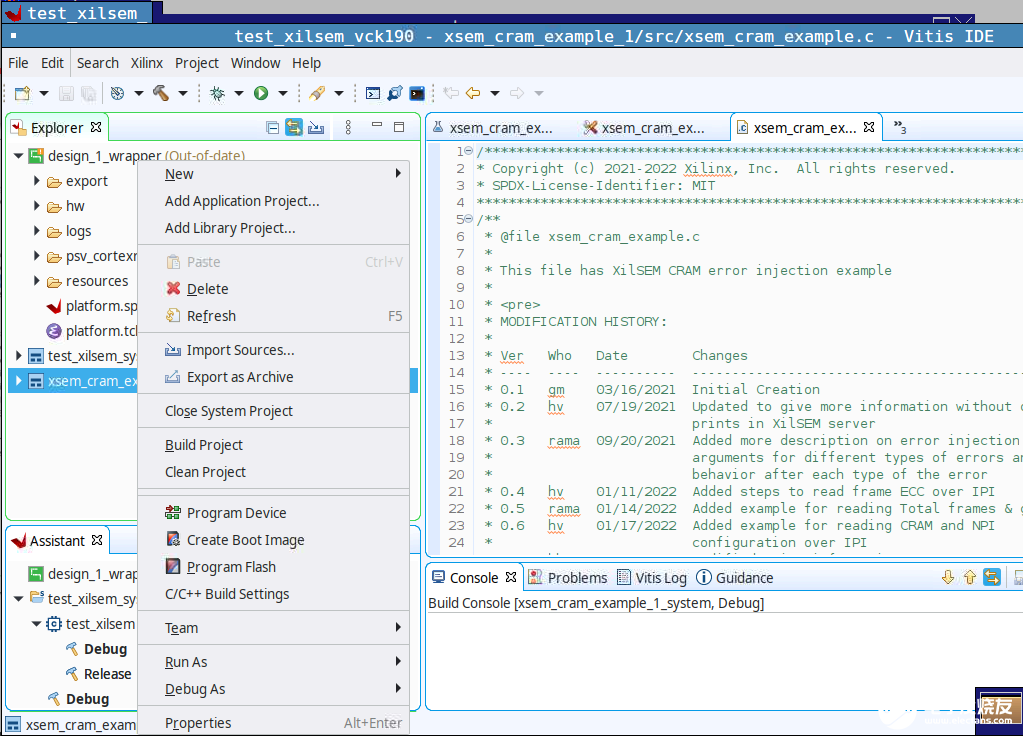

編譯新建的xsem_cram_example_1工程,生成elf文件。

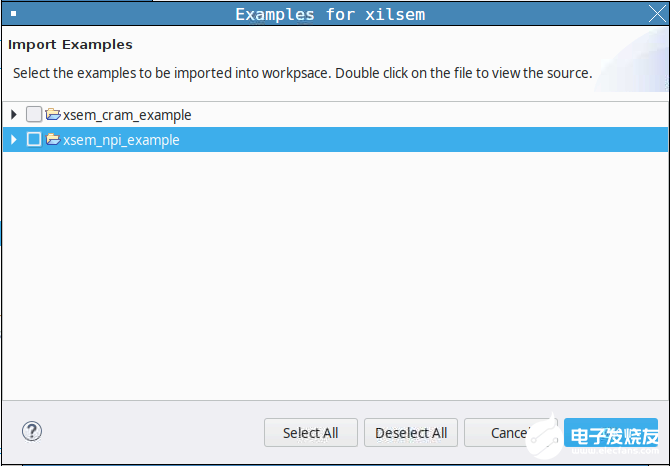

可以重復(fù)一樣的步驟,再次選擇xsem_npi_example, 則可以生成NPI掃描的elf文件。

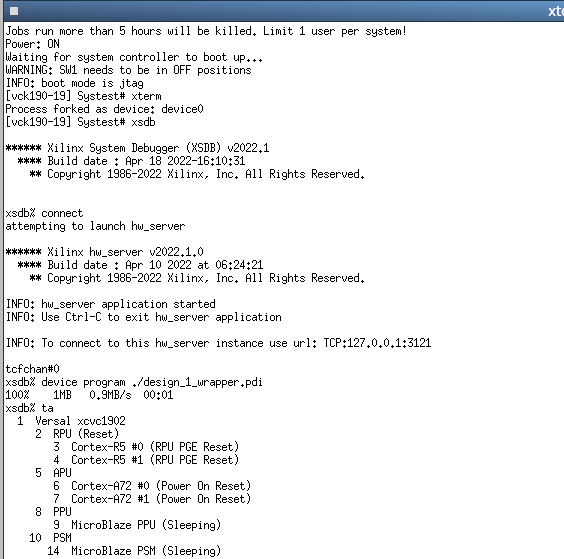

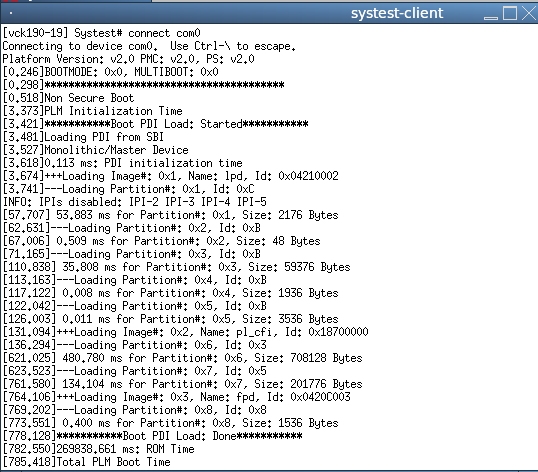

3. 連接VCK190開(kāi)發(fā)板,打開(kāi)串口顯示窗。下載pdi文件。可以看到輸出log如下:

執(zhí)行如下指令序列進(jìn)行cram elf文件的下載:

ta

ta 3

rst -proc

dow -force <.elf>

con

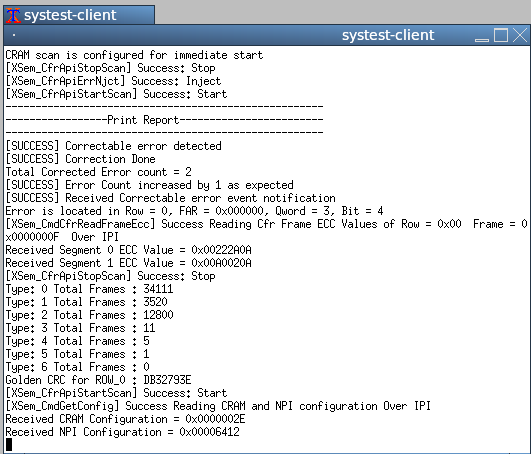

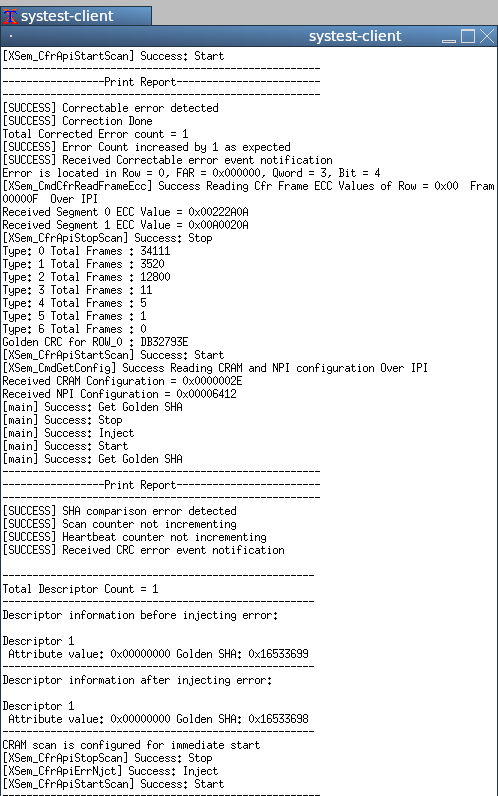

可觀測(cè)到串口輸出如下。此時(shí)XilSEM已經(jīng)開(kāi)啟并運(yùn)行了。注意example程序進(jìn)行了一次插錯(cuò)測(cè)試。

同樣方式,下載NPI elf,log打印信息如下:

這篇文章介紹了在工程中如何開(kāi)啟最基本的XilSEM功能,可以添加任意自己的設(shè)計(jì)。但是對(duì)于某些高級(jí)功能比如DFX,還需要在將來(lái)版本中完成兼容。

審核編輯:湯梓紅

-

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120689 -

開(kāi)發(fā)板

+關(guān)注

關(guān)注

25文章

5082瀏覽量

97718 -

Versal

+關(guān)注

關(guān)注

1文章

160瀏覽量

7677

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺(tái)之 Versal 介紹(2)

如何推遲XilSEM掃描功能的開(kāi)始?(二)

Versal系列芯片三個(gè)產(chǎn)品的基礎(chǔ)知識(shí)

Xilinx宣布7nm Versal AI Core和Versal Prime系列器件全面量產(chǎn)出貨

UltraScale和Versal之間有哪些不同?

Versal ACAP中的配電系統(tǒng)

基于Versal的圖像恢復(fù)管道

Versal System Monitor(Sysmon):過(guò)熱告警行為

Versal平臺(tái)的系統(tǒng)級(jí)優(yōu)勢(shì)

Versal ACAP設(shè)計(jì)指南

怎樣開(kāi)啟javascript功能

Versal 自適應(yīng)SoC設(shè)計(jì)指南

如何開(kāi)啟Versal的XilSEM功能

如何開(kāi)啟Versal的XilSEM功能

評(píng)論