來源:電子與封裝

摘 要

隨著異構(gòu)集成模塊功能和特征尺寸的不斷增加,三維集成技術(shù)應(yīng)運而生。凸點之間的互連 是實現(xiàn)芯片三維疊層的關(guān)鍵,制備出高可靠性的微凸點對微電子封裝技術(shù)的進(jìn)一步發(fā)展具有重要意 義。整理歸納了先進(jìn)封裝中的凸點技術(shù),包括凸點的制備方法與材料、微觀組織與力學(xué)性能、電性 能與可靠性、仿真在凸點中的應(yīng)用,為后續(xù)凸點研究提供參考。最后,對凸點技術(shù)進(jìn)行了展望,凸 點工藝將繼續(xù)向著微型化、小節(jié)距、無鉛化和高可靠性方向發(fā)展。

1 引言

近年來,隨著半導(dǎo)體技術(shù)的迅速發(fā)展,工藝制程 的節(jié)點已逐步接近原子尺寸級別,先進(jìn)封裝逐漸成為 延續(xù)摩爾定律的主要方式。從行業(yè)發(fā)展趨勢看,封裝 正在向著小型化、輕質(zhì)量、更多I/O數(shù)、高性能、高速 度、高頻率、高集成化的方向發(fā)展。倒裝(FC)焊接技 術(shù)應(yīng)運而生,在某些高要求應(yīng)用中逐漸取代傳統(tǒng)的引 線鍵合技術(shù),以減小封裝體積,提升封裝密度,縮短互連長度,從而減小寄生電容,提升傳輸速度。

倒裝焊接技術(shù)作為一種先進(jìn)封裝技術(shù),其發(fā)展離不開焊點技 術(shù)的革新。倒裝焊接技術(shù)的精度要求進(jìn)一步提升了凸點(尤 其是微型凸點)制備的復(fù)雜性。微小的凸點間距和高 度增加了填充工藝的難度。同時,多應(yīng)力作用下的凸 點極易產(chǎn)生諸如界面空洞、金屬間化合物(IMC)擴(kuò)展 等缺陷,加速芯片失效的過程。因此,在后摩爾時 代,針對凸點小型化、材料選擇、可靠性等問題,需要建 立合理的評判機(jī)制。本文主要介紹先進(jìn)封裝中凸點 技術(shù)的研究進(jìn)展,并結(jié)合應(yīng)用端,展望凸點技術(shù)的發(fā) 展趨勢。

2凸點的制備方法與材料

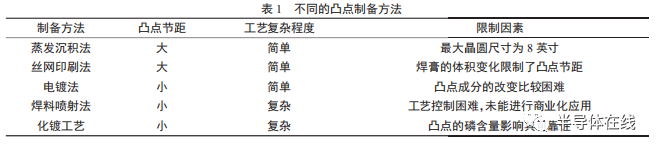

凸點按照制備方法可以分為蒸發(fā)沉積、絲網(wǎng)印 刷、植球、電鍍、噴射、化鍍等。

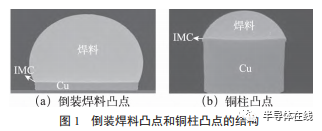

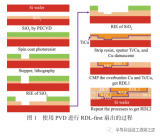

凸點最早使用的制備方法為蒸發(fā)沉積法,由IBM公司研發(fā)并用于芯片F(xiàn)C鍵合,并隨著可控坍塌芯 片連接(C4)技術(shù)而流行起來。該凸點材質(zhì)最初選用 銅,后逐步轉(zhuǎn)變?yōu)殄a鉛焊料凸點,被IBM及其他公司 持續(xù)使用了幾十年,并一直保持高可靠性記錄。倒裝 焊料凸點和銅柱凸點的結(jié)構(gòu)如圖1所示。由于鉛及其 化合物均有很大毒性,對人體健康和環(huán)境有不良影 響,我國出臺了《電子信息產(chǎn)品污染控制管理辦法》以 限制鉛及含鉛物質(zhì)的使用。由于成本以及良率、節(jié)距 的問題,8英寸晶圓是蒸發(fā)沉積技術(shù)的終點。

絲網(wǎng)印刷技術(shù)由印制電路板產(chǎn)業(yè)引進(jìn)到晶圓級 封裝技術(shù)中,采用絲網(wǎng)印刷法制備凸點的優(yōu)點是工 藝簡單、操作方便、成本低,缺點是用此種方法制備的 凸點節(jié)距較大,無法制備較小節(jié)距凸點是因為回流前 后焊膏的體積變化很大,需要足夠大的空間。

采用電鍍法制備凸點,具有工藝簡單、易于量產(chǎn)、 一致性好、線寬/線距小等優(yōu)點,其被廣泛應(yīng)用于半導(dǎo)體封裝領(lǐng)域。該方法的缺點是工序相對復(fù)雜,改變 焊料合金的成分相對較難,需要通過對電鍍液中各組 成成分的含量進(jìn)行控制,且在凸點存在狀態(tài)下進(jìn)行種子層刻蝕。

焊料噴射是連續(xù)的無掩模焊料沉積技術(shù),用噴頭 將液態(tài)焊料噴射至晶圓上。此技術(shù)可以實現(xiàn)較高的噴 射頻率,但對整個工藝的控制較為困難。

由于不需要采用光刻和濺射等工序,化鍍工藝的 成本較低,可以直接對露出鋁焊盤的晶圓進(jìn)行濕法處 理,從而吸引了研究者的關(guān)注。德國的IZM工藝是先 對晶圓背面掩模,然后進(jìn)行正面鈍化層的清洗,通過 鋁焊盤的活化、浸鋅、化鎳、浸金、清洗等制備出磷鎳凸 點,其厚度為5μm,表面防氧化層金的厚度為50~ 80 nm。不同凸點制備方法如表1所示。

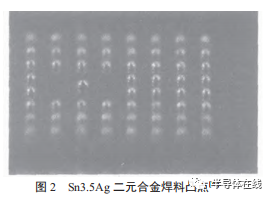

中國電子科技集團(tuán)公司第二十四研究所采用德國電鍍技術(shù)有限公司的MOT機(jī)臺和某進(jìn)口電鍍 液 , 電 鍍 制 備 出 以Cu為 凸 塊 下 金 屬 (UBM)的Sn3.5Ag二元合金焊料凸點,如圖2所示。通過對陽極 板位置的調(diào)節(jié)、藥液中Sn離子和Ag離子濃度比值的 調(diào)節(jié)、電鍍液的定期監(jiān)控等措施將凸點的成分控制在Sn、Ag的質(zhì)量比為96.5∶3.5。

YU等的研究將 Sn/Ag/Cu 三元無鉛焊料作為含 鉛焊料的潛在替代品,并對 Sn/2.5Ag/0.7Cu、Sn/3.5Ag/ 0.7Cu、Sn/3.5Ag/0.7Cu/0.1RE 和 Sn/3.5Ag/0.7Cu/0.25RE 的微觀結(jié)構(gòu)和力學(xué)性能進(jìn)行了研究。當(dāng) Sn/2.5Ag/ 0.7Cu 和 Sn/3.5Ag/0.7Cu 中形成粗大的 β-Sn 晶粒時, Sn/3.5Ag/0.7Cu 合金中出現(xiàn)塊狀的 Ag、Sn。通過摻雜 微量稀土元素 Ce 使得粗大的 Cu6Sn5 和 Ag3Sn 晶粒得 以細(xì)化,這主要是由于稀土元素 Ce 起到了釘扎作用, 抑制了晶粒的生長。由于顯微組織精細(xì)均勻,提高了 拉伸強(qiáng)度和伸長率,稀土元素的加入可以作為開發(fā)新 型無鉛焊料的有效途徑。

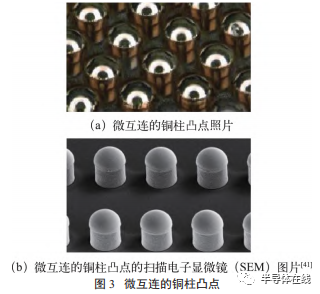

WEI等介紹了銅柱凸點技術(shù)的進(jìn)展,對比了銅 柱焊料凸點(CPB)和C4凸點的性能,列舉了各大廠 的代表銅柱凸點,介紹了銅柱凸點的制造工藝、應(yīng)用 場景、可靠性、倒裝問題和可以生產(chǎn)的封裝廠,以及未 來的發(fā)展趨勢。微互連的銅柱凸點如圖3所示。CPB工藝以其更小的凸點節(jié)距(<50μm),更優(yōu)良的電學(xué) 性能、熱學(xué)性能和機(jī)械性能,能夠滿足未來高I/O密 度、優(yōu)良電熱性能的封裝需求。

呂鏢等研究了陰極移動對在不同電流密度下制 備的鎳層表面形貌、粗糙度、孔隙率、組織結(jié)構(gòu)以及纖 維硬度等性能的影響。研究發(fā)現(xiàn),當(dāng)電流密度較大時, 陰極移動可以改善濃度極化導(dǎo)致的鍍層質(zhì)量劣化,降 低孔隙率和殘余應(yīng)力,但對晶向沒有影響。

相較于其他凸點制備方法,電鍍法具有易于批量 生產(chǎn)、一致性好,以及可以制備絕大部分凸點等優(yōu)點, 因此被廣泛應(yīng)用于集成電路的封裝領(lǐng)域。研究者們也 會針對凸點材料將常用凸點分為含鉛凸點及無鉛凸 點。由于鉛的毒性,無鉛電子組裝已成為不可扭轉(zhuǎn)的 趨勢。目前已經(jīng)明確用來取代Sn/Pb合金的無鉛焊料 是以Sn為基體的二元、三元甚至更多元的合金焊料。

3微觀組織與力學(xué)性能

凸點的成分、結(jié)構(gòu)及其形成的微觀組織決定了其 力學(xué)性能,國內(nèi)外學(xué)者進(jìn)行了大量的相關(guān)研究,以期 構(gòu)建凸點的微觀組織與力學(xué)性能之間的聯(lián)系,從而獲 得符合使用要求的凸點結(jié)構(gòu),并取得了大量的成果。

李福泉等采用熔融法熔滴SnPb焊料,其在CuNiAu焊盤上所形成的組織為Au/Sn IMC,Au/Sn凸 點的整體形貌如圖4所示。隨后的再回流過程中,Au/Sn IMC遷移至焊料基體內(nèi)部,裸露出的Ni層與Sn生成Ni3Sn4。隨著老化過程的進(jìn)行,AuSn4重新沉積 于界面,并形成(AuxNi1-x)Sn4,在該層之上有富鉛相產(chǎn) 生。Au/Sn IMC的反應(yīng)及其分布對焊料與焊盤間的力 學(xué)性能影響很大。

通過熔融共晶SnPb和熱退火Ni的反應(yīng)潤濕,在Ni上形成Ni3Sn4晶粒,并使用同步X射線衍射分析發(fā)現(xiàn)Ni3Sn4和Ni之間存在2種擇優(yōu)取向關(guān)系。

凸點的成分也會對界面反應(yīng)的動力學(xué)過程造成影 響。LAURILA等研究了SnPbAg、SnAg和SnAgCu凸點焊料與印制板上Ni/Au表面進(jìn)行光刻的界面反 應(yīng),特別是AuSn IMC的再沉積,發(fā)現(xiàn)SnPbAg/Ni/Au和SnAg/Ni/Au體系在焊接過程中形成的第一相為Ni3Sn4。在隨后的固相退火過程中,2個體系都出現(xiàn)了AuSn4、(Au, Ni)Sn4相的再沉淀,可用局部平衡的概念 和相應(yīng)的三元相圖解釋這一現(xiàn)象。結(jié)果表明,Ni可以 驅(qū)動(Au, Ni)Sn4發(fā)生再沉淀。當(dāng)焊料中含有一定的Cu時,首先形成的IMC為(Cu, Ni, Au)6Sn5,未發(fā)現(xiàn)AuSn4的再沉積,在富Sn焊料體系中加入少量Cu就 完全改變了互連系統(tǒng)的行為。

LABIE等研究報道了倒裝芯片尺寸凸點的Cu/Sn和Ni/Sn固態(tài)擴(kuò)散,在直徑為40μm的鍵合墊 倒裝凸點上測量了Cu/Sn和Ni/Sn的IMC互擴(kuò)散系 數(shù)和活化能,描述了金屬反應(yīng)的形貌。在Ni/Sn體系 中,少量的Cu對Ni的消耗有一定影響,而大量的Cu則會導(dǎo)致金屬間界面的極端扇貝化。

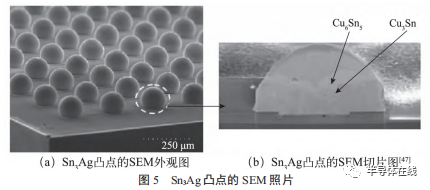

回流焊的條件會改變凸點的微觀形貌,從而影響 其可靠性。林小芹等用電鍍法制備了以Cu為UBM的尺寸小于100μm的Sn3Ag凸點,圖5為Sn3Ag凸 點的SEM照片。芯片內(nèi)凸點高度的一致性為1.4%,4英寸片間的凸點高度一致性約為3.57%;研究了Cu焊 盤與焊料SnAg在不同回流次數(shù)下界面反應(yīng)及孔洞形 成的機(jī)理,預(yù)測了對凸點連接可靠性的影響。研究結(jié) 果表明,焊料與Cu6Sn5界面中孔洞的產(chǎn)生主要是相變 體積收縮所致。凸點的剪切強(qiáng)度隨著回流次數(shù)的增多 而增大,Cu6Sn5/Cu界面隨服役而不斷產(chǎn)生的孔洞對凸 點的長期可靠性會產(chǎn)生不利影響。

GORLICH等研究了固態(tài)Ni和液態(tài)Sn之間的 焊接。研究發(fā)現(xiàn),只有在工藝的早期階段,IMC晶粒的 生長隨時間呈線性變化。之后,IMC晶粒的生長速度 逐漸下降。值得注意的是出現(xiàn)了速率常數(shù)不同的2個體系。用最新的助焊劑驅(qū)動理論討論了所觀察到 的生長速度變化,但是這個理論僅針對4 min內(nèi)的 短回流過程有效。使用透射電鏡觀察到扇貝狀微結(jié) 構(gòu),在Ni/Ni3Sn4界面新晶粒永久成核,海綿狀等軸 晶粒隨后形成。晶界潤濕只出現(xiàn)在反應(yīng)區(qū)的一定范圍內(nèi)。

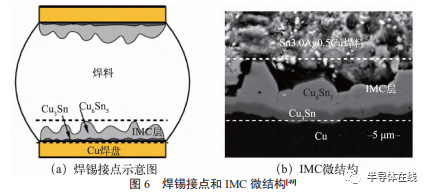

凸點的微觀形貌也會影響其剪切強(qiáng)度。TIAN等對含有限晶粒數(shù)的回流失效凸點進(jìn)行了動態(tài)剪切測 試,研究了SAC305/Cu凸點的變形和斷裂行為。使用 偏振光顯微鏡(PLM)和電子束背散射(EBSD)技術(shù)分 析了晶粒的形貌和分布,利用SEM觀察了凸點組織 和IMC對凸點斷裂行為的影響,焊錫接點和IMC微 結(jié)構(gòu)如圖6所示。實驗結(jié)果表明,在Sn3.0Ag0.5Cu焊 料中,IMC(Cu6Sn5和Ag3Sn)的形貌和分布是導(dǎo)致焊 料尺寸效應(yīng)的主要原因。隨著凸點尺寸的增大,回流 和失效焊接頭的剪切強(qiáng)度降低。分散在小凸點中的納 米顆粒狀A(yù)g3Sn對凸點的力學(xué)性能有強(qiáng)化作用。樹枝 狀和羽毛狀的Ag3Sn使大尺寸的凸點變脆。在動態(tài)剪 切測試中,小凸點出現(xiàn)了明顯的塑性變形,并發(fā)生了 動態(tài)回復(fù)和再結(jié)晶。斷裂發(fā)生在大部分焊料中,而脆 性斷裂發(fā)生在大凸點中,斷裂位置靠近焊料表面。裂 紋以穿晶斷裂的方式擴(kuò)展。老化后,所有的凸點均發(fā) 生動態(tài)回復(fù)和再結(jié)晶。大凸點的塑性增強(qiáng),在動態(tài)測 試過程中發(fā)生穿晶斷裂和沿晶斷裂。

CHUANG等對Ni和Sn反應(yīng)的空洞消除進(jìn)行 了研究,以揭示空間限制對Ni/Sn和Ni/SnAg反應(yīng)的 影響。結(jié)果表明,空間限制導(dǎo)致Ni/Sn/Ni夾層中心附 近形成了空洞,其根本原因是反應(yīng)產(chǎn)生的體積收縮不 能通過夾層垂直厚度的減小而完全消散。在Ni3Sn4相 反方向生長的晶粒互相撞擊,有效地阻止了夾層垂直厚度的減小。第一次增加質(zhì)量分?jǐn)?shù)為2.4 %的Ag時有 效地消除了這些空洞,說明加入Ag可以顯著地抑制Ni/Sn空洞的產(chǎn)生,有人認(rèn)為這是Ag原子的析出擴(kuò)散 造成的。

CHUANG等提出了在三維集成電路封裝中由 空間引起界面反應(yīng)的幾個關(guān)鍵問題。包括IMC晶粒的 碰撞產(chǎn)生結(jié)構(gòu)缺陷,焊料濃度消耗導(dǎo)致雜質(zhì)濃度上 升,焊料尺寸變小導(dǎo)致薄膜層對UBM和表面光潔度 的影響越來越大等,并討論了這些問題的含義和解決方案。

凸點的尺寸也會改變IMC的生長情況。HUANG等 報道了在Ni/SnAg/Cu焊料微凸點中的新發(fā)現(xiàn),IMC的生長速率在很大程度上取決于焊料厚度。在Ni/SnAg(厚度為40μm)/Cu結(jié)構(gòu)中,化合物在Ni側(cè) 的生長速度比在Cu側(cè)快。由于焊料中Cu和Ni濃度 的梯度變化,當(dāng)焊料厚度小于20μm時,IMC的生長情況相反。

LIANG等研究了焊料厚度分別為4μm和12μm時,Ni/Sn2.3Ag/Ni微凸點的三明治結(jié)構(gòu)在260℃下經(jīng) 回流后的微結(jié)構(gòu)演變。當(dāng)焊料厚度為4μm的微凸點 經(jīng)過1次4 min的回流處理后,Ni在UBM界面處形 成了IMC,成分為Ni3Sn4,形成的Ag3Sn IMC分散在焊 料基體中。當(dāng)回流時間接近34 min時,Ni3Sn4 IMC幾 乎占據(jù)了整個界面,此時在IMC中仍有些孔洞。相比 之下,在焊料厚度為12μm的微凸點中Ni3Sn4 IMC的 生長速率要慢于焊料厚度為4μm的微凸點。

陳雷達(dá)等研究發(fā)現(xiàn),由于IMC的熱膨脹系數(shù)、 彈性模量、斷裂伸長率等材料參數(shù)與基體金屬差異很 大,所以IMC越厚就越容易產(chǎn)生龜裂,導(dǎo)致凸點失效。在使用過程中由于擴(kuò)散導(dǎo)致的柯肯達(dá)爾孔洞也會成 為裂紋的源頭。因此,IMC的形貌、厚度和結(jié)構(gòu)都會影 響凸點的可靠性。微型化導(dǎo)致的尺寸效應(yīng)對可靠性產(chǎn) 生了越來越重要的影響。

YU等研究了高度小于10μm時Ni/SnAg/Ni微 凸點中的Ag含量對減少孔洞的影響,系統(tǒng)地研究了Ag的質(zhì)量分?jǐn)?shù)低于8%時的最佳值。結(jié)果表明,在固 態(tài)反應(yīng)中,當(dāng)Ag的質(zhì)量分?jǐn)?shù)低于2.4 %時有孔洞產(chǎn) 生;當(dāng)Ag的質(zhì)量分?jǐn)?shù)不低于3.5 %時,幾乎沒有孔洞 產(chǎn)生,且在鍵合條件下析出Ag3Sn。當(dāng)Ag的質(zhì)量分?jǐn)?shù) 達(dá)到8%時,形成了部分連續(xù)的Ag3Sn層。

YANG等研究了Cu/Ni/SnAg微凸點中Sn的表 面擴(kuò)散對IMC生長的影響,發(fā)現(xiàn)隨著凸點尺寸的降 低,表面擴(kuò)散變得更加重要。該團(tuán)隊采用透射電鏡 (TEM)觀察了側(cè)面的Ni3Sn(靠近4 Ni3Sn4/Ni界面)、側(cè) 壁Ni3Sn(在2 Ni阻擋層表面)和側(cè)面Cu3Sn(在銅柱表 面)對Sn原子擴(kuò)散的影響;計算出了Ni3Sn4橫向生長 常數(shù)約為0.025 7μm/h1/2。基于以上實驗結(jié)果和擴(kuò)散理 論,提出了微凸點中IMC的形成機(jī)理,在高密度電子 封裝中,表面擴(kuò)散引起的額外IMC生長可能是引起失 效風(fēng)險的潛在因素。

CAI等通過Sn層間的厚度優(yōu)化、界面IMC的 生長演化和凸點尺寸效應(yīng)這3個重要實驗研究Cu/Sn固態(tài)鍵合。通過對電鍍Sn表面粗糙度和預(yù)制Cu6Sn5晶粒峰的分析,確定Sn中間層的最小厚度為2μm。在 鍵合前,只有一個不穩(wěn)定的Cu6Sn5相在室溫下形成, 該相的成核是一個不穩(wěn)定過程。在富Cu的Cu/Sn/Cu三明治結(jié)構(gòu)的鍵合和退火過程中,Sn中間層經(jīng)歷了還 原、分裂和衰竭,相應(yīng)的Cu6Sn5相發(fā)生了生長、合并和 轉(zhuǎn)變,最終形成了一個穩(wěn)定的Cu/Cu3Sn/Cu的3層結(jié) 構(gòu)。柯肯達(dá)爾孔洞出現(xiàn)在Cu/Cu3Sn界面處,且隨著Cu6Sn5相的減少而不斷生成。在200℃的低溫條件下,Cu/Sn鍵合中IMC的生長機(jī)制仍為晶格擴(kuò)散。當(dāng)Sn存在時,Cu6Sn5相的產(chǎn)生抑制了Cu3Sn的生長,且得到了2個略大的互擴(kuò)散系數(shù)D(Cu6Sn5)=3.035×10-17m2/s,D(Cu3Sn)=7.496×10-17m2/s。隨著凸點寬度的不斷降低, 尤其是降低至60μm以下時,IMC側(cè)向生長引起的凸 點尺寸效應(yīng)逐漸明顯,并對細(xì)節(jié)距Cu/Sn/Cu互連有利。

田飛飛等在CuNi焊盤上植共晶Sn63Pb37焊 球,用波峰焊焊接至化學(xué)鍍NiAu的PCB銅焊盤上, 通過SEM觀察了界面的微觀組織,采用色譜儀(EDS) 分析其微觀組織成分。結(jié)果表明,芯片側(cè)從Ni層往PCB方向,IMC依次為(Cu, Ni)3Sn、(Cu, Ni)6Sn5;PCB側(cè)從Ni往芯片方向,IMC依次為NiSnP三元化合物 和(Cu,Ni)6Sn5。由于IMC多為脆性相,容易產(chǎn)生微裂 紋并對凸點的力學(xué)性能、可靠性有不利影響。

LIN等人首次在高溫、高濕存儲條件下觀察到 在Cu/Ni/SnAg微凸點表面的淺層晶粒上生長出錫晶 須。氧化反應(yīng)和IMC反應(yīng)形成的應(yīng)力差導(dǎo)致了晶須的 形成。均勻取向的相關(guān)孿晶減緩了Sn原子的擴(kuò)散速 率,淺層表面較大體積的Ag3Sn限制了晶須晶界的遷 移,對晶須和小丘表面形貌有著重要影響。在此基礎(chǔ) 上,他們提出了Sn晶須和階地狀小丘的形成機(jī)理。該 研究結(jié)果對孤立Sn基凸點上的Sn晶須和小丘具有 重大意義,對3D電子封裝的可靠性具有指導(dǎo)意義。

目前關(guān)于力學(xué)性能與微結(jié)構(gòu)的研究主要集中在 較大尺寸的凸點中,針對微型凸點的力學(xué)性能研究較少。此外,實際生產(chǎn)過程中的工藝條件以及凸點尺寸 的差異均會顯著影響界面IMC,從而導(dǎo)致凸點的力學(xué) 性能發(fā)生變化。因此,在后續(xù)研究中有必要進(jìn)一步聚 焦微型凸點的微觀結(jié)構(gòu)及其力學(xué)性能。

4微觀組織與電性能及可靠性

凸點的微觀組織不僅決定了其力學(xué)性能,還會對 電路的電性能及可靠性造成影響。隨著電路不斷朝著 微型化方向發(fā)展,封裝結(jié)構(gòu)中的凸點尺寸越來越小, 凸點所經(jīng)受的電流密度大大提高。電遷移對元素擴(kuò)散 與界面反應(yīng)的影響變得越來越重要。因此,在電遷移 作用下凸點中的元素擴(kuò)散及界面反應(yīng)已經(jīng)成為微電 子封裝的研究熱點。

由于實際倒裝凸點結(jié)構(gòu)為非對稱結(jié)構(gòu),在凸點的 電流入口處和出口處容易產(chǎn)生嚴(yán)重的電流擁擠效應(yīng) 與焦耳熱效應(yīng),進(jìn)而使得凸點處的電遷移現(xiàn)象變得十 分復(fù)雜。陳雷達(dá)在“純化條件下”研究電遷移對Cu/Sn/Cu、Cu/Sn/Ni凸點中元素擴(kuò)散及界面反應(yīng)的影 響,并在此基礎(chǔ)上更深一步地研究了電遷移對這2種 凸點的界面反應(yīng)與失效機(jī)理的影響。經(jīng)研究發(fā)現(xiàn),對 于Cu/Sn/Cu對稱結(jié)構(gòu),在電遷移作用下,凸點界面的IMC生長呈現(xiàn)明顯的極性效應(yīng)。陰極界面處的IMC生 長弱于陽極界面處的IMC生長。電流密度越大、溫度 越高,界面IMC的生長速率越大。

對于Cu/Sn/Ni非對稱結(jié)構(gòu),在液/固與固/固條 件下,界面IMC在電遷移過程中的生長均呈現(xiàn)極性效 應(yīng),液/固條件下陽極界面的生長速率比液/液條件 下高一個數(shù)量級。電子風(fēng)的方向影響凸點中Cu-Ni的 交互作用,在固/固的電遷移條件下,Cu原子只有在 順電子風(fēng)擴(kuò)散時才能夠擴(kuò)散到對面Sn/Ni界面并改變 界面IMC的類型,在逆電子風(fēng)時無法擴(kuò)散到對面Sn/Cu界面,對應(yīng)的IMC為(Cu, Ni)6Sn5;Ni原子無論 在順/逆電子風(fēng)下都無法大量擴(kuò)散到Sn/Cu界面,在150℃、104A/cm2的條件下,當(dāng)Ni為陰極時會大量溶 解并與Sn原子生成塊狀Ni3Sn4。在液/固的電遷移條 件下,原子擴(kuò)散更快,Cu原子在順/逆電子風(fēng)條件下 均能擴(kuò)散到對面的Sn/Ni界面IMC;Ni原子只有在順 電子風(fēng)時可以擴(kuò)散到對面Sn/Cu界面,逆電子風(fēng)時并 不 能 擴(kuò) 散 到 對 面Sn/Cu界 面 , 即 對 應(yīng) 的IMC為Cu6Sn5。

對于Ni/Sn3Ag0.5Cu/Cu凸點而言,在電遷移作用 下凸點只存在一種失效模式,即當(dāng)電子由基板(Cu)端 流向芯片(Ni)端時,電流擁擠效應(yīng)導(dǎo)致基板端的Cu原子在電子入口處出現(xiàn)局部的快速溶解,并導(dǎo)致在陰 極界面處形成裂紋。在150℃、104A/cm2條件下電遷 移1 000 h后,陰極Cu基板基本消耗完,裂紋貫穿整 個陰極界面。在180℃、104A/cm2條件下經(jīng)過143 h電 遷移后,凸點已經(jīng)發(fā)生失效。當(dāng)電子由芯片端流向基 板端(芯片端Ni UBM為陰極)時,陰極Ni UBM未發(fā) 生明顯溶解。無論溫度如何,電遷移都沒有引起凸點 失效。

研究結(jié)果表明,IMC界面的生長動力學(xué)符合拋物 線規(guī)律,而且電流密度越大、溫度越高,界面的生長速 率就越大。然而,目前關(guān)于凸點的電遷移研究絕大部 分都集中在固/固電遷移方面。隨著凸點尺寸的不斷 減小,通過凸點的電流密度越來越大,凸點中的電流 擁擠效應(yīng)和焦耳熱效應(yīng)更加明顯。凸點極易在電遷移 過程中發(fā)生熔化現(xiàn)象。因此,進(jìn)一步研究凸點在液/固 條件下的電遷移行為對理解凸點的失效機(jī)理起著至 關(guān)重要的作用。

5仿真分析在凸點研究中的應(yīng)用

隨著互連密度越來越高,凸點逐漸向著細(xì)節(jié)距、微尺寸方向發(fā)展,熱疲勞可靠性問題的影響越發(fā)突 出。為了應(yīng)對這一問題,諸多學(xué)者運用有限元分析 方法、試驗設(shè)計法(DOE)開展了凸點的熱疲勞可靠性 研究,對解決實際工程難題有一定的指導(dǎo)意義。

王健等發(fā)明了一種以硅為基板的微波芯片倒裝 封裝結(jié)構(gòu),該結(jié)構(gòu)可以解決關(guān)鍵的微波芯片背面接地 問題,并建立了三維有限元模型,在此封裝結(jié)構(gòu)中進(jìn) 行了金凸點的熱疲勞可靠性研究。結(jié)果表明,關(guān)鍵金 凸點的最大等效總應(yīng)變分布在硅與凸點的界面處。根 據(jù)其他學(xué)者的研究結(jié)果,選取了凸點高度、直徑和共 晶焊料片厚度作為影響凸點熱疲勞可靠性的重要因 素,通過3因素3水平9組正交試驗對結(jié)構(gòu)設(shè)計進(jìn)行 了優(yōu)化,得出3個因素的影響程度依次為共晶焊料片 厚度>金凸點直徑>金凸點高度,對結(jié)構(gòu)設(shè)計具有指 導(dǎo)意義。

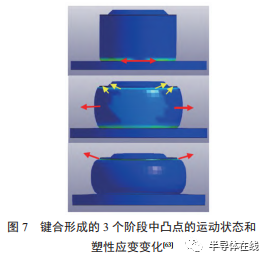

王健等還基于Ansys Workbench LS-DYNA軟 件,建立了包含鈍化層及凸點下金屬化結(jié)構(gòu)的熱超聲 倒裝結(jié)構(gòu)三維有限元模型。鍵合形成的3個階段中凸 點的運動狀態(tài)和塑性應(yīng)變變化如圖7所示。根據(jù)凸點 的運動狀態(tài)將鍵合形成過程進(jìn)一步細(xì)分為3個階段, 分析了仿真得到的凸點、凸點/焊盤界面及凸點下金屬化結(jié)構(gòu)的應(yīng)力、塑性應(yīng)變分布及其在鍵合過程中的 變化規(guī)律,指出了熱超聲倒裝芯片鍵合可靠性的風(fēng)險點。

凸點界面結(jié)合的物理機(jī)制是研究倒裝芯片鍵合 工藝的關(guān)鍵。而常規(guī)的試驗技術(shù)手段難以直接測量局 部區(qū)域內(nèi)的動態(tài)應(yīng)力、應(yīng)變瞬態(tài)特性。此外,后摩爾時 代采用的新材料、新結(jié)構(gòu)微互連凸點帶來了一系列新 的可靠性問題。為了實現(xiàn)其工程化應(yīng)用,需要通過合 適的仿真方式建立新的失效模型,探索綜合可靠性評 價和設(shè)計方法等。因此在后續(xù)研究中,凸點仿真的模 塊化和精細(xì)化是凸點結(jié)構(gòu)設(shè)計與工藝開發(fā)的關(guān)鍵。

6凸點在先進(jìn)封裝中的應(yīng)用

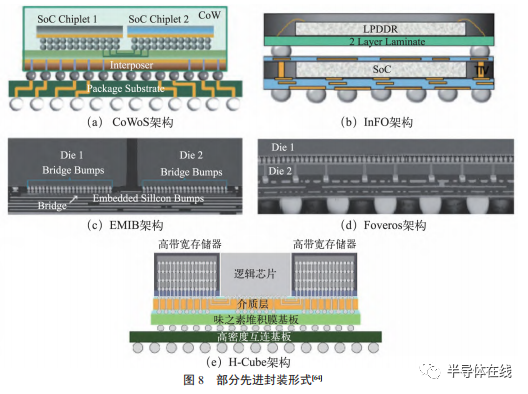

凸點是先進(jìn)封裝中重要的要素之一,它的主要作 用是電氣互連和應(yīng)力緩沖。從傳統(tǒng)的打線工藝發(fā)展到 倒裝焊接工藝,凸點起到了至關(guān)重要的作用。在當(dāng)前 比較知名的先進(jìn)封裝技術(shù)中,凸點技術(shù)都是其中的關(guān) 鍵技術(shù),如臺積電的2.5D CoWoS(Chip on Wafer on Substrate)技術(shù)和集成式扇出型封裝(InFO)技術(shù)、英特 爾的嵌入式多芯片互連橋(EMIB)和3D邏輯芯片封 裝 技 術(shù) (Foveros)、三星電子的扇出面板級封裝 (FOPLP)和混合基板封裝(H-Cube)技術(shù)等,部分先進(jìn) 封裝形式如圖8所示[64]。在過去的10年間,先進(jìn)封裝 技術(shù)快速發(fā)展,涌現(xiàn)出2D、2.5D、3D、3D+2D、3D+2.5D等多種封裝方式,應(yīng)用領(lǐng)域包括5G、AI、可穿戴設(shè)備、 高性能服務(wù)器、高性能顯卡等。總的來說,先進(jìn)封裝的 目的就是提升功能密度,縮短互聯(lián)長度,提升系統(tǒng)性 能,降低整體功耗,而其中最為重要的環(huán)節(jié)之一就是 凸點制備以及互聯(lián),因此凸點技術(shù)的開發(fā)與優(yōu)化影響 著先進(jìn)封裝技術(shù)的發(fā)展。

由于工藝技術(shù)的發(fā)展,凸點尺寸也變得越來越 小,單位面積芯片上的I/O引腳數(shù)量不斷增加,異構(gòu)集 成微系統(tǒng)以及凸點制備工藝將繼續(xù)呈現(xiàn)體積不斷微 型化、功能密度不斷提高的發(fā)展趨勢。伴隨著凸點互 連技術(shù)的不斷優(yōu)化,異構(gòu)集成微系統(tǒng)產(chǎn)品有望獲得突 破,并對集成電路行業(yè)產(chǎn)生顛覆性影響。

7 結(jié)束語

電子封裝的小型化、輕薄化要求倒裝芯片的凸點尺寸不斷減小,更高密度的微凸點技術(shù)正在研發(fā)并轉(zhuǎn)向量產(chǎn)應(yīng)用。但是隨著凸點尺寸的減小,體積效應(yīng)導(dǎo) 致物理、化學(xué)的影響更加顯著,包括化學(xué)反應(yīng)、金屬溶 解、化學(xué)勢梯度驅(qū)動的擴(kuò)散、電遷移、焦耳熱、熱遷移和 應(yīng)力遷移,這些因素對凸點長期可靠性影響的研究將 伴隨凸點尺寸的減小同步開展。在材料選擇方面,盡 管SnPb凸點由于其具有低成本和高可靠性的優(yōu)點, 被最早應(yīng)用于封裝互連中,但嚴(yán)格的禁鉛條例使封裝 行業(yè)研究者轉(zhuǎn)向了對無鉛凸點的開發(fā)與應(yīng)用,未來的 凸點材料既要滿足環(huán)保要求,也需要具有優(yōu)異的可靠性。在制備工藝方面,電鍍法由于具備工藝簡單、成本 低、易于批量生產(chǎn)等優(yōu)點,被廣泛應(yīng)用于凸點制備。隨著凸點尺寸的進(jìn)一步縮小和密度的進(jìn)一步增加,需要開發(fā)出更加合適的電鍍工藝,從而滿足不同的產(chǎn)品要求。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

51757瀏覽量

431305 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28164瀏覽量

227466 -

封裝

+關(guān)注

關(guān)注

128文章

8211瀏覽量

144112 -

微電子

+關(guān)注

關(guān)注

18文章

394瀏覽量

41529 -

先進(jìn)封裝

+關(guān)注

關(guān)注

2文章

440瀏覽量

411

原文標(biāo)題:先進(jìn)封裝中凸點技術(shù)的研究進(jìn)展

文章出處:【微信號:wc_ysj,微信公眾號:旺材芯片】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

先進(jìn)封裝RDL-first工藝研究進(jìn)展

新型銅互連方法—電化學(xué)機(jī)械拋光技術(shù)研究進(jìn)展

薄膜鋰電池的研究進(jìn)展

傳感器EMC的重要性與研究進(jìn)展

應(yīng)用聲發(fā)射評定金屬點蝕過程的研究進(jìn)展

應(yīng)用聲發(fā)射評定金屬點蝕過程的研究進(jìn)展

農(nóng)業(yè)機(jī)械自動導(dǎo)航技術(shù)研究進(jìn)展

先進(jìn)激光雷達(dá)探測技術(shù)研究進(jìn)展

先進(jìn)封裝中銅-銅低溫鍵合技術(shù)研究進(jìn)展

先進(jìn)封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進(jìn)展

評論