物理設計中的問題

設計寄生效應

寄生電阻

·如果電阻增加,延遲也會增加(延遲= RC)

·隨著技術的縮小,互連也會縮小,因此導線電阻將會增加

·為了避免這種情況我們將增加互連的高度

寄生電容

·隨著技術的不斷縮小,網絡高度不斷增加,因此側壁電容不斷增加

·隨著技術的縮小,電介質變得更薄,電容將增加

·減小電容,盡量減少可共用的表面積

·所以我們在設計時保持相鄰金屬層的垂直和水平

寄生電感

·互感影響:高頻母線

·自感影響:時鐘網絡

·隔離和屏蔽是可能的補救措施

·經驗法則是,當信號路徑的長度足夠長,達到波長的一定百分比時,線路本身就開始成為信號完整性的問題

·對于長線網和電源/時鐘線,在 500MHz 以上和 130nm 以下尤為突出

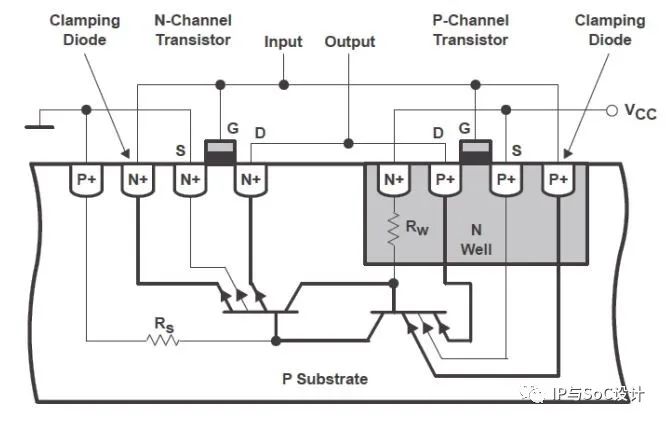

閂鎖

什么是閂鎖?

·CMOS/BiCMOS電路出現的現象

·在 VDD 電源和地之間生成低阻抗路徑

閂鎖原因

·由于寄生PNP和NPN晶體管之間的再生反饋

對設計的影響

·PN結會產生寄生晶閘管

·PNP/NPN結構形式

·需要相當大的輸入電流才能激活

·由寄生晶體管組成的晶閘管被觸發并在 VDD 和 GND 之間產生短路

·由于 VDD 和 GND 直接連接,導致自毀/系統故障

NPN晶體管

·N溝道MOSFET的發射極-漏極/源極

·底座-P基板

·集電極 – N 井,其中有互補的 P 溝道 MOSFET

PNP晶體管

·P溝道MOSFET的發射極-漏極/源極

·基極 – N 阱,其中有互補的 P 溝道 MOSFET

·集電極-P基板

晶閘管/SCR/PNPN二極管

·P溝道MOSFET的陽極-漏極/源極

·N溝道MOSFET的陰極-漏極/源極

·柵極-P基板

閂鎖的補救措施

** 抗閂鎖?? CMOS 工藝**

·降低寄生晶體管的增益(使用硅起始材料,在高摻雜襯底上有薄外延層)

·將保持電壓提高至 VDD 電源以上

·增加襯底和阱的摻雜濃度(但會導致更高的VT)

·逆行阱結構(底部高摻雜,頂部輕摻雜)

** 布局技巧**

·NMOS和PMOS之間有足夠的空間

·這降低了寄生晶體管的電流增益

·成功有限,因為只能增加到一定限度

·通過保持基板和孔的接觸盡可能靠近來減少RS和RW

·將基板觸點盡可能靠近連接到電源軌的晶體管的源極連接(VSS n 器件、VDD p 器件)

·這會降低 RSUBSTRATE 和 RWELL 的值

·一種非常保守的規則是為每個電源(VSS 或 VDD)連接放置一個襯底觸點

·標準中。基于細胞的設計,常見的 Well Tap 根據需要取出

·保護環

·晶體管的增益降低(在模擬設計中)

靜電放電 (ESD)

靜電放電 (ESD)

·當兩種非導電材料摩擦在一起然后分離時,相反的靜電電荷保留在兩者上,試圖相互平衡

·由于人為操作或機器接觸而產生的靜電荷瞬態放電

靜電放電的原因

·CMOS 的柵極氧化層薄而脆弱,使得 ESD 保護對于 CMOS 至關重要

·可能是由于電感或電容耦合

·金屬化過程中通過摩擦去除多余金屬時可能會發生ESD

· ESD 發生得如此之快,以至于普通 GND 線會表現出太大的電感,無法在造成損壞之前耗盡電荷

對設計的影響

·如果熱引發,ESD 也會燒毀器件/互連

·PMOS的ESD保護能力強于NMOS,因為NMOS的回彈保持電壓較低

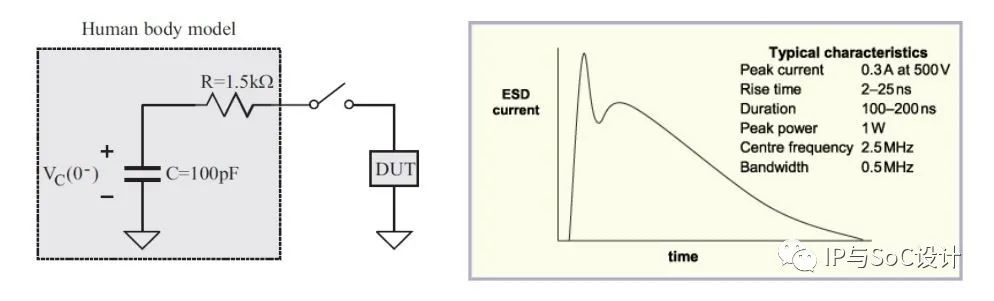

人體模型 (HBM)

·人體的實際電容在150pF到500pF之間,人體的內阻在幾千歐到幾百歐之間

·峰值電流約1.3A,上升時間約10-30ns

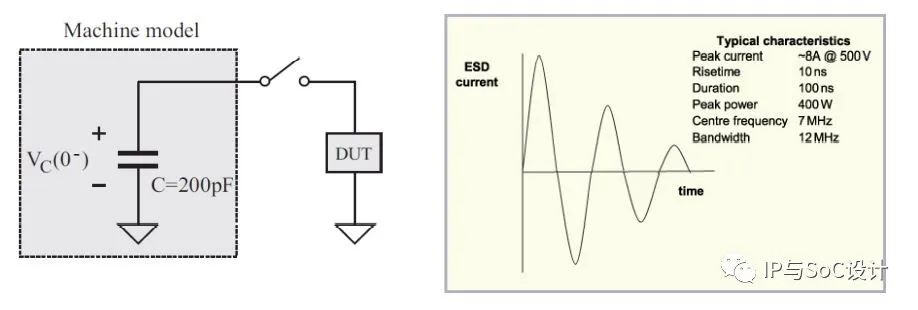

機器型號(MM)

·MM對制造/測試設備的ESD進行建模

·峰值電流約3.7A,上升時間約15-30ns,帶寬約12 MHz

·由于體電阻為零,帶電機器引起的ESD應力很嚴重

·MM ESD耐受電壓通常為HBM的十分之一

·大多數ESD保護電路只能保護HBM和MM

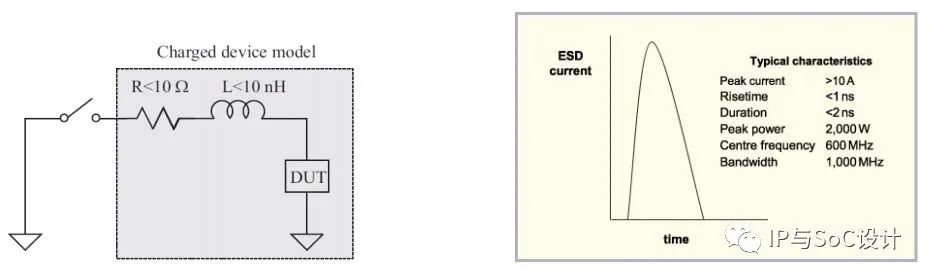

帶電器件模型 (CDM)

·CDM 對帶電集成電路的 ESD 進行建模

·隨著越來越多的電路和功能集成,導致芯片尺寸變大,從而提供了大的體電容,進而在 IC 體中存儲 CDM 的電荷

·模型中的電感主要來自鍵合線的電感

·與 HBM 和 MM 應力的熱失效特征相比,柵氧化層擊穿是 CDM 應力的特征失效

·CDM 應力是最難防范的 ESD 應力,因為瞬態速度最快,并且具有最大。峰值電流

·峰值電流約10A,上升時間約1ns

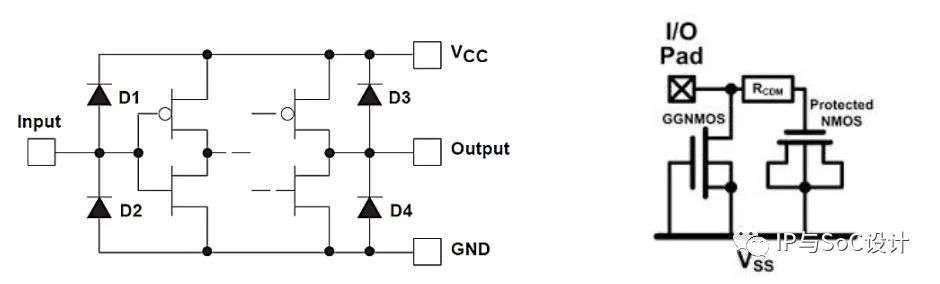

靜電放電保護

鉗位二極管的集成

·限制危險電壓并將過量電流傳導到電路的安全區域

保護二極管

·正常運行時面向阻塞

·位于要保護的組件的連接和電源電壓線之間的安全區域主要由電源電壓連接組成

電遷移

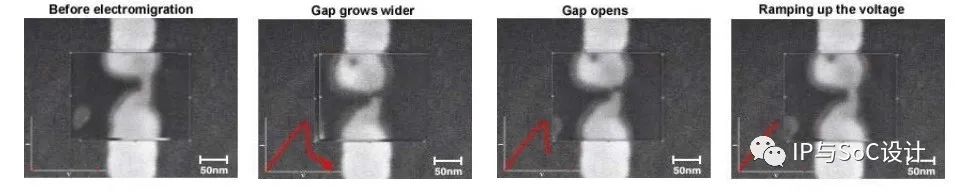

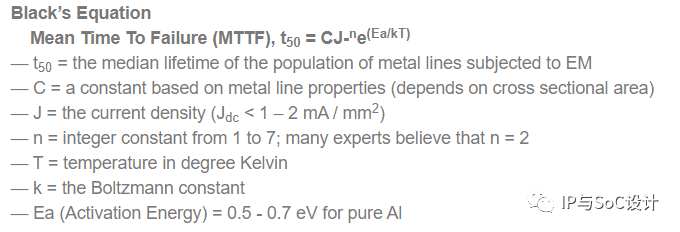

電遷移 (EM)

·高能電子撞擊材料中的原子并導致它們移動位置而引起的失效機制

·電場影響下原子的增強和定向遷移

電遷移的原因

·形成正反饋路徑,其中電磁將導致原子沿著導線移動,稍微縮小該位置的導線寬度并增加電流密度

·電流密度的增加進一步增加了電遷移,導致更多的原子被移位 由于傳導電子和擴散金屬原子之間的動量轉移,導體中離子的逐漸移動引起材料的傳輸

·在高電流密度區域問題最嚴重

·隨著尺寸的減小而顯著,對于單向 (DC) 電流最為顯著

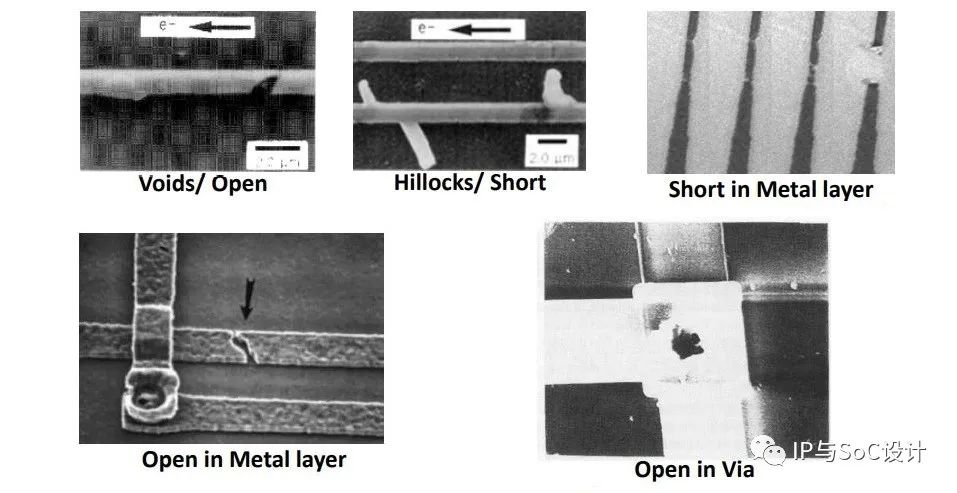

對設計的影響

·過高的EM會導致開路(空洞)和短路(Hillocks),從而降低芯片的可靠性

·更快地接近設備的使用壽命

·功耗增加

·更高的片上溫度

·高壓操作

·高頻開關

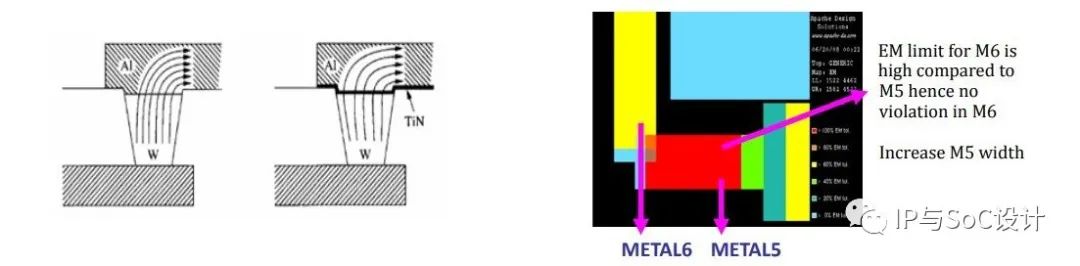

EM 補救措施和預防措施

·導線加寬以降低電流密度

·良好的電源管理技術

·更大的電網用于電網(將電網放在更厚的層上)

·信號網線加寬

·更好的電網規劃

·Power Greedy 網絡的雙倍調整

·提供冗余過孔

·設計電路以在較低電壓水平下運行

·通過與銅合金化可以提高電磁抗性

·使用熱感知 IC 設計方法控制溫度

·減少變異性的DFM技術

·此外,需要注意“碟形”效應(CMP)

EM 檢查的類型

與電流相關

·平均EM檢查

·RMS EM 檢查

·峰值EM檢查

與 籃網相關

·信號電磁檢查

·電源電磁檢查

·所有這些 EM 檢查的限制將在技術文件中指定為設備最小壽命的函數,具體取決于應用

·信號 EM 需要滿足所有三個與電流相關的 EM 檢查,除非另有說明

·對于電力網,滿足平均EM數就足夠了

電磁故障機制

·時序失敗:導線變窄會增加導線電阻,如果信號無法再在時鐘周期內傳播,可能會導致時序失敗

·功能故障:電遷移將持續到導線完全斷裂,不允許進一步的電流流動并導致功能故障

EM 規則類型

·基于金屬層(這是舊技術中使用的唯一規則)

·金屬長度或寬度相關的 EM 規則

·上下金屬的長度和寬度也取決于過孔寬度

·多項式的復雜規則

天線效應

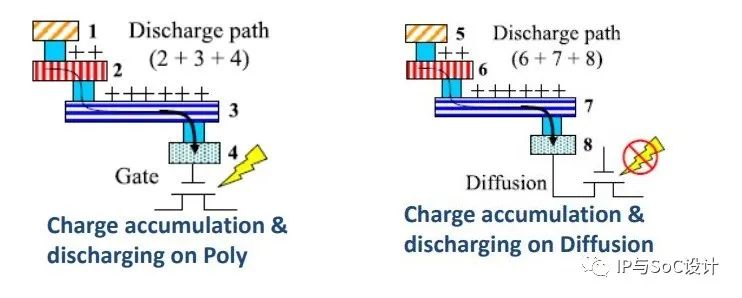

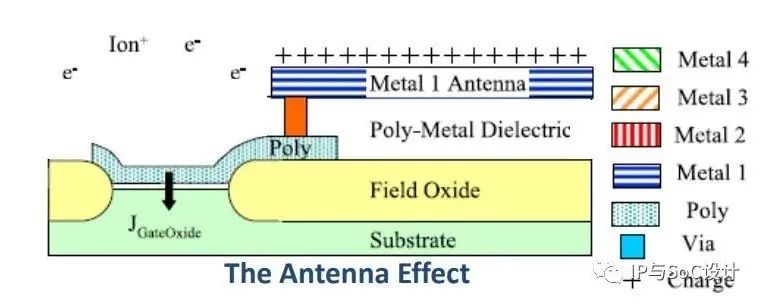

天線效應

·金屬化過程中連接到隔離柵極(多晶硅)的金屬段中電荷積累的現象

·這種現象發生在加工過程中,所以又稱為過程天線效應(PAE)

·當導電網充當天線時發生,放大電荷效應

·導電層接收電荷,稱為天線效應

天線效應產生的原因

·等離子蝕刻過程中的輝光放電會導致充電,當發生在導電層中時會導致天線效應,因此稱為等離子誘導/過程誘導損傷(PID)

·當未被氧化物屏蔽層覆蓋的導體層直接暴露于等離子體時,會發生充電

·在焊接等過程中,芯片受到一些屏蔽的保護

·但在制作過程中沒有這樣的保護,會導致天線效應

·對于鋁基工藝,PAE 在蝕刻階段突出,對于銅基工藝,PAE 在化學機械拋光 (CMP) 階段突出

·如果較高金屬層的區域通過較低金屬層連接到柵極,則較高金屬層的電荷會添加到較低金屬層,這也會導致 PAE,稱為累積天線效應

對設計的影響

·如果直接連接到柵極的層區域靜電荷通過柵極放電,則放電會損壞絕緣柵極的氧化物并導致芯片失效

·福勒-諾德海姆(FN)隧道電流將通過薄氧化物放電并對其造成損壞

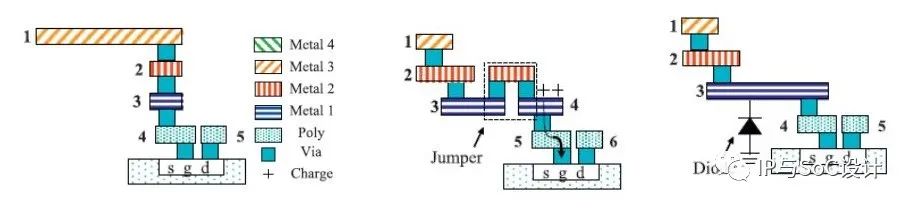

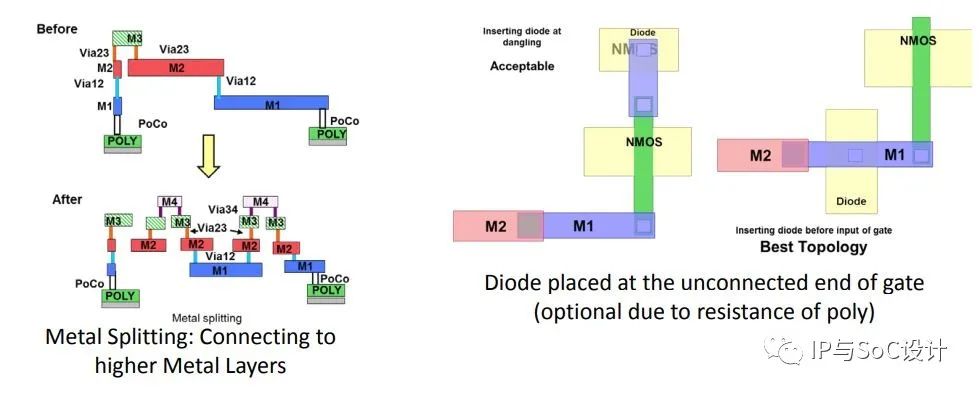

PAE 的補救措施

·為布線分配更高的金屬層

·較高的金屬層不會直接與Gate連接,通過Via連接連接各種金屬

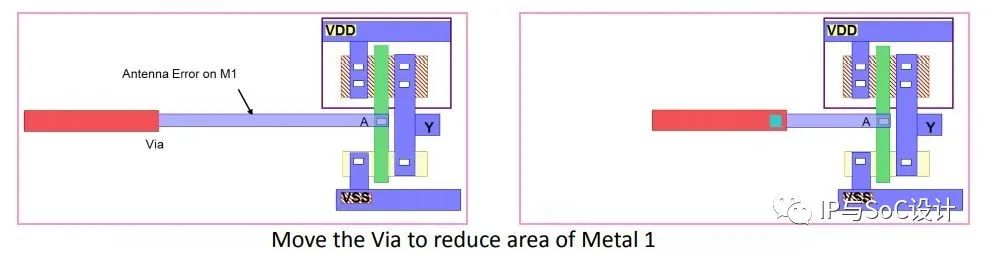

·插入跳線

·如果PAE位于較低層,則可以通過跳線將其連接到較高層來減少PAE

·跳線將減少連接到門的外圍金屬長度

·連接天線二極管

·如果是在高層,跳線就不行了,需要二極管

·一旦金屬/多晶硅上感應出額外的電荷,二極管就會將額外的電荷轉移到基板上

·但是對于緩沖器插入,較高的金屬層必須到達較低的金屬層(M1或M2)以連接到緩沖器的引腳并返回,并且可能沒有足夠的空間用于緩沖器插入

·布線后我們只進行天線檢查,因此緩沖區插入可能會導致擁塞和DRC違規

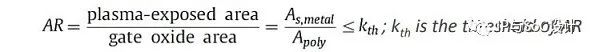

天線比率 (AR)

·防止金屬/多晶硅層蝕刻期間電荷積累的設計規則,限制了連接到柵極氧化物的金屬段的面積

·代工廠為其制造的芯片設定了最大允許的 AR

·AR 定義為等離子暴露面積 As,metal 與柵極氧化面積 Apoly 的比率,公式如下:

·此規則適用于連接到門的任何金屬段

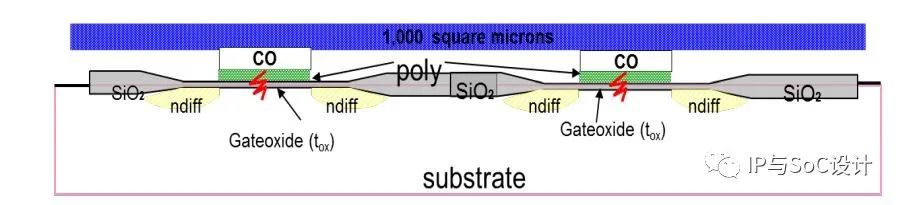

天線效應可能性示例

·假設代工廠設置最大允許天線比率為 500

·如果網絡有兩個輸入門,每個輸入門的面積為 1 平方微米,則任何連接到門且面積大于 1,000 平方微米的金屬層都存在工藝天線違規,因為它們會導致天線比率高于500

隨著技術的萎縮而占據主導地位

·當氧化物厚度減少時

·芯片中添加了更多的金屬結構

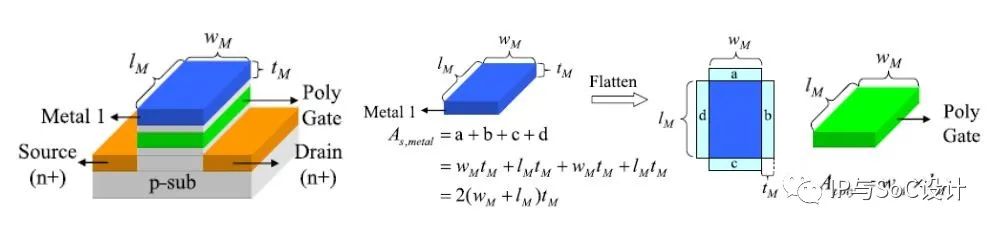

天線 (ANT) 規則

·天線比

·對于鋁的蝕刻階段(金屬沉積)

·在此步驟中,金屬頂部受到抗蝕劑保護,因此此過程的天線規則應基于金屬側壁區域

·用于化學機械拋光(CMP)階段的銅

·CMP過程中發生電荷積累

·在此過程中,金屬的側面受到保護,因此天線規則需要基于金屬的頂部表面積

·工藝中使用的金屬取決于技術

·從28nm開始鋁正在取代銅

PAE 作為制造過程的副作用

·等離子蝕刻機/離子注入機將電荷感應到與柵極氧化物連接的各種結構中

·這種感應電荷會破壞氧化層 - 造成永久性損壞

·導體層圖形蝕刻工藝

·累積電荷量與周長成正比

·灰化工藝

·累積電荷量與面積成正比

·灰化工藝去除導體層蝕刻工藝后剩余的光刻膠層

·在工藝后期,導體層圖形區域直接暴露于等離子體

·接觸蝕刻工藝

·累積電荷量與觸點總面積成正比

·接觸蝕刻工藝在兩個導體層之間挖孔

·在工藝后期,下導體層圖案上的所有接觸點區域直接暴露于等離子體

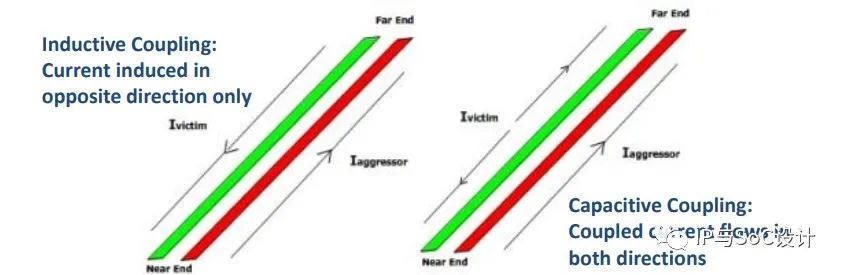

相聲

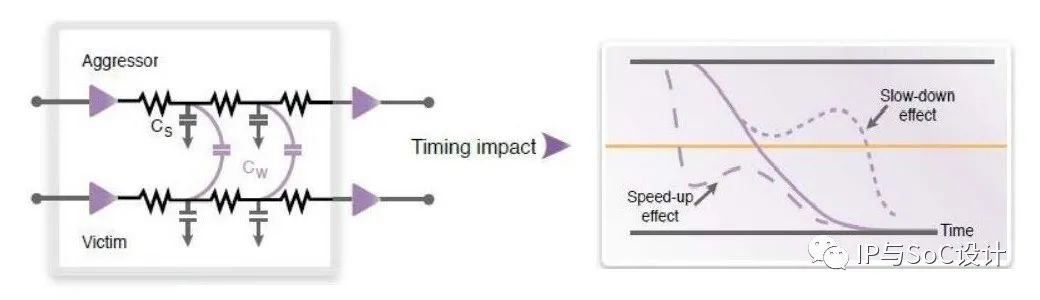

什么是串擾?

·指因電容/電感耦合而影響附近正在傳輸的另一個信號的信號

·串擾是兩條或多條相鄰線路之間不必要的能量耦合,它會改變所需的信號,也稱為 Xtalk

·發生在長的相鄰電線上

·可以解釋為能量從一條線到另一條線的耦合:

·互電容,Cm(由于電場)

·互感,Lm(由于磁場)

串擾對設計的影響

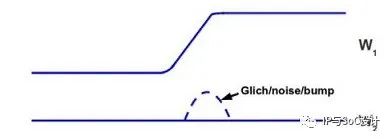

·功能故障

·噪聲引起的故障

·如果Glitch持續時間是時鐘周期持續時間,則額外的時鐘周期效應

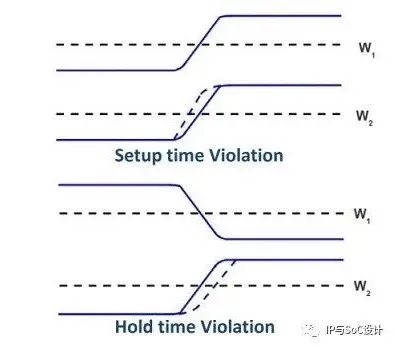

·計時違規

·如果攻擊者轉向與受害者相反的方向:建立時間違規

·如果攻擊者轉向與受害者相同的方向:保持時間違規

·如果受害線路的特性阻抗兩端沒有端接,則感應的雜散信號會在線路的兩端反射,并沿線路的相反方向傳播

·因此,反射的近端串擾最終可能出現在遠端,反之亦然

串擾的類型

·從實際信號線(干擾源)耦合到安靜的無源受害線路的能量,以便傳輸的能量“返回”到受害線路的起點。這稱為后向串擾或近端串擾

·能量從有源信號線(干擾源)耦合到安靜的無源受害線路,以便傳輸的能量“向前傳播”到受害線路的末端。這稱為前向串擾或遠端串擾

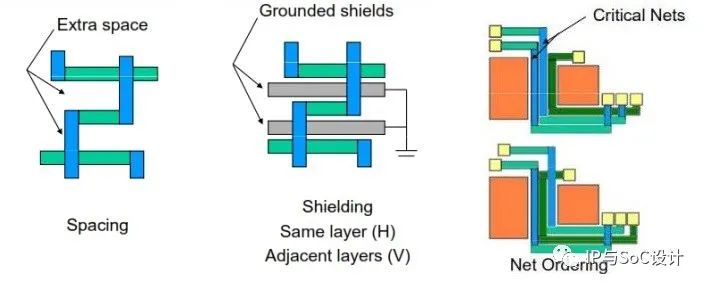

避免 Xtalk 的補救措施

·這是一個三維問題,所以高度、寬度和長度很重要

·可以通過改變關鍵網絡之間的間距來修復噪聲/碰撞違規

·通過地線將時鐘網絡(關鍵網絡)與其他網絡屏蔽開

·網絡重新排序

·避免長距離并行布線關鍵網絡

·將時鐘網絡(關鍵網絡)最小寬度從正常值修改為更大的值

·這使得路由器跳過時鐘網絡附近的網格以防止間距違規

·該技術不僅可以減少串擾,而且由于線寬更大、側壁電容更小,電阻也更低

·可以通過擴大受害者的規模(增加驅動強度)或縮小攻擊者的規模(減少驅動強度)來解決

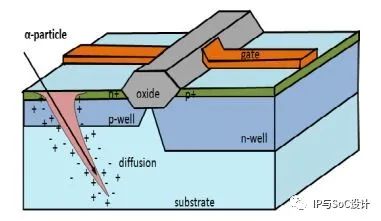

軟錯誤

軟錯誤(隨機粒子錯誤)

·軟錯誤是晶體管邏輯值錯誤變化的現象,可能由多種因素引起,包括信號電壓波動、電源噪聲、電感耦合效應等,但大多數軟錯誤由宇宙粒子撞擊芯片引起

·隨著技術的擴展,即使是低能粒子也會導致軟錯誤

·軟錯誤是由于包裝材料中雜質的 α 粒子或宇宙射線中子的粒子撞擊而發生的輻射引起的故障

·當粒子撞擊硅基板時,它們會產生空穴電子對,然后通過漂移和擴散機制由 PN 結收集

·收集到的電荷會產生瞬態電流脈沖,如果它足夠大,它可以翻轉存儲在狀態保存元件(位單元、鎖存器等)中的值

·這些冷門被稱為單項冷門(SEU)

對設計的影響

·軟錯誤可能導致不正確的結果、分段錯誤、應用程序或系統崩潰,甚至系統進入無限循環

·當組合電路中發生粒子撞擊時,結果是一個故障,然后該故障可以傳播到鎖存器,在鎖存器中可以對其進行計時并鎖存不正確的數據

避免軟錯誤的預防措施

·輻射強化:降低數字電路軟錯誤率的技術

·輻射硬化通常是通過增加節點處共享漏極/源極區域的晶體管的尺寸來實現的

自加熱

·如果電流流過電線,則由于電線的電阻,會產生熱量

·電線周圍的氧化物是熱絕緣體,因此熱量容易在電線中積聚

·更熱的電線電阻更大并且速度變慢

·電線自熱對大容量 CMOS IC 的電源線的影響可以忽略不計

·自加熱設計規則/自加熱限制交流電流密度以確保可靠性

·典型限值:JRMS < 1.5 MA/ cm2(對于鋁網)

·它限制了由于載流或任何附近互連的溫度升高而導致的不可避免的電遷移壽命下降

審核編輯:湯梓紅

-

晶體管

+關注

關注

77文章

9835瀏覽量

139486 -

寄生電容

+關注

關注

1文章

294瀏覽量

19434 -

NPN

+關注

關注

11文章

2665瀏覽量

47925 -

物理設計

+關注

關注

0文章

5瀏覽量

6901 -

寄生電阻

+關注

關注

1文章

20瀏覽量

2309

原文標題:博文速遞:Issues in Physical Design

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

物理設計中的問題詳解

物理設計中的問題詳解

評論