據最新報道,Cadence Design Systems 的工具已通過 Samsung Ondry 2nm 工藝的數字、定制模擬和背面布線認證。

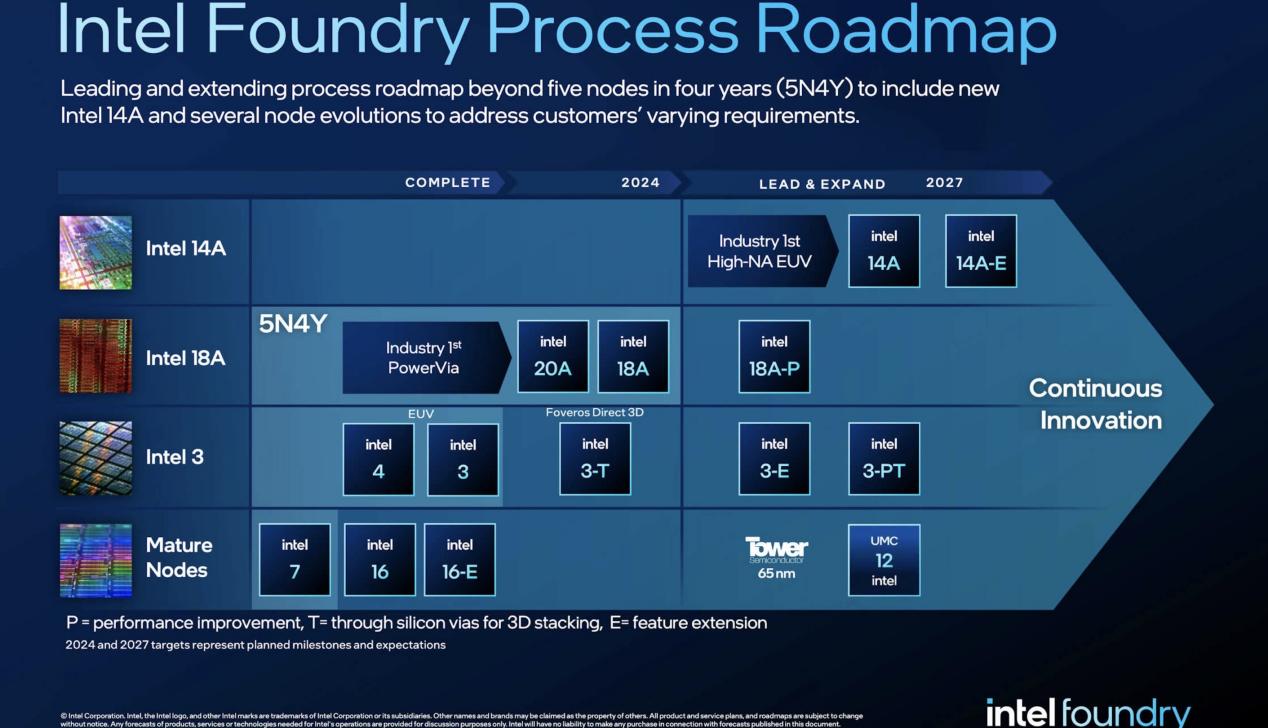

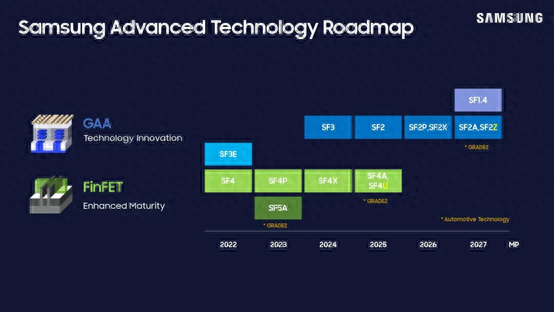

數字和定制模擬設計流程經過了 SF2 2nm 和 SF3 3nm 工藝認證,而完整的背面布線解決方案則為移動、汽車、人工智能和超大規模應用提供了下一代高性能芯片。

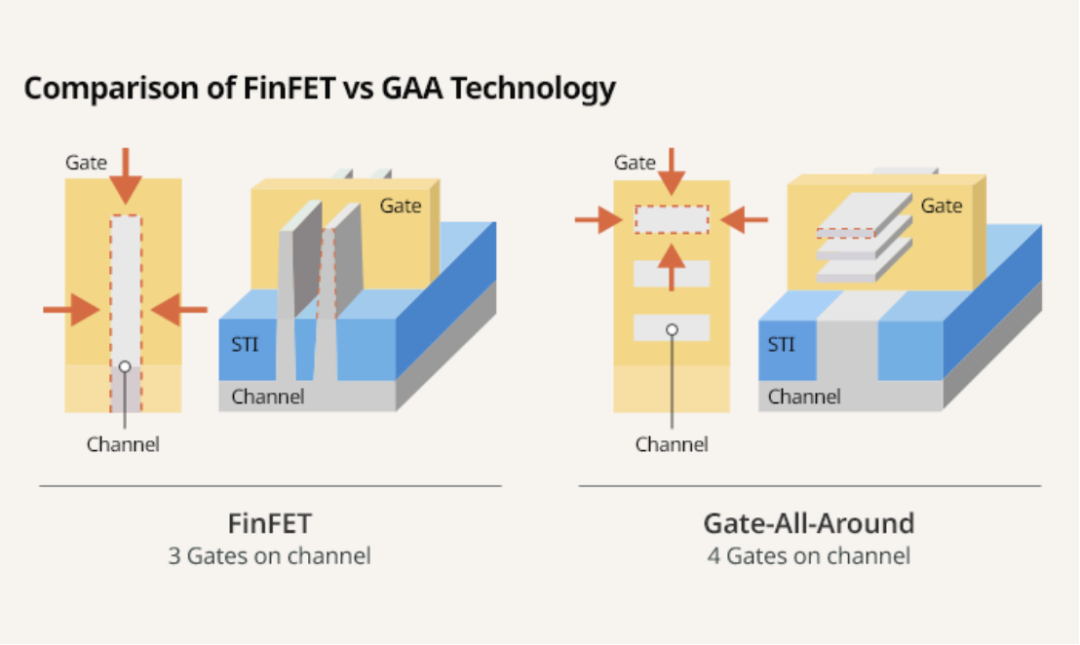

背面實施流程已通過成功的 SF2 測試芯片流片得到驗證。這是 2nm 設計的一項關鍵功能,但可能會受到三星、英特爾和臺積電缺乏布線的限制,而是在晶圓背面布線并使用過孔連接電源線。

該認證意味著工程師可以使用定制和模擬工具(包括基于 AI 的 Virtuoso Studio),根據經過認證的 SF2 和 SF3 流程,使用 PDK 設計 IC。

該流程包括 Genus 綜合解決方案、Modus DFT 軟件解決方案、Innovus 實施系統、Quantus 提取解決方案和 Quantus 場求解器、Tempus 時序簽核解決方案和 Tempus ECO 選項、Pegasus 驗證系統、Liberate 表征產品組合、Voltus IC 電源完整性解決方案和 Cadence Cerebrus 智能芯片瀏覽器。

單元交換支持可幫助設計人員對齊單元引腳以進行直接連接,以節省布線資源,同時支持各種組合的混合行解決方案,以最大限度地提高基于區域的設計規則,以及使用掩模移位單元和水平單元放置和細化走線的能力半履帶移動單元以減少位移。由于通過訂書釘插入增強型、修剪感知功能,還支持各種直線標準單元,以實現更高的密度并減少 IR 降。

背面布線依賴于 Innovus GigaPlace 引擎,該引擎可自動放置并合法化納米硅通孔 (nTSV) 結構,從而實現正面和背面層之間的連接。Innovus GigaOpt 引擎將背面層用于時序關鍵的長線,以提高芯片性能,而 Innovus NanoRoute 引擎本質上支持基于該技術的庫交換格式 (LEF) 中的規則的背面布線。

Quantus 提取解決方案完全支持背面層,使 Tempus 時序解決方案能夠簽核正面和背面層混合的設計,從而降低配電網上的壓降并提高正面金屬層的可布線性。

三星電子代工設計技術團隊副總裁 Sangyun Kim 表示:“通過與 Cadence 的持續合作,我們不斷尋找新方法來幫助我們共同的客戶加速下一代設計創新。” “這一背面設計流程的成功推出,得到了 Cadence 數字流程的全面支持,讓客戶能夠從我們先進的 SF2 技術中獲益。”

Cadence 數字與簽核集團公司副總裁 Vivek Mishra 表示:“設計人員可以利用我們與 Samsung Foundry 在完整 RTL 到 GDS 流程和 SF2 技術方面的合作來加快產品上市速度。” “我們已經看到了成功的流片,我們期待看到我們的客戶使用我們的最新技術取得更多的設計成功。”

定制/模擬設計工具為客戶提供了多種優勢,例如更好的拐角模擬管理、統計分析、設計中心和電路優化;支持現代計算場以及私有和公共云配置上的并行操作;整個布局環境具有更好的性能和可擴展性;混合信號 OpenAccess 設計套件,可與 Innovus 實施的布局布線引擎無縫集成,從而提高結果質量;總結了 EM-IR 信息,其中突出顯示了電阻值、金屬層、寬度和長度信息的違規情況和詳細信息;以及有關電路性能和可靠性的反饋。

“通過我們與 Cadence 的最新合作,我們看到早期客戶利用 Cadence 認證的設計流程以及我們先進的 SF2 和 SF3 工藝技術提高了生產力,”Kim 說。“借助新的 PDK,我們使下一代移動、汽車、人工智能和超大規模設計的開發人員能夠更輕松地采用我們的技術并更快地將創新推向市場。”

-

芯片

+關注

關注

455文章

50851瀏覽量

423916 -

電源完整性

+關注

關注

9文章

209瀏覽量

20731 -

三星

+關注

關注

1文章

1534瀏覽量

31265

原文標題:三星2nm,走向背面供電

文章出處:【微信號:芯長征科技,微信公眾號:芯長征科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

2nm突圍,背面供電技術的首個戰場

三星2nm,走向背面供電

三星2nm,走向背面供電

評論