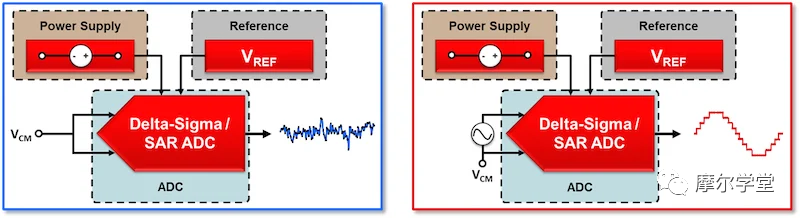

在考慮ADC中的噪聲時,幾乎可以將ADC視為混頻器。如果有噪聲從各種門口中的任何一個進入ADC,則噪聲可以表現在輸出數據的FFT中。

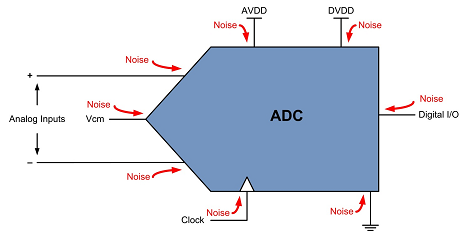

圖1顯示了我們之前討論的噪聲門口,其中包括電源輸入、模擬輸入和時鐘。但是,在使用ADC時,我錯過了更多我們絕對應該考慮的門口。第一種是共模電壓(Vcm)輸出,為模擬輸入提供共模電平。接下來是數字輸入和輸出(I/O),它們可能是噪聲進入ADC的路徑。最后,有一個門口可能是最容易被忽視的門口之一——地面或電路。

圖1

額外的ADC噪聲“門口”

如今,許多高速ADC都使用Vcm輸出為ADC模擬輸入提供共模基準電壓。它是ADC輸入最小到最大范圍內的中點電壓。該引腳通常需要一個大約0.1μF的去耦電容。這為輸出穩定性以及高頻噪聲的濾波提供了一個主導極點。進行適當的去耦非常重要,因為該節點為ADC模擬輸入的噪聲提供了潛在的直接線路。即使它是輸出,噪聲也會強行進入ADC的內部偏置電路。

除電容外,許多具有兩個或更多通道的ADC還需要少量串聯電阻,每次連接Vcm輸出到每個通道。這也是降噪的一種形式,因為它通常有助于減少ADC通道之間的串擾。另一種說法是,額外的串聯電阻有助于改善通道間的隔離,使來自一個通道的信號不會進入另一個通道。

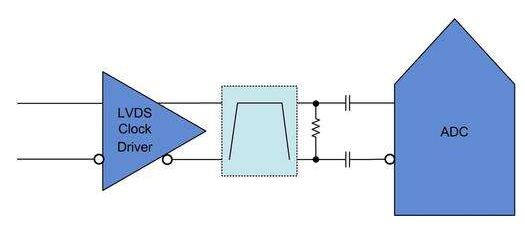

ADC的數字I/O線也是噪聲的門口。數字I/O有幾種不同的功能,因此噪聲通過每種功能進入ADC的方式也不同。最明顯的是數字輸出接口。對于具有CMOS輸出的ADC來說,由于其單端實現,這更令人擔憂。

通常,具有LVDS輸出的ADC或采用串行JESD204B接口的ADC對噪聲耦合的免疫力要強得多。除數字輸出外,ADC內部的數字電路數量也越來越多,這為通過控制線的噪聲提供了一些潛在的入口點。隨著數字內容的增加,需要為這些功能提供 I/O。有時,額外的I/O是通過SPI(串行端口接口)完成的。有時,SPI 無法處理所有需要處理的問題。

關于SPI的附帶說明:SPI不僅是一個潛在的噪聲門,還可能導致其他轉換問題。各種建議表示,在系統運行時(進行轉換時)不要訪問ADC的SPI。

其他I/O包括模式控制、掉電、待機、超量程指示器、同步引腳等。這些都是需要注意的事項,除了良好的布局實踐以避免噪聲耦合外,還要確保使用適當的去耦。

可能最容易被忽視的門口(我上次自己當然也忽略了這一點)是ADC的地面。請注意,當我說接地時,我指的是電路通用。另請注意,通常有多個接地連接,例如模擬接地和數字接地。對于這兩個理由,您有時需要考慮它們粘合或捆綁在一起的位置。這是某個時候另一個博客的主題。

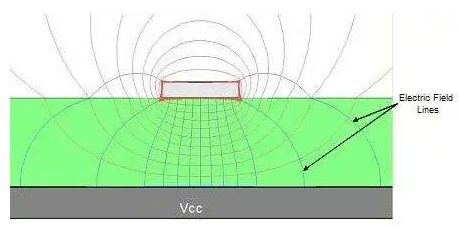

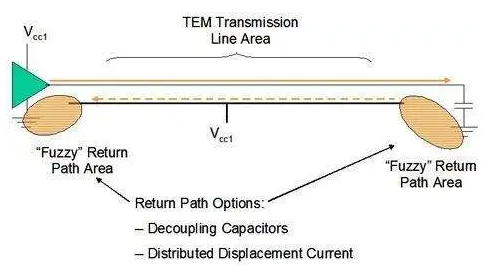

地面通常被認為是一個堅實的參考點。然而,地并不總是一個穩定的參考點,并且可能允許噪聲進入ADC。在系統設計和布局中注意接地層非常重要,以確保有足夠的平面面積而不會中斷,并且有足夠的接地過孔以允許適當的電流返回路徑。在設計中必須考慮所有電流返回路徑,而不是假設接地是一個穩定的參考點。

如果沒有適當的系統設計,噪聲可能會存在于接地層中,并可能進入ADC。

流向其他地方的電流,而不是你認為它將或應該流動的地方,實際上并不是最嚴格意義上的噪音,但它顯然是麻煩。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17724瀏覽量

250296 -

adc

+關注

關注

98文章

6501瀏覽量

544741 -

混頻器

+關注

關注

10文章

680瀏覽量

45696

發布評論請先 登錄

相關推薦

其中一個ADC通道噪聲很大

AD7196:2 通道、 4.8 kHz 、超低噪聲、 集成 PGA 的 24 位 Σ-? 型 ADC

ADC3910Dx和ADC3910Sx小型單通道和雙通道ADC數據表

ADC3664 14位、125MSPS、低噪聲、低功率雙通道ADC數據表

ADC368x 18位、0.5至65MSPS、低噪聲、極低功率雙通道ADC數據表

ADC366x 16位、0.5MSPS至65MSPS、低噪聲、低功率雙通道ADC數據表

ADC364x 14位、10至65MSPS、低噪聲、低功率雙通道ADC數據表

ADC3644 14位125MSPS低噪聲低功耗雙通道ADC數據表

ADC3660 16位、0.5至65MSPS、低噪聲、低功率雙通道ADC數據表

如何為ADC噪聲提供通道

如何為ADC噪聲提供通道

評論