IP核的開發(fā)過程中,面臨著許多關(guān)鍵技術(shù),比如IP核的規(guī)格定義、基于接口的設(shè)計(jì)、IP核測試存取結(jié)構(gòu)標(biāo)準(zhǔn)、IP核的驗(yàn)證與打包等。對于IP核的驗(yàn)證,主要是建立參照模型和測試平臺,然后進(jìn)行回歸測試和形式驗(yàn)證。這里參照的模型主要用于對系統(tǒng)功能進(jìn)行驗(yàn)證以及和RTL模型的對照驗(yàn)證,該模型主要用Verilog HDL等語言來構(gòu)造。測試平臺的建立與子模塊設(shè)計(jì)并行,搭建驗(yàn)證環(huán)境和開發(fā)測試用例,并針對IP核的行為級模型對測試環(huán)境和測試用例進(jìn)行調(diào)試,從而同步準(zhǔn)備好用來仿真測試RTL級IP核的驗(yàn)證環(huán)境和測試用例。

仿真和驗(yàn)證是開發(fā)任何高質(zhì)量的基于 FPGA 的 RTL 編碼過程的基礎(chǔ)。在本系列文章中,我們將分享我們設(shè)計(jì)過程中的關(guān)鍵步驟,并將基于虹科以太網(wǎng)IP核產(chǎn)品組合進(jìn)行介紹。

整個過程的關(guān)鍵步驟如下:

面向?qū)嶓w/塊的仿真:通過在每個輸入信號上生成激勵并驗(yàn)證 RTL 代碼行為是否符合預(yù)期,對構(gòu)成每個 IP 核的不同模塊進(jìn)行實(shí)體/塊的仿真。

面向全局的仿真:一旦不同的模塊被單獨(dú)驗(yàn)證,則意味著下一步將整個IP仿真為單個 UUT(被測試單元)。

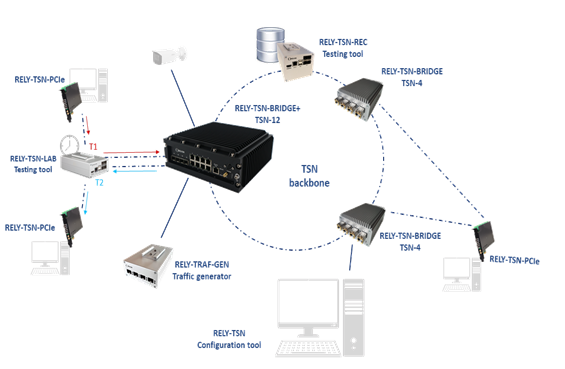

(On)硬件測試:盡管擴(kuò)展的仿真計(jì)劃提供了良好的可信度,但仍有許多corner的情況無法在虛擬環(huán)境中驗(yàn)證。對于這些情況,需要基于硬件的測試計(jì)劃,這也是獲得高質(zhì)量結(jié)果的最后一步。

在本篇文章中,我們將描述第一步:IP 仿真的實(shí)體或塊級別是如何完成的。

面向?qū)嶓w或塊的仿真

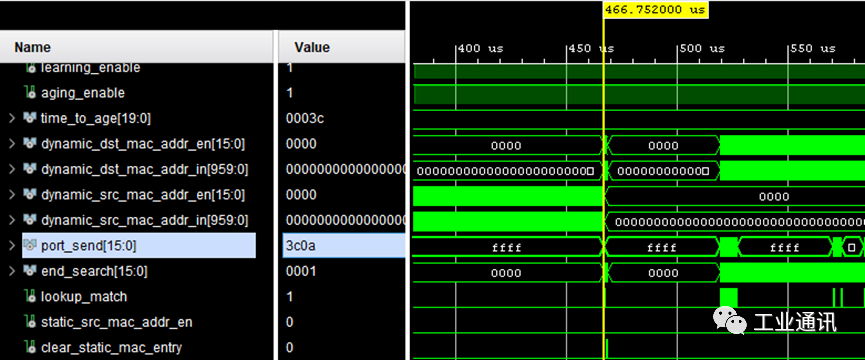

“面向?qū)嶓w或塊的仿真”這一步驟意味著驗(yàn)證在 IP 核內(nèi)具有特定操作的特定實(shí)體或模塊的正確操作。每個 IP 核都由許多實(shí)體或塊組成,為了測試它們,每個實(shí)體會有不同的測試平臺,通過在輸入受到刺激時觀察設(shè)計(jì)的輸出來執(zhí)行設(shè)計(jì)。這將有助于檢查預(yù)期的行為。

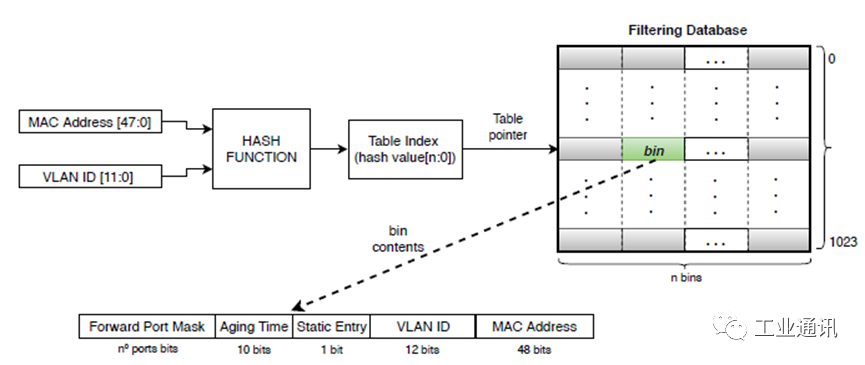

舉個例子就可以很好地理解這個步驟。下面我們先介紹虹科以太網(wǎng)交換機(jī) IP 核的過濾數(shù)據(jù)庫。過濾數(shù)據(jù)庫存儲 MAC 地址及其相關(guān)信息以做出幀轉(zhuǎn)發(fā)決策。它是一個基于哈希的存儲器,每個地址條目都有一些存儲過濾數(shù)據(jù)的 bin。該哈希算法還生成過濾數(shù)據(jù)庫內(nèi)存的索引。

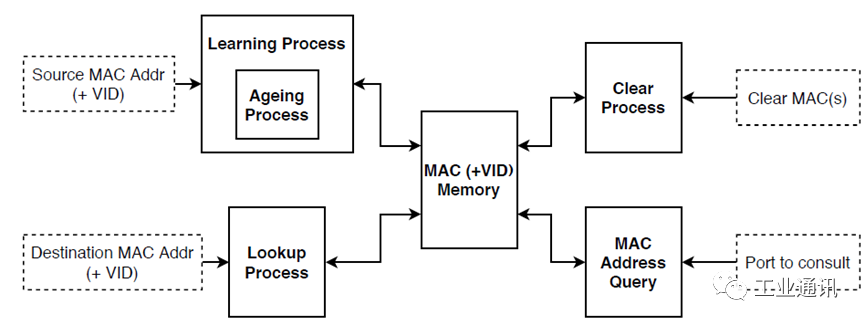

過濾數(shù)據(jù)庫執(zhí)行有三個主要過程:學(xué)習(xí)、查找和老化

學(xué)習(xí)過程負(fù)責(zé)在滿足不同條件時保存幀。

查找過程是在過濾數(shù)據(jù)庫中搜索并獲得幀的轉(zhuǎn)發(fā)端口掩碼的過程。

老化過程根據(jù)給定的時間段刪除舊的 MAC 條目。

在這個仿真MAC表的具體案例中,請始終嘗試測試構(gòu)成過濾數(shù)據(jù)庫功能的所有機(jī)制。從這個意義上說,就像學(xué)習(xí)不同的MAC,不同的查詢、老化是并行完成的,最后需要清除MAC表并驗(yàn)證所有條目都已刪除。此外,研究并始終能夠測試可能的corner案例也十分重要。

測試和驗(yàn)證復(fù)雜 FPGA 設(shè)計(jì)的第二個關(guān)鍵步驟將在下一篇文章中展開介紹。一旦形成 IP 核的所有實(shí)體都按預(yù)期工作,全局仿真就會發(fā)揮作用。

未完待續(xù)

IP核可以使開發(fā)人員減少工作量,并縮短產(chǎn)品上市時間。虹科目前已有豐富的IP核產(chǎn)品組合,包括TSN IP核、HSR/PRP IP核、以太網(wǎng)IP核、冗余IP核等,可以輕松集成到用戶的FPGA中。若想了解更多信息,歡迎通過sales@hkaco.com聯(lián)系虹科工業(yè)控制團(tuán)隊(duì)!

-

FPGA

+關(guān)注

關(guān)注

1630文章

21796瀏覽量

605727 -

仿真

+關(guān)注

關(guān)注

50文章

4124瀏覽量

133940

發(fā)布評論請先 登錄

相關(guān)推薦

虹科方案 僅需4個步驟!輕松高效搭建虹科TSN測試網(wǎng)絡(luò)

虹科方案 | 精準(zhǔn)零部件測試!多路汽車開關(guān)按鍵功能檢測系統(tǒng)

EasyGo實(shí)時仿真丨PCS儲能變流器控制仿真應(yīng)用

【干貨分享】硬件在環(huán)仿真(HiL)測試

虹科干貨 輕松掌握PCAN-Explorer 6,dll調(diào)用一文打盡!

虹科技術(shù)前沿 TSN網(wǎng)絡(luò)中時間感知整形器的性能驗(yàn)證實(shí)測

虹科干貨 | 如何測試與驗(yàn)證復(fù)雜的FPGA設(shè)計(jì)(1)——面向?qū)嶓w或塊的仿真

虹科干貨 | 如何測試與驗(yàn)證復(fù)雜的FPGA設(shè)計(jì)(1)——面向?qū)嶓w或塊的仿真

評論