在本篇文章中,我們將展示兩種可在FPGA上實(shí)現(xiàn)的COTS IEC 62439-3交換機(jī)IP核的延遲的比較。第一種是混合使用直通交換和存儲(chǔ)-轉(zhuǎn)發(fā)交換架構(gòu),第二種則是僅基于存儲(chǔ)-轉(zhuǎn)發(fā)交換技術(shù)。

01

可靠的以太網(wǎng)技術(shù)——HSR&PRP

如今,HSR/PRP等可靠的以太網(wǎng)網(wǎng)絡(luò)正在獲得許多工業(yè)自動(dòng)化應(yīng)用的認(rèn)可。這種演變的一個(gè)有力證據(jù)是國(guó)際電工委員會(huì)采用了基于高可靠性無(wú)縫冗余 (HSR)以太網(wǎng)的協(xié)議和用于變電站自動(dòng)化的并行冗余協(xié)議 (PRP) (IEC 62439-3 第 5 和 4 條)。這兩種協(xié)議都提供零切換延遲時(shí)間,在故障情況下不丟失幀,并被當(dāng)作在第 2 層進(jìn)行網(wǎng)絡(luò)監(jiān)督的強(qiáng)大手段。

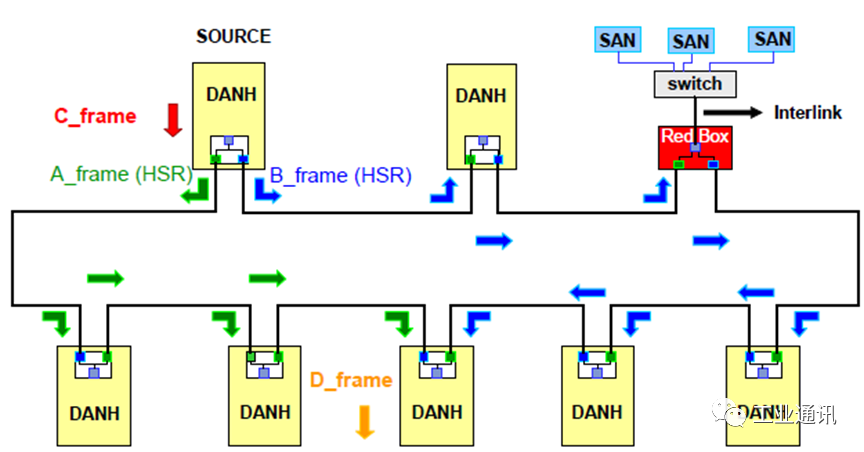

HSR單播流量環(huán)配置示例

HSR幀與傳統(tǒng)的以太網(wǎng)基礎(chǔ)設(shè)施不兼容,而PRP則允許通過(guò)兩個(gè)傳統(tǒng)的以太網(wǎng)網(wǎng)絡(luò)發(fā)送重復(fù)幀。因此,PRP 的應(yīng)用領(lǐng)域更為廣泛,盡管它并不是專門為“實(shí)時(shí)”以太網(wǎng)環(huán)境設(shè)計(jì)的。

“實(shí)時(shí)”意味著在信號(hào)發(fā)生后的可預(yù)測(cè)時(shí)間內(nèi)對(duì)其進(jìn)行響應(yīng)。例如,現(xiàn)代數(shù)字控制回路需要低于10μs的反應(yīng)時(shí)間。最新的基于以太網(wǎng)的控制協(xié)議如EtherCAT或Sercos III等往往基于硬件來(lái)實(shí)現(xiàn)可預(yù)測(cè)的同步行為和極低的延遲時(shí)間。

HSR旨在滿足為Process Bus設(shè)置的嚴(yán)格通信要求,它可以將每個(gè)間隔層中的智能電子設(shè)備 (IED) 互連。

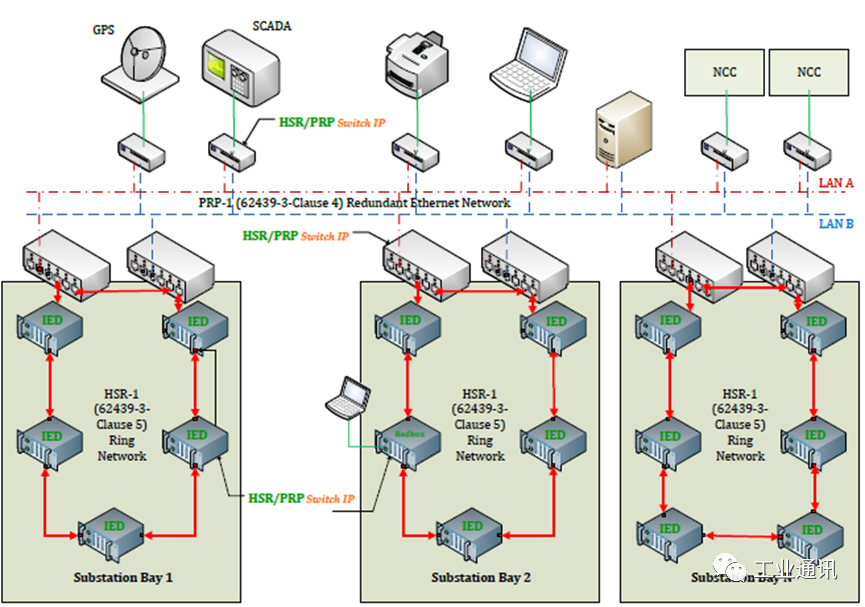

PRP適用于Station和Inter-Bay Buses。由于該協(xié)議的靈活性,它可以連接許多異構(gòu)設(shè)備。

為了保持通信中的冗余,PRP和 HSR 網(wǎng)絡(luò)之間的互連是使用冗余網(wǎng)關(guān)執(zhí)行的。每個(gè)HSR鏈路使用兩個(gè)網(wǎng)關(guān)設(shè)備連接到每個(gè)PRP LAN。因此,避免了潛在的“單點(diǎn)故障”問(wèn)題。

通過(guò)HSR和PRP的變電站網(wǎng)絡(luò)通信

02

直通與存儲(chǔ)轉(zhuǎn)發(fā)

直通和存儲(chǔ)轉(zhuǎn)發(fā) L2 交換都基于數(shù)據(jù)包的目標(biāo) MAC 地址做出轉(zhuǎn)發(fā)決策。它們之間的主要區(qū)別是:

存儲(chǔ)轉(zhuǎn)發(fā)交換在收到整個(gè)數(shù)據(jù)包后做出決定。

直通交換在分析目標(biāo) MAC 地址后做出轉(zhuǎn)發(fā)決定,該地址位于幀的第一部分。

在存儲(chǔ)轉(zhuǎn)發(fā)交換中,延遲時(shí)間包括接收整個(gè)幀所需的時(shí)間。因此,與直通交換相比,存儲(chǔ)轉(zhuǎn)發(fā)交換的延遲時(shí)間更長(zhǎng)。

03

轉(zhuǎn)發(fā)延遲時(shí)間

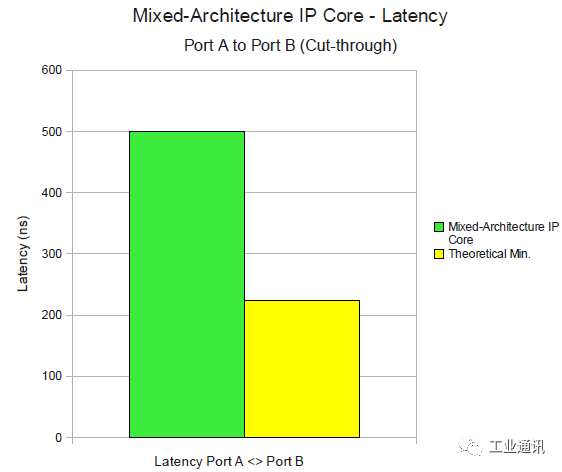

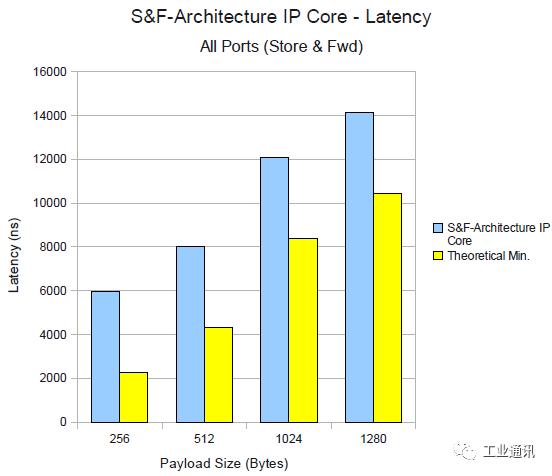

在Xilinx FPGA上的虹科HSR-PRP IP核中實(shí)現(xiàn)這兩種方法(一種混合直通和存儲(chǔ)轉(zhuǎn)發(fā),另一種是純存儲(chǔ)轉(zhuǎn)發(fā)),結(jié)果如下:

混合直通和存儲(chǔ)轉(zhuǎn)發(fā)延遲

存儲(chǔ)轉(zhuǎn)發(fā)延遲

因此,可以說(shuō)虹科HSR-PRP IP核實(shí)現(xiàn)了專為PRP和HSR協(xié)議設(shè)計(jì)的交換架構(gòu)。

理論上的最小延遲時(shí)間是通過(guò)考慮以太網(wǎng)幀的強(qiáng)制字段來(lái)計(jì)算的,這意味著必須對(duì)這些字段進(jìn)行分析以做出交換決策。在這種情況下,在直通中,時(shí)間與幀長(zhǎng)度無(wú)關(guān),因此它將是恒定的。在純存儲(chǔ)轉(zhuǎn)發(fā)方法的情況下,在開(kāi)始重傳之前需要存儲(chǔ)整個(gè)幀,因此延遲取決于幀長(zhǎng)度。可以看出,它比優(yōu)化的直通交換架構(gòu)大一個(gè)數(shù)量級(jí)。

結(jié)論

1

分析表明,將直通與存儲(chǔ)轉(zhuǎn)發(fā)方法相結(jié)合的定制架構(gòu)在任何情況下都能提供最佳的延遲時(shí)間。

2

FPGA在這些新協(xié)議中的作用至關(guān)重要。一方面,它們?cè)试S低延遲、靈活和可擴(kuò)展的解決方案來(lái)滿足這些標(biāo)準(zhǔn)中設(shè)定的嚴(yán)格要求。另一方面,當(dāng)工業(yè)制造商結(jié)合新協(xié)議和特定協(xié)議為市場(chǎng)提供設(shè)備時(shí),F(xiàn)PGA能夠減少上市時(shí)間和風(fēng)險(xiǎn)。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21759瀏覽量

604348 -

交換機(jī)

+關(guān)注

關(guān)注

21文章

2646瀏覽量

99805

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

反射內(nèi)存交換機(jī)與普通交換機(jī)的區(qū)別

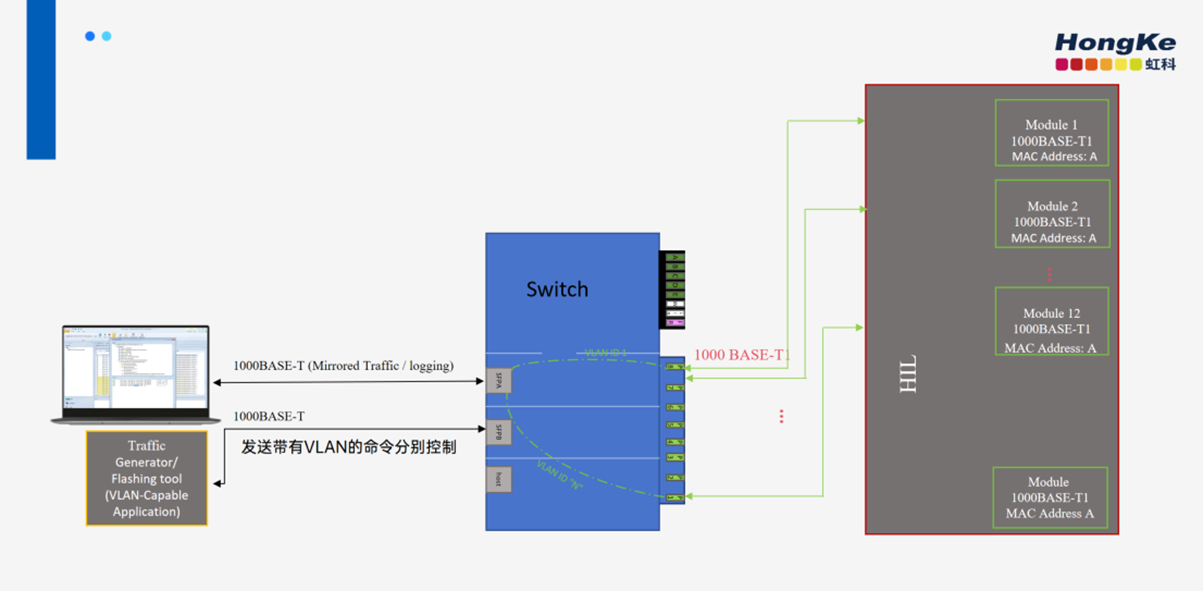

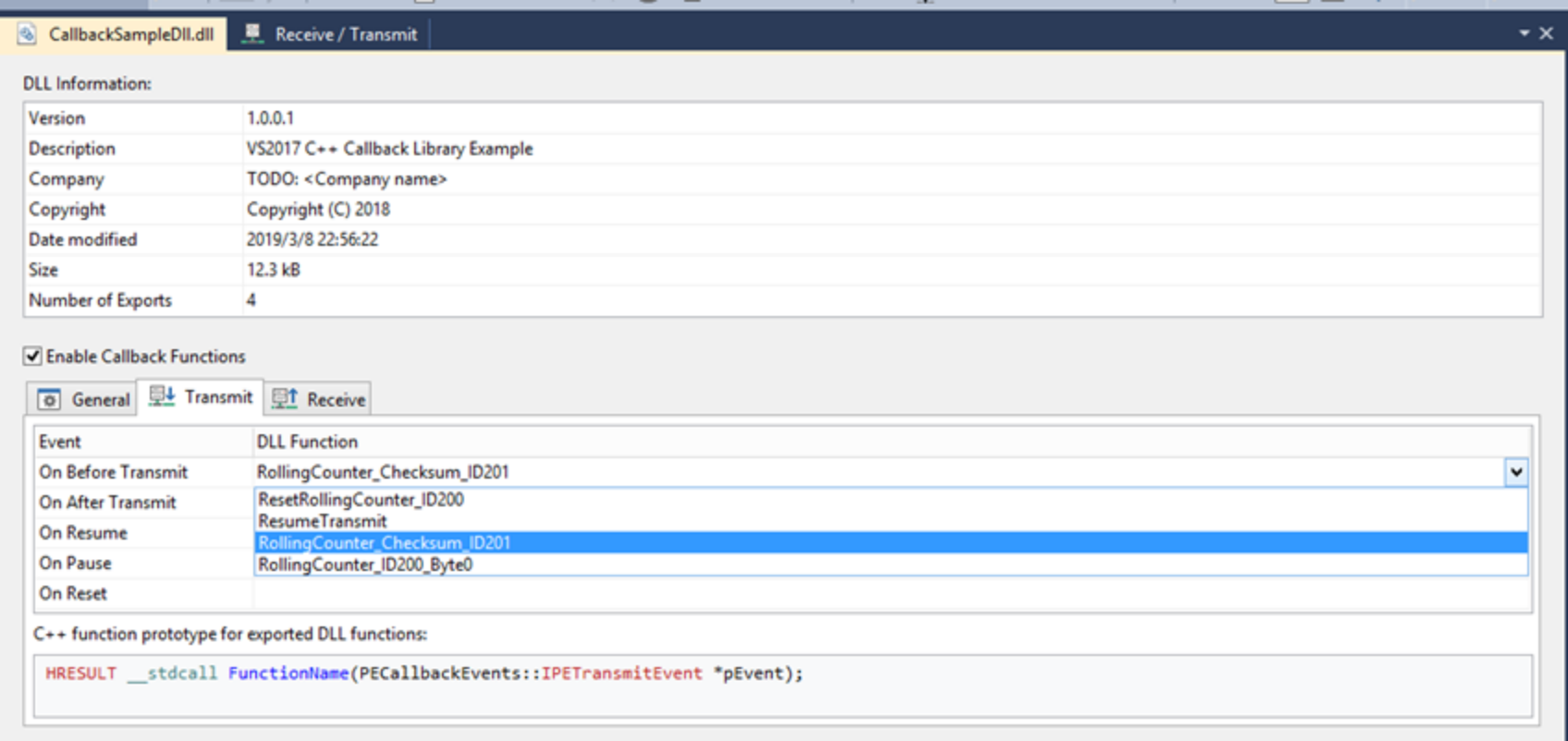

虹科干貨 輕松掌握PCAN-Explorer 6,dll調(diào)用一文打盡!

虹科方案 領(lǐng)航智能交通革新:虹科PEAK智行定位車控系統(tǒng)Demo版亮相

車載以太網(wǎng)交換機(jī)入門基本功(3)—VLAN 轉(zhuǎn)發(fā)

虹科應(yīng)用 增強(qiáng)型以太網(wǎng)交換機(jī):如何實(shí)現(xiàn)同IP控制的高效網(wǎng)絡(luò)管理?

直通網(wǎng)線的作用及制作步驟

什么是以太網(wǎng)交換機(jī)中的網(wǎng)絡(luò)延遲

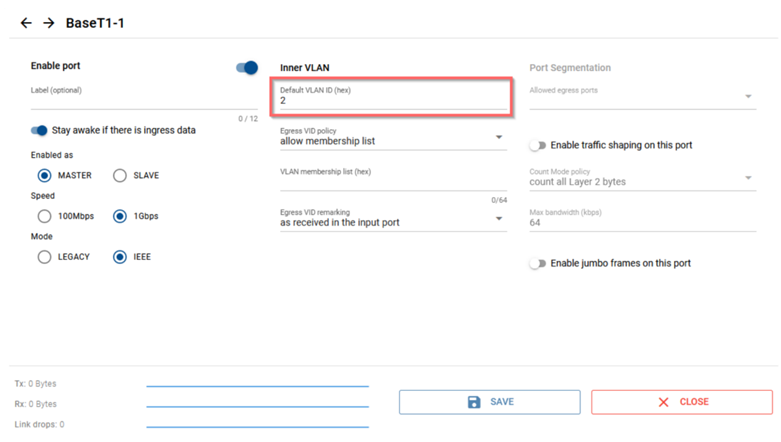

虹科案例丨VLAN不再難懂:一臺(tái)轉(zhuǎn)換器+交換機(jī)輕松解鎖VLAN配置

深入探索InfiniBand網(wǎng)絡(luò)、HDR與IB技術(shù)

虹科干貨丨輕松掌握PCAN-Explorer 6,dll調(diào)用一文打盡!

虹科方案 | 符合醫(yī)藥行業(yè)規(guī)范的液氮罐運(yùn)輸和存儲(chǔ)溫度監(jiān)測(cè)解決方案

交換機(jī)芯片的原理是什么

交換芯片是什么意思 交換芯片的功能有哪些

虹科干貨|HK-TE-200x系列FAQ(一):如何定義EES的VLAN?

虹科干貨 | FPGA實(shí)現(xiàn)直通交換與存儲(chǔ)轉(zhuǎn)發(fā)的切換延遲

虹科干貨 | FPGA實(shí)現(xiàn)直通交換與存儲(chǔ)轉(zhuǎn)發(fā)的切換延遲

評(píng)論