在電路板放置分立的去耦電容可以靈活地調(diào)整電源供電系統(tǒng)的阻抗,實現(xiàn)較低的電源地噪聲。然后,如何選擇擺放電容位置、選用多少及選用什么型號的去耦電容仍是設計者需要考慮的問題。

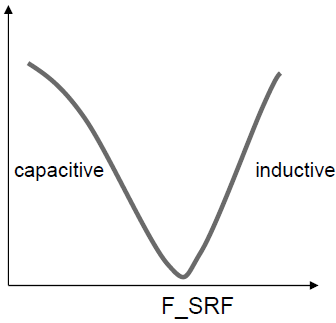

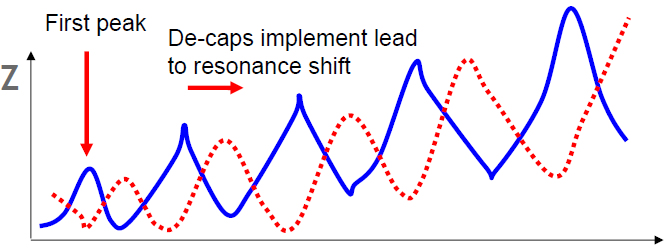

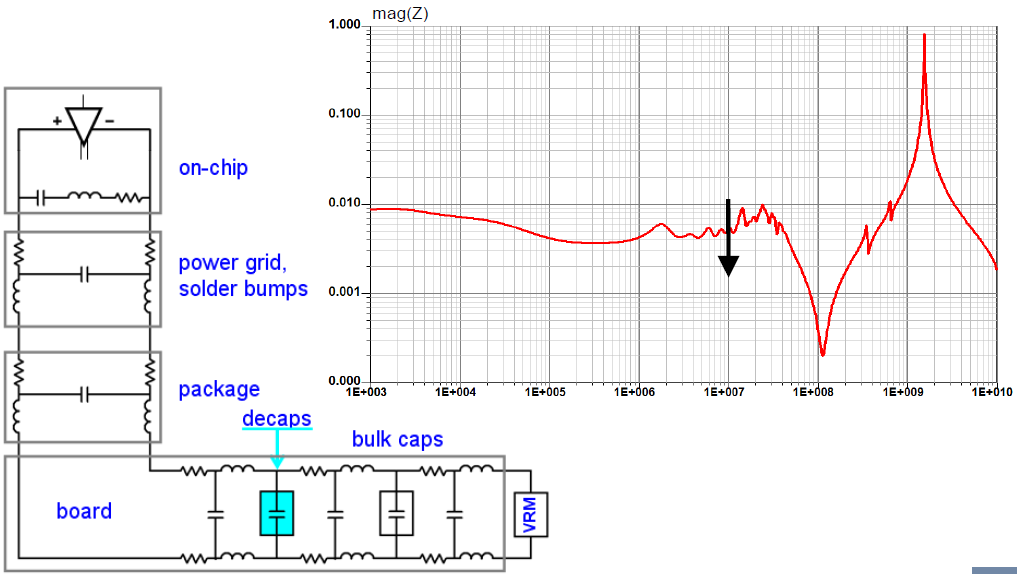

因此,為了對一個特定的設計尋求最佳的去耦解決方案,選用合適的仿真軟件及進行大量的電源供電系統(tǒng)的仿真模擬往往是必須的。去耦電容的阻抗呈現(xiàn)下圖所示的V字形特性,在自諧振頻率之前是容性的,愛自諧振頻率點之后是感性的。在電容方案選型時,可以利用去耦電容阻抗在諧振點最低的特點,合理組合不同容值和位置的電容以抵消PDN諧振峰值,改變系統(tǒng)諧振點的分布,并使在關心的頻段范圍內(nèi)這個PDN沒有明顯的諧振。

利用電容自諧振頻率來抑制PDN諧振

電容是最重要的電源阻抗控制優(yōu)化器件,接下來我們將通過一個例子進一步闡述其在實際產(chǎn)品中的應用方法。

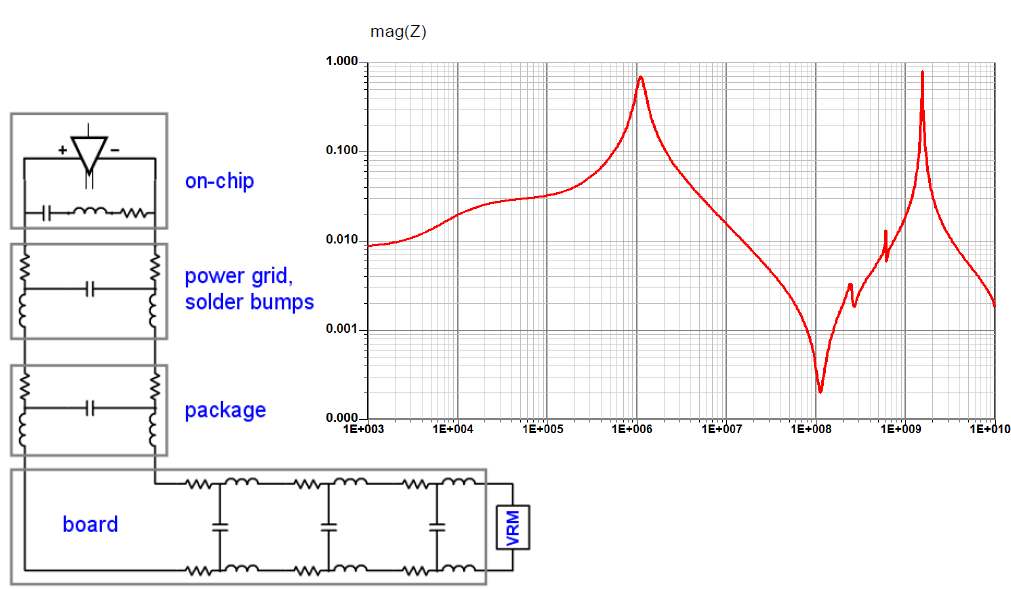

下圖中是利用電容自諧振頻率點阻抗最低的特點來抑制PDN諧振的一般方法。下圖中通過芯片自阻抗曲線,可以發(fā)現(xiàn)其在1MHZ左右有個明顯的諧振,由于常用的470uF電解電容的自諧振頻率基本上位于1MHZ附近,所以我們在PCB上的VRM附件安裝一顆470uF的去耦電容(Bulk),并從新提取芯片端自阻抗曲線。

沒有電容的情況

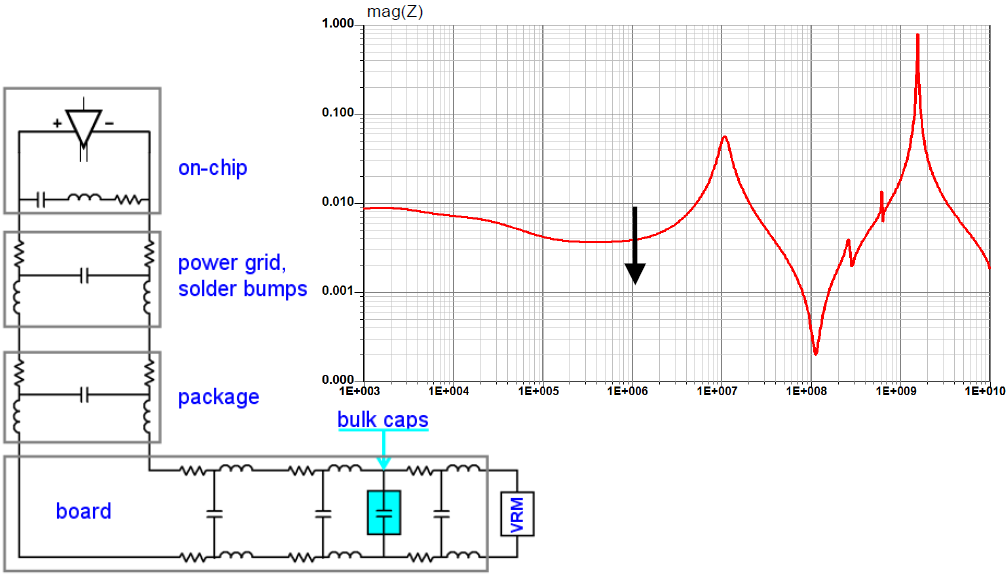

增加Bulk 470uF電容的情況

Bulk 470uF電容添加后的阻抗曲線,可以發(fā)現(xiàn)1MHZ附近的諧振峰明顯的消失,但是10MHZ附近出現(xiàn)了新的諧振峰。此時可以通過板上合適的位置放置一些容量比較小的高頻陶瓷電容MLCC電容100nf-22uf,來進一步抑制10MHZ附近的諧振。下圖顯示了通過高頻電容的組合能有效的消除10MHZ出的諧振峰。

從上面的例子分析鐘我們可以看出利用頻域仿真獲取PDN網(wǎng)絡的輸入阻抗,并利用阻抗諧振針對性性地添加板基去耦電容是改善PDN性能的行之有效的手段方法。

電源噪聲從頻譜上來看是一個很寬的頻率范圍內(nèi)的噪聲,頻域分析需要在一定的范圍內(nèi)考慮;基于網(wǎng)絡參數(shù)法的目標阻抗法是PDN的頻域分析中最常用的方法。PDN的目標阻抗通常需要根據(jù)器件工作電流、噪聲容限等參數(shù)確定;根據(jù)器件中最大工作電流附近估算的目標阻抗只適用于中低頻的分析,高頻的目標阻抗需要較為準確的器件工作時的電流模型進行計算;從目前的發(fā)展來看,芯片的工作電壓越來越低,最大電流越來越大,因此核心電源的目標阻抗越來越小。

-

電容

+關注

關注

100文章

6133瀏覽量

152231

發(fā)布評論請先 登錄

相關推薦

串聯(lián)諧振特點全面介紹

串聯(lián)諧振和并聯(lián)諧振特性對比及介紹

串聯(lián)諧振和并聯(lián)諧振的特點區(qū)別

電路發(fā)生諧振的條件是什么

巧了不是,原來你也不知道啥是去耦電容的“濾波半徑”啊!

頻率大于諧振頻率電路呈什么性

串聯(lián)諧振的應用在哪里

串聯(lián)諧振的原理是什么

如何判斷諧振回路處于諧振狀態(tài)

電力系統(tǒng)為什么會產(chǎn)生諧振,怎么處理?

PDN 元件對阻抗的影響

評論