來自RISC-V歐洲峰會的新創新準備簡化開源處理器的設計過程。

隨著RISC-V歐洲峰會的結束,我們將回顧本周的公司如何利用這次活動作為平臺,展示他們利用開放指令集架構(ISA)的最新創新。這些發展既包括硬件也包括軟件,這使得它們對許多領域的設計師都很重要。

自2015年發布以來,RISC-V一直是一個開放的標準,支持自定義硬件和軟件創新。ISA使用預先存在的知識來加快開發時間,并在設計過程中提供改進的靈活性。

RISC-V歐洲峰會的三個亮點可能為不需要在架構的最低級別操作的設計人員提供新的抽象級別。本文將介紹峰會上的這些公告,并討論每個創新如何為設計師提供工具,使開發周期更簡單,同時縮短上市時間。此外,我們將研究不斷發展的RISC-V生態系統,以評估ISA將如何繼續發展。

自定義矢量核

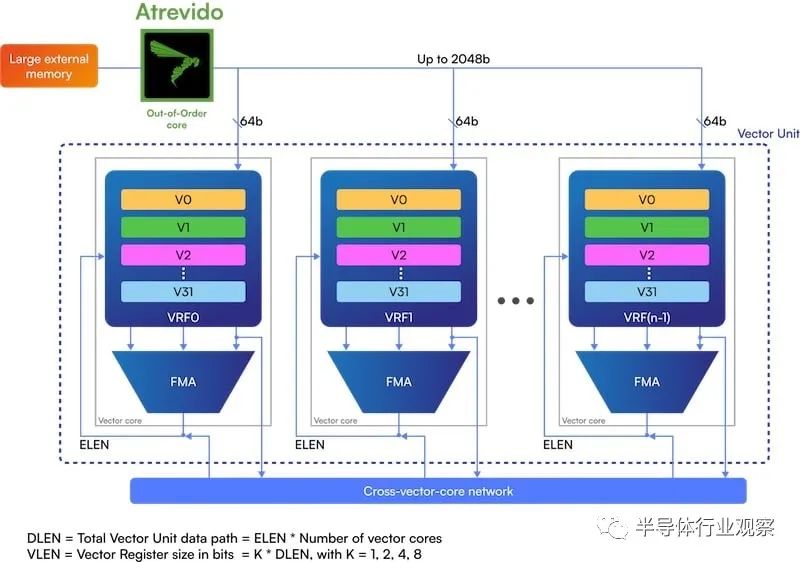

為了迎接RISC-V歐洲峰會,semidynamics宣布了“最大的、完全可定制的”矢量處理RISC-V處理器。隨著矢量計算在人工智能或計算機視覺應用中變得越來越重要,硬件矢量支持可以成為許多開發人員在高性能系統上工作的寶貴設計工具。隨著RISC-V國際公司2021年的矢量擴展,預計ISA的矢量處理將隨著需求而增長。

來自semidynamics的矢量單元是可定制的,以適應應用程序的需求,允許設計人員根據需要縮放數據路徑長度,矢量長度或數字格式。并且在單個單元中集成了從4到32個矢量內核,即使是計算最密集的應用程序也可以使用vector unit。矢量單元與atrevideo和Avispado RISC-V內核一起提供,并展示了RISC-V ISA的多功能性。

RISC-V矢量加密

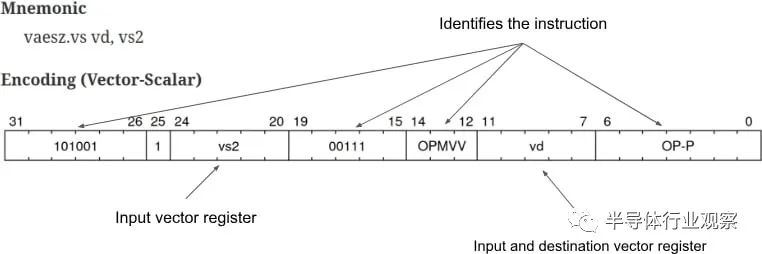

隨著矢量硬件可用性的提高,Codethink已經將對RISC-V矢量加密擴展集的全面支持集成到仿真軟件QEMU中。雖然仿真可能不是實現矢量加密設計的直接要求,但它是RISC-V規范中批準的要求。

基于他們過去在RISC-V設備上的經驗,Codethink在QEMU模擬器上的開發最終將使矢量加密技術更接近RISC-V標準化。目前,擴展集處于穩定階段,預計會發生有限的更改,之后擴展集可以凍結和/或批準。

軟件定義的硅

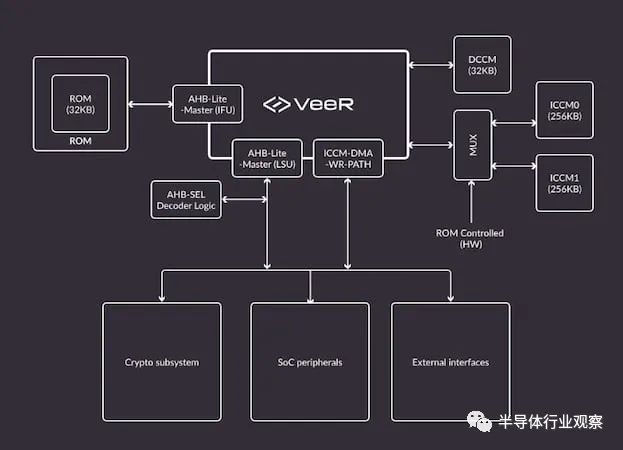

一組芯片聯盟成員,包括安特微和谷歌,提出了改進的數字設計工具,用于集成使用RISC-V內核。這些工具,即Verible和Kythe,可以與非常高效和優雅的RISC-V (VeeR)核心家族一起使用,以簡化設計過程,并允許在組織內部和組織間的工作中進行開放協作。

Caliptra項目突出了這些努力,該項目利用VeeR核心家族提供現代處理器所需的安全性。除了設計和驗證工具之外,Antmicro還提供了一個視覺系統設計器,提供了更多的理由相信RISC-V設計器很快就會體驗到一個新的抽象層次。

高性能RISC-V

雖然RISC-V歐洲峰會肯定會討論更多的發展,但本文中的發展代表了RISC-V處理器增加可訪問性和市場份額的趨勢。這并不是說模擬和數字芯片設計師很快就會過時,而是說設計RISC-V處理器可能很快就會成為一項更容易的任務。

隨著軟件和硬件的創新,如視覺系統設計,矢量核心支持,或專用的RISC-V模擬IP,高級開發和集成的新機會似乎即將到來。除了進入RISC-V生態系統的門檻較低之外,這最終支持了RISC-V不可避免的說法。

-

處理器

+關注

關注

68文章

19293瀏覽量

229914 -

指令集

+關注

關注

0文章

226瀏覽量

23384 -

RISC-V

+關注

關注

45文章

2283瀏覽量

46177

原文標題:RISC-V,迎來新創新

文章出處:【微信號:Rocker-IC,微信公眾號:路科驗證】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

擁抱RISC-V的開發世界 兆易創新推GD32VF103系列RISC-V MCU

玄鐵RISC-V生態大會深圳召開,達摩院引領RISC-V創新應用

2024 RISC-V 中國峰會:華秋電子助力RISC-V生態!

RISC-V Summit China 2024 | 青稞RISC-V+接口PHY,賦能RISC-V高效落地

RISC-V,即將進入應用的爆發期

為什么選擇RISC-V?

【RISC-V專題】芯昇科技RISC-V生態開發板首發試用

RISC-V簡介

RISC-V芯粒,終于來了

RISC-V競賽|2024年iCAN大學生創新創業大賽“算能杯”報名正式啟動!

RISC-V Summit China 2024 青稞RISC-V+接口PHY,賦能RISC-V高效落地

2024年RISC-V產品和應用創新案例征集活動公告

RISC-V,迎來新創新

RISC-V,迎來新創新

評論