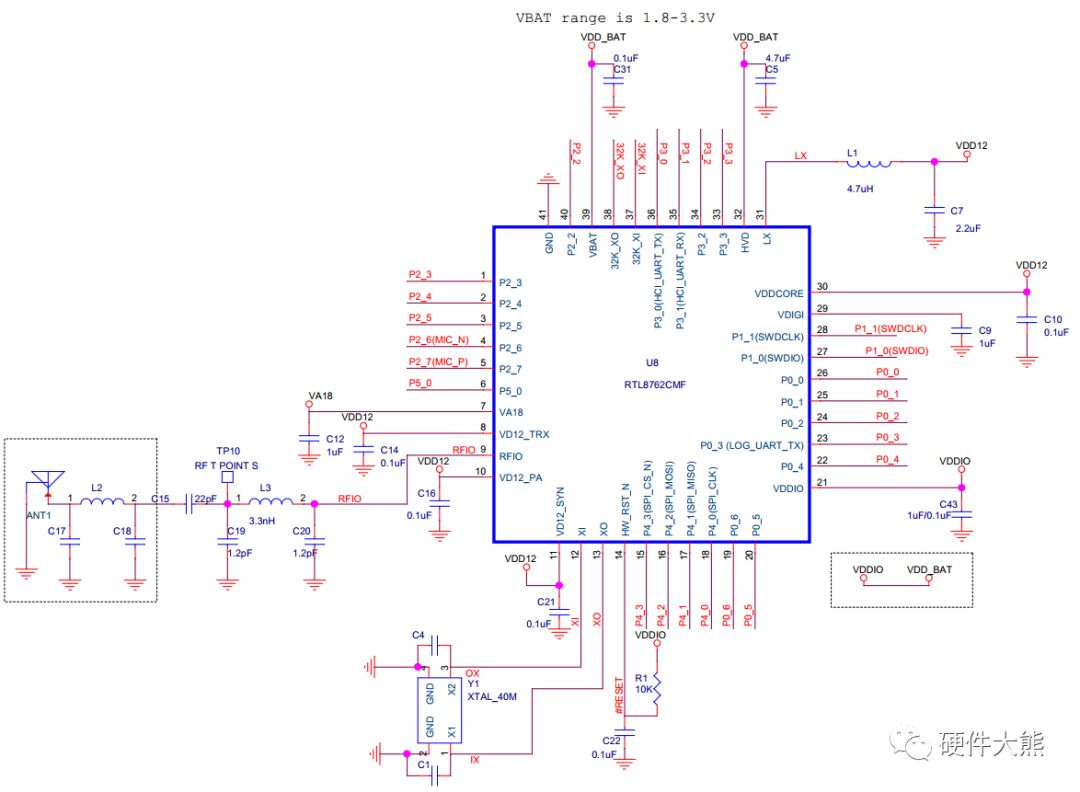

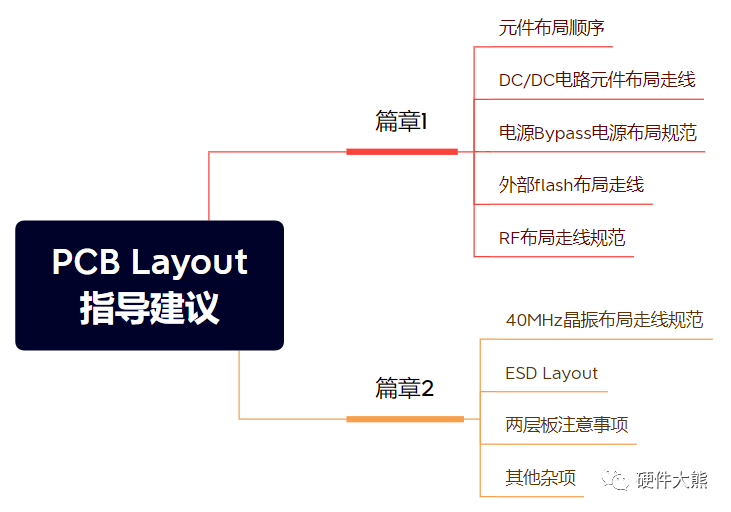

《一款射頻芯片的layout設(shè)計(jì)指導(dǎo)案例-篇章1》中,我們闡述了RTL8762元件布局順序、DC/DC電路元件布局走線、電源Bypass布局規(guī)范、外部flash布局走線、RF布局走線,

本篇闡述晶振、ESD、板層等相關(guān)指導(dǎo)建議——

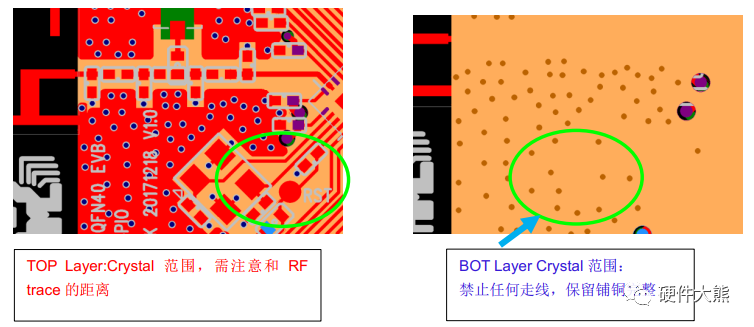

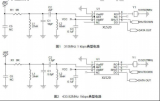

40MHz晶振布局走線規(guī)范

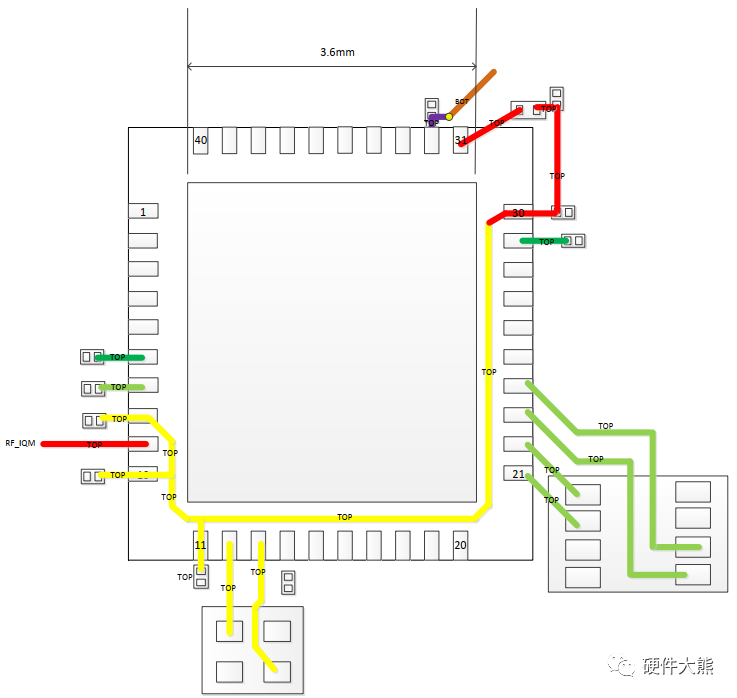

在沒(méi)有結(jié)構(gòu)限制情況下, Crystal 和 BT CHIP 要放在同一層面。

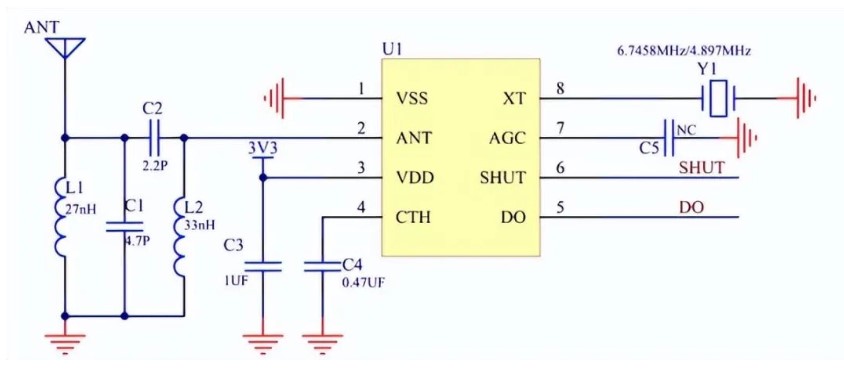

為了避免干擾 RF 信號(hào), Crystal 盡量遠(yuǎn)離 RF Trace。

Crystal 的放置應(yīng)盡可能靠近 BT CHIP,路徑要短, Trace 寬度建議超過(guò) 6mil。

如果是 2 層板,禁止在 Crystal 的背層走線,讓背層(BOT)的鋪銅保留完整性。

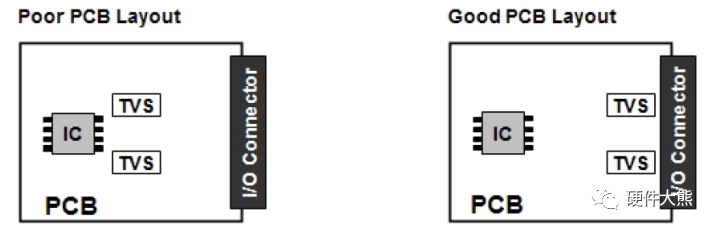

ESDLayout

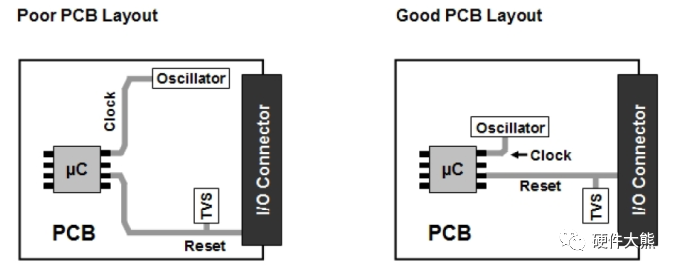

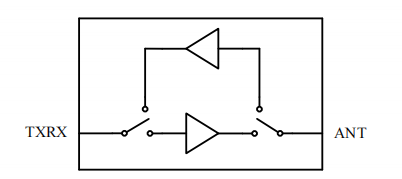

TVS 擺放位置應(yīng)盡可能靠近 ESD 源頭(接頭等處),與被保護(hù) IC 的距離要遠(yuǎn)于 ESD 源。布線時(shí)需將 ESD 源直接接到 TVS,減少 TVS 管和回流地之間的寄生電感

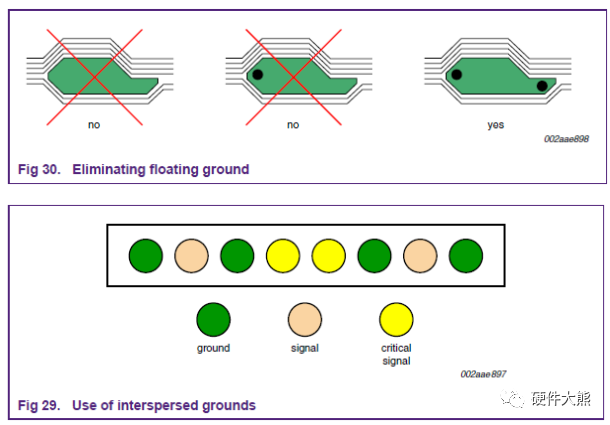

分割地平面時(shí)要注意縮短信號(hào)線的回流路徑, 采用星狀線的方式實(shí)現(xiàn)并聯(lián)接地。

刪除孤島銅皮,用地將敏感信號(hào)包裹起來(lái),防止其他信號(hào)的輻射干擾

盡量縮短線長(zhǎng)以減少寄生電感。因直角走線會(huì)產(chǎn)生更大的電磁輻射,避免直角走線連接到器件或走線上。高速電路設(shè)計(jì)時(shí),更需注意這點(diǎn)。

盡量增大過(guò)孔的鉆孔直徑和焊盤(pán)直徑,減少過(guò)孔的寄生電感。

布線時(shí),讓敏感信號(hào)線遠(yuǎn)離 PCB 板邊。為避免走線與天線間的串?dāng)_,走線需遠(yuǎn)離天線,天線需放在離

接頭較遠(yuǎn)的位置。布局時(shí),將所有的接頭和板邊接線放在 PCB 板邊一側(cè), ESD 敏感器件放到 PCB 中心。

兩層板注意事項(xiàng)

BT CHIP、 RF、 Crystal、 Buck 區(qū)域,盡量避免于這些區(qū)域走線。

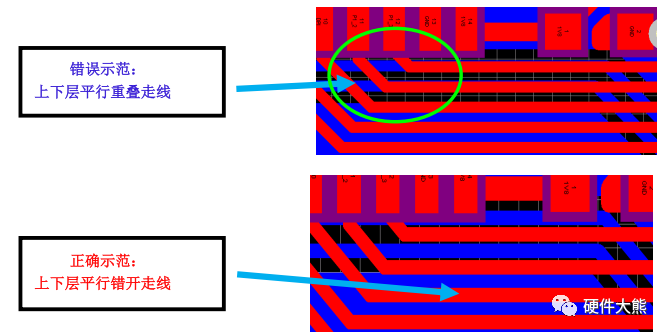

兩層板走線盡可能走在同一層面。

若走線要貫穿到背層,背面的走線盡可能短或者集中在一起,維持背面敷銅的完整。

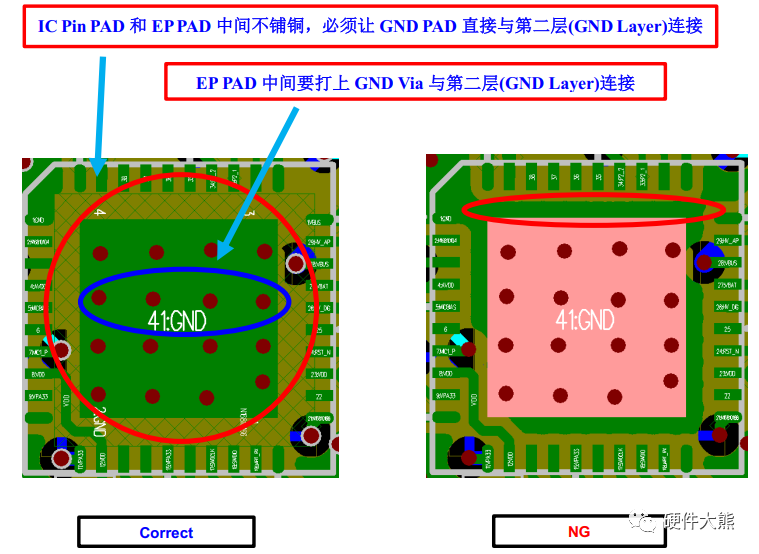

電源VDD12 走線可將 EPAD 尺寸改小到 3.6mm, trace 從 IC package 縫隙中穿過(guò)。

其他注意事項(xiàng)

上下層走線時(shí)盡可能不要平行重疊的走線

External flash 必須盡量的靠近 IC 擺放

-

ESD

+關(guān)注

關(guān)注

49文章

2036瀏覽量

173029 -

RF

+關(guān)注

關(guān)注

65文章

3055瀏覽量

167051 -

Layout

+關(guān)注

關(guān)注

14文章

405瀏覽量

61793 -

布局

+關(guān)注

關(guān)注

5文章

269瀏覽量

25017 -

射頻芯片

+關(guān)注

關(guān)注

976文章

413瀏覽量

79631

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

請(qǐng)推薦一款芯片

我想選一款能實(shí)現(xiàn)TMS320F2812的ARM芯片,求大神指導(dǎo)~

求一款帶有模擬輸出的射頻芯片

請(qǐng)問(wèn)有沒(méi)有一款參考頻率本身在10MHz的射頻卡

請(qǐng)大家給推薦一款集成整個(gè)接收通道的芯片

開(kāi)發(fā)一款射頻SOC藍(lán)牙芯片

介紹一款低功耗的單片ASK/OOK射頻接收芯片XL700

一款射頻芯片的layout設(shè)計(jì)指導(dǎo)案例

AT2401C是一款2.4GHz Zigbee 射頻前端芯片 功率放大器(PA) 智能家居工業(yè)自動(dòng)化

一款射頻芯片的layout設(shè)計(jì)指導(dǎo)案例

一款射頻芯片的layout設(shè)計(jì)指導(dǎo)案例

評(píng)論