今天,最先進的大算力芯片研發,正展現出一種拼搭積木式的“角逐”。誰的“拆解”和“拼搭”方案技高一籌,誰就更有機會在市場上贏得一席之地。隨著chiplet概念的不斷發酵,chiplet架構和異構計算也逐漸從頭部大廠偶爾為之的驚鴻一現,演變為高性能芯片的新常態。

與此同時,一場席卷全球的AIGC競賽,加劇了高性能芯片的需求。面對昂貴且一票難求的高性能賽道,新入局者不得不尋求更經濟和更快速的方式,從而反哺了chiplet生態。

接口:Chiplet互聯密鑰

在高性能計算和人工智能應用中,由于SoC的尺寸已接近reticle size,設計者被迫將SoC分割成更小的芯片,并將其封裝在一起。這些分解的die需要超短距離及高數據速率的die間互連。除了帶寬,die與die之間的連接必須確保可靠,并具有極低的延遲和功率效率。

Die-to-Die接口定義

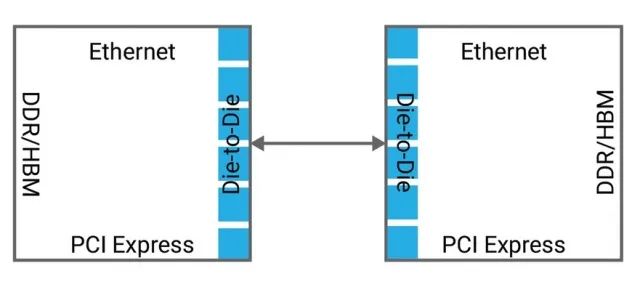

Die-to-die接口是在同一個封裝內的兩個die之間提供數據接口的功能模塊,它提供了一種可靠、高帶寬的芯片間互連方式,使不同的dielet可以在系統級別上進行連接和協同工作。為了實現功效和高帶寬,它們利用了連接裸片的極短通道的特征。?

Die-to-die接口通常由一個PHY和一個控制器模塊組成,在兩個die的內部結構之間建立可靠的數據連接。倘若沒有die-to-die接口,die之間的通信會變得十分困難。

Example of a high-performance computing and server SoC requiring die-to-die connectivity(source:eetimes)

Chiplet架構的前世今生

Die-to-die接口作為一種互聯技術,是為支持chiplet設計而誕生的。其背后的chiplet架構為應用需求驅動,經歷了三個時期的發展迭代。????

同構拆分:首先,是成本的迭代。大型SoC被拆分為多個相同設計的同質die,單獨流片,從而提高制造效率并降低成本。典型案例:AMD Zen/Zen+,在性能不變的情況下實現了40%的成本降幅。

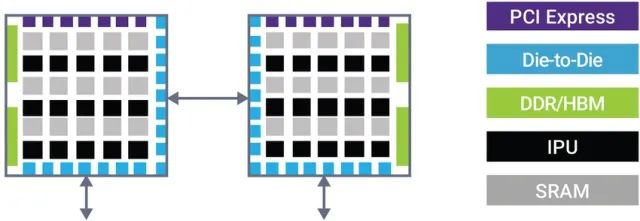

同構擴展:而后,是性能的提升。通過把更多的功能單元拼接在一起,進行橫向擴展,從而實現更高的計算能力和內存容量;這對于處理大規模的神經網絡和海量數據的AI訓練任務非常有益。

Example of an AI SoC requiring die-to-die connectivity(source:eetimes)

一個典型代表是Tesla DoJo,在Dojo芯片系統中,D1芯片是Dojo系統的基本算力單元(chiplet),每個Dojo則包含了25個D1及40個專用的IO芯片,使用TSMC的system-on-wafer技術集成到一起,實現超大算力支持。

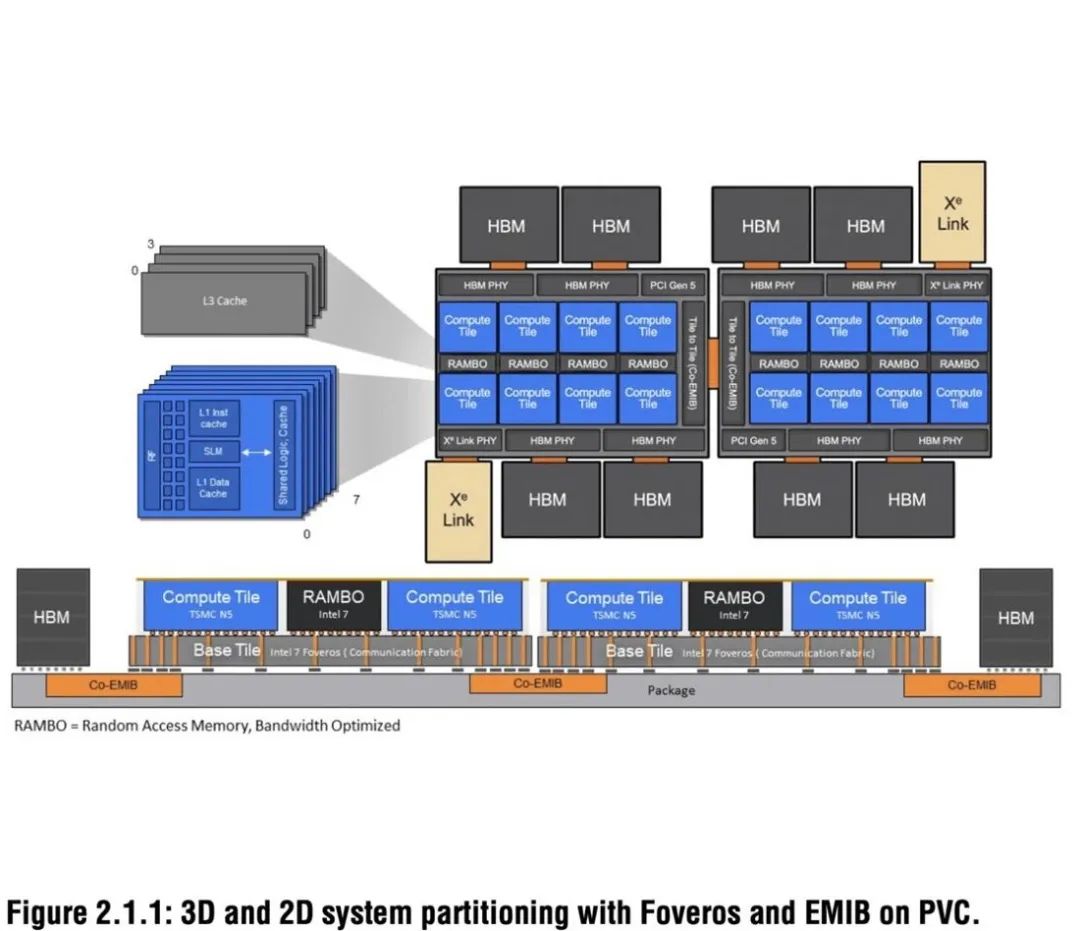

模塊化異構組合:隨著chiplet發展到3D架構,chiplet 逐漸演變模塊化單元,并分化為功能die和互連die兩種單元類型。常見的功能die如CPU、GPU、Senser、Wireless、光電等模塊,專注于不同的任務和功能的實現;互連die則通常包含一些關鍵的硬件組件,以實現功能die之間的高速數據傳輸和通信。通過組合不同功能的芯片模塊,有助于芯片更靈活、更容易地實現擴展和定制。

典型案例如Intel的Ponte Vecchio。由于使用chiplet設計,Intel得以在良率可控的情況下加入了大量的Xe核和海量緩存:包括128個Xe核,64MB的register file,64MB的L1 cache和408MB的L2 cache,共63顆chiplet(47個功能單元)。Ponte Vecchio系統可以實現839 TFLOPS的峰值浮點數算力以及1678 TOPS的峰值整數算力。?

從Intel Lakefield/Ponte Vecchio到AMD MI300再到Nvidia的GRACE+HOPPER,在實現如此高算力的超大規模芯片系統中,chiplet模塊化技術可謂居功至偉。與此同時,模塊化架構也催生了互聯設計方式的變革。????

高速互連芯粒IO Die

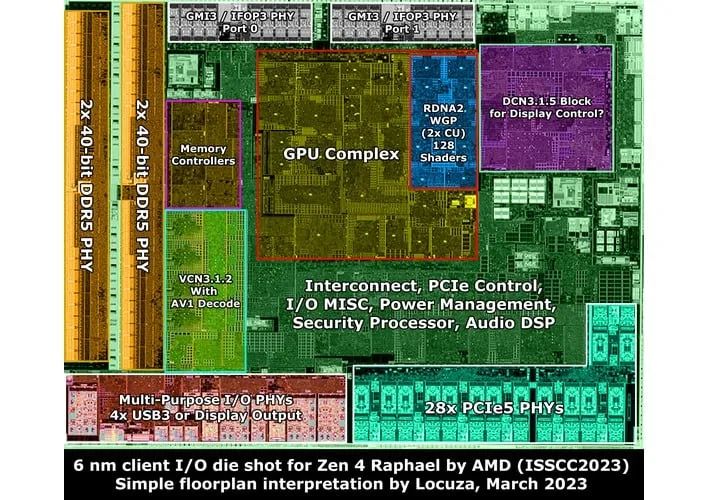

高速互聯芯粒IO Die,是一種獨立于CPU核心芯片的dielet。IO Die中通常包含各種負責互連的功能模塊,負責進行其他功能單元的互連。在AMD的Zen 2架構中,首次采用了分離的IO Die設計,這是Chiplet架構中的一大里程碑事件。

AMD實現chiplet設計的方式是將CPU與IO單元分離,分別稱為CCD(Core Chiplet Die)、IOD(IO die)。在一代Zen架構中,每顆CCD都包含IO部分,1-4組CCD單元實現了8-32核的并行,通過 IFOP(Infinity Fabric on Package)互連技術相連;Zen 2架構中,IO核心被剝離了出來,用IODie連接所有CPU core。CCD中包括CPU核心、緩存,后者包括各類控制器和輸入輸出。IO die在AMD的Zen系列里一直沿用至今。

AMD's Zen 4 IO die shot isolated by Li Jae-Yeon.

總的來說,IO die設計可以提高系統的性能、可靠性和可擴展性,且可以降低制造成本和電源消耗。此外,IOdie可以選擇最適合的工藝節點,不必緊跟CPU Core采用最先進的工藝節點,可以每兩三代處理器更新的時候再做一次大的迭代。

作為IOdie技術的開拓者,AMD采用IODie分離互連單元,打造高性能服務器芯片的策略,已經形成了正向的反饋。雖然在chiplet誕生初期,IOdie主要由AMD等大廠根據自身產品需求自行研發,但隨著CPU、GPU和其他高性能芯片領域廠商的崛起,加大了對通用IOdie的需求。應市場需求,國內也出現了一些技術能力強、業務快速增長的第三方通用IO die供應商,如奇異摩爾。

奇異摩爾的IODie方案主要面向高端服務器、自動駕駛、DPU、Edge AI、5G等高性能場景。通過在IODie中集成超高速D2D接口,全集成高速接口以及超高速互聯網絡等模塊,產品適用于計算密集的場景,并支持多場景設計復用,能助力高性能計算客戶實現產品性能的成倍提升,研發成本和量產時間的下降。

高性能互連底座Base Die

隨著超高規模和異構計算的快速發展,3DIC正成為一股重要的技術方向。在3D Chiplet架構中,互連芯粒IO die逐漸演成變為3DIC的高性能互聯底座 “Base die”。

Base die較IO die面積更大,除了IO die中的互聯模塊,還可以把原本集成在SoC中的Power、SRAM、I/O等非數字功能模塊拆分并拼搭進去,從而構成一個高度集成并節能的多核異構計算架構,同時實現上層的邏輯芯片面積最大化和芯片單位面積的最小化。

在互聯方面,Base die支持水平方向和垂直方向的異構芯片互連。垂直方向,通過TSV、microbump等3D互連技術與頂層邏輯芯粒、substrate垂直通信,從而以最小限度實現die與die之間的互連、片外連接,顯著提高芯粒集成密度。Base die適用于數據中心CPU/GPU/AI,智能汽車等工作負載居高不下的領域。

以Intel lakefield為例,設計為3D立體模塊化堆疊,由 3 層 die 組成。其中,底層的Base die 以Intel 22節點制造,主要包含各種協議的 IO 功 能,如USB,PCIe等,將中間層基于10nm制造的computing die(計算單元、圖形單元和顯示單元)堆疊在其上,并通過High current TSVs 與上層的功能單元互連。通過這種設計,Lakefield得以把更多的面積留給computing die,最終實現了10倍的SoC功率提升,2倍的圖形性能提升和2倍PCB面積下降。同類Base die設計還有AMD的旗艦級芯片MI300等。

AMD Instinct MI300 HPC accelerator. (Image Source: AMD)

隨著高性能芯片需求的增長,Base die市場不斷擴張,國內也崛起了一些相關的產品研發企業,如奇異摩爾,國內首批專注于chiplet的研發企業,面向數據中心、自動駕駛、下一代個人計算平臺等高性能算力場景提供3D chiplet架構的IO Die 和 Base die 解決方案。致力于以數據存儲和傳輸為中心,通過互聯芯粒連接和調度不同類型計算單元,成為大規模分布式異構計算平臺的基石。

行業生態格局轉變

Chiplet 生態發展至今,我們看到了它作為一種全新的技術,從內部自研到開放的發展過程:

內部自研:

Chiplet技術發展早期,如AMD等大型芯片制造商開始試水chiplet,但往往局限于企業內部獨立研發和應用,且僅應用于一些高端產品,如服務器和高性能計算等,組裝和測試等方面仍存在技術瓶頸。

半開放期:

目前,隨著chiplet技術的不斷成熟和商業化的推廣,越來越多的芯片廠商、設計公司和封裝測試廠商開始關注和使用chiplet技術。Chiplet應用范圍日益擴大,如各類處理器、加速器、芯片組和存儲器,從高性能服務器直至小型化電子產品;組裝和測試技術也得到了進一步的改進和完善;此外,市場上關于chiplet技術相關的產品和服務不斷涌現,chiplet作為一種芯片技術,其商業化應用趨勢也促進了整個芯片生態系統的升級和發展。

全面開放:

隨著chiplet技術的發展,未來會出現越來越多的產業鏈公司,專注于chiplet產業鏈各環節,即由chiplet系統級設計、EDA/IP、芯粒(核心、非核心、IO Die、Base Die)、制造、封測組成的完整chiplet生態鏈。

在我國,目前具備3D異構芯片整體能力的芯片廠商極少,大多數芯片廠商還是依賴IP廠商提供并行物理層或者串行物理層IP,Fab廠商提供先進封裝能力,一個完整的、面向 chiplet芯片的社會分工體系亟待形成。

作為國內第一批專注于2.5D-3D Chiplet服務的公司,奇異摩爾集合了一個全球大廠具有chiplet量產經驗的核心團隊,在Base die和IO Die方面具有先發優勢。奇異摩爾擁有多項芯片互聯關鍵基礎技術,包括高性能互連底座Base die、高速互聯芯粒IO die等,這些技術作為高密度、低延遲互連實現的關鍵,在chiplet系統運行方面起著關鍵作用。

基于Chiplet架構、通用互連芯粒、設計工具,及海量第三方芯粒庫,奇異摩爾致力于打造全球領先的chiplet通用產品解決方案。客戶只需自研部分核心芯粒,復用其他通用單元進行設計組合,即可快速構建所需專屬高性能芯片,極大降低研發成本和設計周期。同時,經由Chiplet超高速互聯形成超大規模系統級芯片(M-SOC), 助力提升芯片性能和能效,共同突破摩爾定律邊界。

除Base die、IO die等芯粒產品之外,奇異摩爾還有更多的軟硬件產品和解決方案,如die-to-die 接口IP,chiplet軟件設計平臺等,全面覆蓋2.xD、2.5D到3D的chiplet架構,為客戶提供從chiplet組合方案設計、芯粒打樣封測到量產管理服務的全鏈路解決方案。

作為半導體領域最為熱門的技術路線,chiplet已被許多頭部公司納入實踐。但這場基于制程與生態圈的革命,絕非僅靠一兩家行業巨頭的努力就可以實現,它需要一個成熟生態體系的群策群力,全產業鏈每一個環節的深度參與、合作。在這個生態圈中,從前端的EDA、設計公司,代工廠、封裝企業,每一環的意義都非同尋常且不可替代。

-

神經網絡

+關注

關注

42文章

4773瀏覽量

100890 -

soc

+關注

關注

38文章

4178瀏覽量

218480 -

chiplet

+關注

關注

6文章

434瀏覽量

12606 -

奇異摩爾

+關注

關注

0文章

49瀏覽量

3444 -

先進封裝

+關注

關注

2文章

417瀏覽量

262 -

芯粒

+關注

關注

0文章

59瀏覽量

143

原文標題:Chiplet:堆疊制程,融合生態

文章出處:【微信號:奇異摩爾,微信公眾號:奇異摩爾】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

藍牙技術的前世今生

初探工業互聯網的前世今生

聊聊MSP和CMP的前世今生

MiniLED背光的前世今生

人工智能的前世今生

帶你探索吹風筒的前世今生【其利天下高速風筒方案開發】?

Chiplet架構的前世今生

Chiplet架構的前世今生

評論