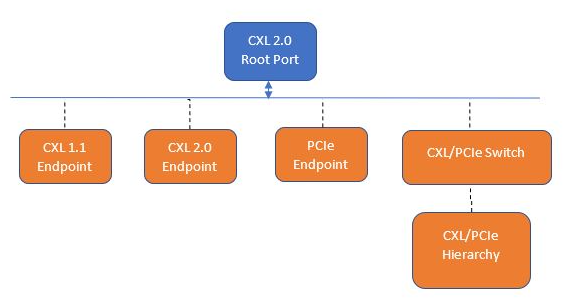

計算高速鏈路 (CXL) 是高帶寬設備互連技術的最新規范。它提供從 CPU 到高性能計算平臺其他組件的高速、高效連接。

CXL 在主機 CPU 和設備(如硬件加速器)之間具有相干內存訪問功能,通過利用 PCIe 架構的高級功能,滿足下一代設計中處理數據和計算密集型工作負載的要求。

讓我們探討一下 CXL 設備的類型和 CXL 特有的驗證挑戰,例如維護主機 CPU 和加速器之間的緩存一致性。有關此規范的初步概述。

類型 1 CXL 設備

實現完全一致的緩存,但沒有主機管理的設備內存

擴展 PCIe 協議功能(例如,原子操作)

可能需要實現自定義訂購模型

適用交易類型:D2H 相干和 H2D 窺探交易

類型 2 CXL 設備

實現可選的一致緩存和主機管理的設備內存

典型應用是連接了高帶寬存儲器的設備

適用的事務類型:所有 CXL.cache/mem 事務

類型 3 CXL 設備

僅具有主機管理的設備內存

典型應用是主機的內存擴展器

適用的交易類型:CXL.mem MemRd 和 MemWr 交易

CXL.cache/mem 設計必須保持主機和設備代理緩存及其相應內存之間的緩存一致性。類型 1 CXL 設備的基于偏差的一致性模型定義了設備附加存儲器的兩種狀態 – 主機偏置和器件偏置。每個國家都有自己的核查挑戰。

CXL 充當高性能 I/O 互連系統,試圖確保可靠、高效地訪問分布在各個組件中的內存。其中一些組件通過使用本地緩存來優化性能,并減少內存訪問的開銷。為了支持這種類型的配置,CXL.cache 協議可確保在內存或本地緩存中的組件之間保存的數據與每個組件保持一致。CXL 中的設備組件通常用作計算密集型應用程序的加速器,因此包含本地緩存。因此,如果主機組件想要訪問相同的內存位置,則可以強制設備從其本地緩存中逐出該行,并根據緩存行狀態更新相應的內存位置。

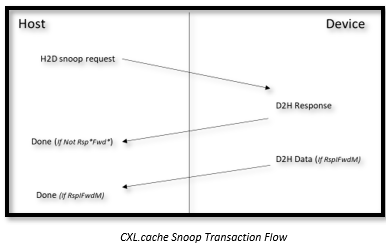

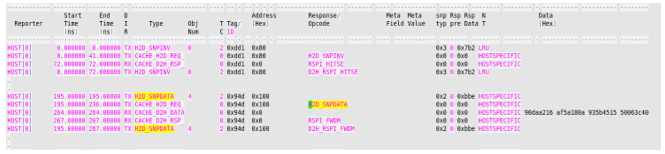

CXL.cache 協議將設備和主機之間的交互定義為多個請求,每個請求至少有一個關聯的響應消息,有時還具有數據傳輸。該接口由每個方向的三個通道組成:請求、響應和數據。通道以其方向命名 - D2H(設備到主機)和 H2D(主機到設備)。

基于 CXL 的系統使用基于偏差的一致性模型來提高內存訪問性能。當設備附加存儲器處于主機偏置狀態時,設備會像常規主機附加存儲器一樣訪問它。如果設備需要訪問設備附加的內存,它首先向主機發送請求,該請求將解析所請求行的一致性。

或者,當設備附加內存處于設備偏置狀態時,可以保證設備沒有緩存線路。在這種情況下,設備可以訪問它,而無需向主機發送任何事務。但是,無論偏置狀態如何,主機都會看到設備附加內存的統一視圖。

在主機偏置狀態和設備偏置狀態下,設備附加存儲器始終保持一致性。

CXL.cache H2D Snp 事務交換:

主機向設備發送 H2D 請求 SnpData

設備接收請求并將 D2H 響應作為RSPI_FWDM發送到主機。

設備將 D2H 數據發送到主機

主機收到響應后事務完成

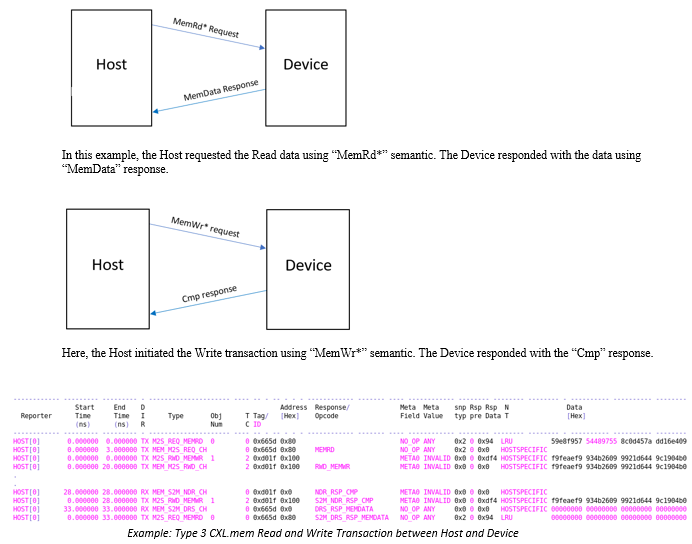

類型 3 設備主要是主機內存的內存擴展器。設備通過 CXL.mem 運行,以服務從主機發送的請求。類型 3 設備支持兩種類型的流 – 讀取和寫入流。

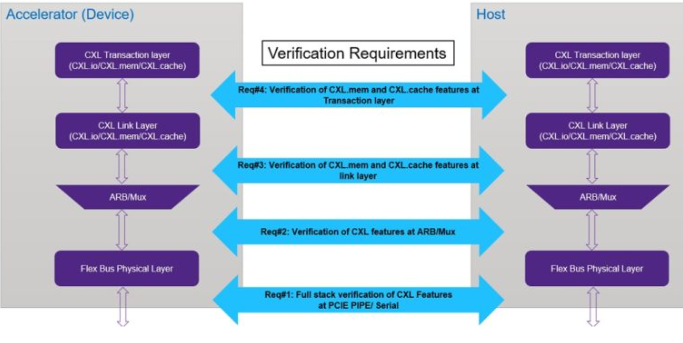

Synopsys 是 CXL 設計 IP 和驗證 IP 的市場領導者,為 CXL 生態系統的發展做出了重大貢獻。請繼續關注此新 CXL 規范的更深入探討,包括其他事務類型、分層體系結構以及 CXL 設計的驗證要求/挑戰等主題。

審核編輯:郭婷

-

cpu

+關注

關注

68文章

10870瀏覽量

211874 -

加速器

+關注

關注

2文章

799瀏覽量

37888 -

PCIe

+關注

關注

15文章

1239瀏覽量

82686

發布評論請先 登錄

相關推薦

一窺CXL協議

CXL事務層的結構是由哪些部分組成的

CXL內存協議介紹

一文詳解CXL鏈路層格式的定義

CXL事務層詳解

CXL.mem是什么?

CXL 2.0設備發現的迷人路徑

揭開CXL的神秘面紗:概述

瀾起科技MXC芯片成功通過CXL聯盟組織的CXL1.1合規測試

什么是CXL技術?CXL的三種模式、類型、應用

什么是CXL技術?CXL的三種模式、類型、應用

CXL設備類型簡介

CXL設備類型簡介

評論