什么是RISC-V?

精簡指令集計算機體系結(jié)構(gòu)(RISC)是一種指令集體系結(jié)構(gòu)(ISA),它意味著硬件和軟件之間的基本橋梁。RISC通過定義一組簡單的指令來實現(xiàn)匯編語言程序員和處理器之間的通信,這些指令組合在一起以執(zhí)行各種復(fù)雜的指令。

RISC和復(fù)雜指令集計算機(CISC)方法都試圖優(yōu)化CPU的處理時間。在RISC中,每條指令所需的周期減少,而每個程序的指令增加。但在CISC中,每個程序的指令數(shù)減少,而每條指令的周期增加。

執(zhí)行時間 = # 每個程序的指令數(shù) X # 每條指令的周期數(shù)

因此,RISC更像是基于軟件的ISA,因為軟件必須負(fù)責(zé)發(fā)送必要的簡單指令來執(zhí)行應(yīng)用程序。而CISC是基于硬件的ISA,因為CISC中的指令很復(fù)雜,因此需要復(fù)雜的指令解碼。

RISC-V是基于既定RISC原則的開放標(biāo)準(zhǔn)指令集架構(gòu)。與大多數(shù)其他ISA設(shè)計不同,RISC-V是在開源許可下提供的,允許在整個行業(yè)中廣泛使用。

了解TileLink在RISC-V架構(gòu)中的作用

RISC-V的開發(fā)人員開發(fā)了一種名為RocketChip的參數(shù)化SoC發(fā)生器,它使用TileLink規(guī)范作為其多處理器,加速器和DMA引擎等的互連。

TileLink 是一種開源芯片級互連標(biāo)準(zhǔn),提供對內(nèi)存和其他設(shè)備的一致內(nèi)存映射訪問。它也是一種快速且可擴展的互連,可提供低延遲和高吞吐量傳輸。

磁貼鏈接的主要優(yōu)點:

TileLink 旨在支持緩存一致性共享內(nèi)存

在多核(單個芯片上的多個處理器)環(huán)境中,緩存一致性是一個問題,其中每個處理器都有一個單獨的緩存內(nèi)存。在這種情況下,可以擁有共享數(shù)據(jù)的不同副本 - 即主存儲器中有一個副本,每個緩存內(nèi)存中有一個副本 - 并且當(dāng)其中一個數(shù)據(jù)副本被更改時,其他副本將留下無效數(shù)據(jù)而沒有更改通知。緩存一致性是用于確保通過系統(tǒng)更新共享數(shù)據(jù)值更改的概念。TileLink支持MESI等效協(xié)議來解決緩存一致性問題。

TileLink 為任何符合標(biāo)準(zhǔn)的 SoC 提供無死鎖

TileLink 支持可定義為有向無環(huán)圖 (DAG) 的任何拓?fù)洌渲写硎琼旤c,鏈路是邊,邊從驅(qū)動程序接口定向到接收器接口。通過支持 DAG,TileLink 在其拓?fù)渲袥]有任何循環(huán)或循環(huán)。

TileLink 配備了無序完成功能,以提高并發(fā)操作的吞吐量。

TileLink 提供無狀態(tài)總線寬度自適應(yīng)。

TileLink網(wǎng)絡(luò)如何工作?

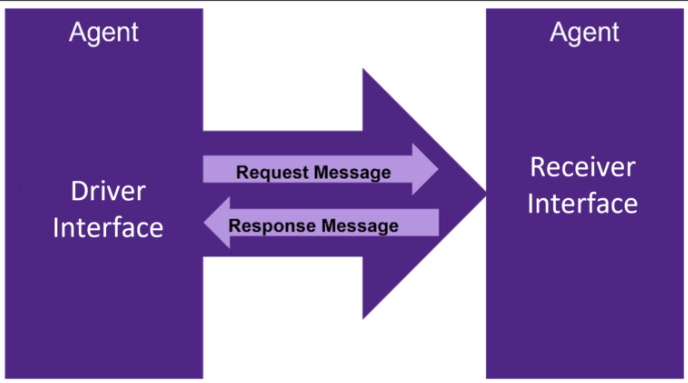

下圖顯示了基本 TileLink 網(wǎng)絡(luò)的示例。包含驅(qū)動程序接口的代理通過鏈路連接到包含接收方接口的另一個代理。驅(qū)動程序代理向接收代理發(fā)送請求,接收代理將響應(yīng)原始請求者,確認(rèn)已收到發(fā)送的數(shù)據(jù)或權(quán)限。

在每個鏈路中,Tilelink 定義了五個在邏輯上彼此獨立的通道,代理可以通過這些通道交換消息。TileLink規(guī)范按照“A << B << C << D << E”的順序定義了通道消息之間的優(yōu)先級,增加了優(yōu)先級,必須確保TileLink網(wǎng)絡(luò)中的消息永遠(yuǎn)不會進(jìn)入路由或保持和等待循環(huán),從而避免死鎖。

TileLink 中的消息由節(jié)拍組成,每個節(jié)拍包含以下內(nèi)容:

不變的郵件頭

不變的操作碼(消息類型)

不變大小(數(shù)據(jù)有效負(fù)載中字節(jié)數(shù)的以 2 為底的對數(shù))

可選的多拍數(shù)據(jù)有效負(fù)載

節(jié)拍由特定通道的獨立“就緒”和“有效”信號調(diào)節(jié)。發(fā)送方和接收方需要分別提供有效和就緒的信號才能實現(xiàn)位傳輸。一旦請求消息啟動,其相應(yīng)的響應(yīng)消息可能會在以下任何時間發(fā)送:

在預(yù)定義的延遲之后

在接受請求的第一個節(jié)拍的同一周期內(nèi)

在接受請求消息的所有節(jié)拍之前

TileLink禁止TileLink網(wǎng)絡(luò)中的超時,保證TileLink網(wǎng)絡(luò)永遠(yuǎn)不會死鎖。TileLink 協(xié)議定義了稱為轉(zhuǎn)發(fā)處理規(guī)則的規(guī)則,這些規(guī)則控制接收代理可以通過更改就緒信號來拒絕消息節(jié)拍的條件。

Synopsys VIP for TileLink

Synopsys? 驗證 IP for TileLink 提供了一套全面的協(xié)議、方法、驗證和生產(chǎn)力功能,使用戶能夠?qū)崿F(xiàn)加速驗證收斂。

Synopsys TileLink VIP 的功能包括:

支持 TileLink 1.8.0 和 1.8.1 規(guī)范

驅(qū)動器、接收器和交叉桿代理

TL-UL、TL-UH 和 TL-C 一致性級別

所有渠道

所有請求和響應(yīng)消息

全面的同通道和跨通道延遲

數(shù)據(jù)寬度:32、64、128、256、512、1024 位

所有突發(fā)大小高達(dá) 4KB

無序響應(yīng)

用戶定義的先進(jìn)先出模式(按順序)響應(yīng)

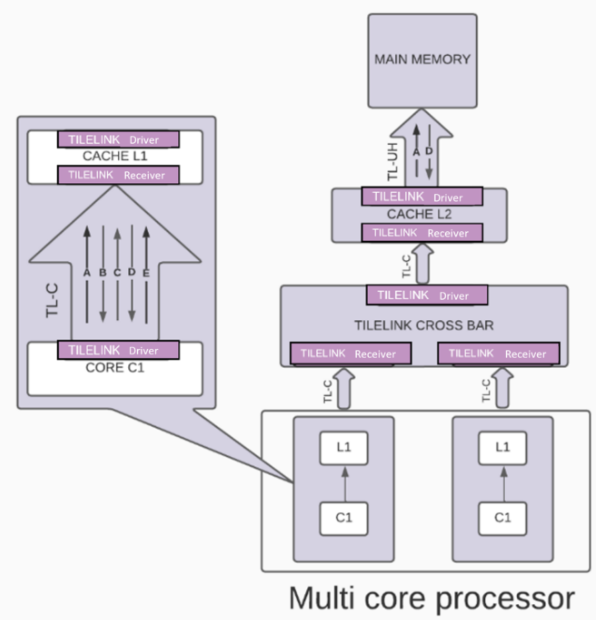

下圖顯示了可在多級高速緩存應(yīng)用程序中使用 Synopsys 驗證 IP for TileLink 的基本架構(gòu)示例。通過TileLink驅(qū)動程序或接收器接口連接到TileLink互連的每個組件(內(nèi)核,緩存L1,緩存L2,主存儲器)都可以與其相應(yīng)的驅(qū)動程序或接收器驗證IP代理集成。

如圖所示,當(dāng)具有獨立緩存的多個內(nèi)核共享主內(nèi)存或更高級別的緩存時,可以使用 TileLink 交叉條代理來維護(hù)它們之間的緩存一致性。

總結(jié)

盡管RISC-V不是第一次嘗試免費和開源處理器IP,但它是第一個大規(guī)模地引起業(yè)界興趣的嘗試。這為TileLink規(guī)范提供了靈活性和開放的方法,產(chǎn)生了巨大的創(chuàng)新和增長潛力。

Synopsys VIP for TileLink 可以毫不費力地集成、配置和定制。

Synopsys VIP 與 Synopsys Verdi Protocol Analyzer 調(diào)試解決方案以及 Synopsys Verdi?? Performance Analyzer 原生集成。在 SoC 上運行系統(tǒng)級有效負(fù)載需要更快的基于硬件的預(yù)硅解決方案。基于 Synopsys IP 的 Synopsys 事務(wù)處理器、內(nèi)存模型、混合和虛擬解決方案可在業(yè)界最快的驗證硬件 Synopsys ZeBu? 和 Synopsys HAPS? 系統(tǒng)上實現(xiàn)各種驗證和確認(rèn)用例。

審核編輯:郭婷

-

處理器

+關(guān)注

關(guān)注

68文章

19349瀏覽量

230314 -

ISA

+關(guān)注

關(guān)注

0文章

55瀏覽量

43760 -

RISC

+關(guān)注

關(guān)注

6文章

463瀏覽量

83775

發(fā)布評論請先 登錄

相關(guān)推薦

《RISC-V能否復(fù)制Linux 的成功?》

RISC-V最重要的意義所在

學(xué)習(xí)RISC-V入門 基于RISC-V架構(gòu)的開源處理器及SoC研究

可擴展的高性能RISC-V 內(nèi)核IP

RISC-V應(yīng)用領(lǐng)域的拓展

Microchip FPGA 和基于 SoC 的 RISC-V 生態(tài)系統(tǒng)簡介

RISC-V SoC 新開源平臺發(fā)布 zqh_riscv

布局 RISC-V 領(lǐng)域,中國聯(lián)通加入中國 RISC-V 產(chǎn)業(yè)聯(lián)盟

RISC-V,正在擺脫低端

RISC-V有什么軟件生態(tài),RISC-V IP在芯片中的應(yīng)用

基于形式的高效 RISC-V 處理器驗證方法

如何保證RISC-V驗證設(shè)計完整性

晶心科技與Arteris合作加速RISC-V的SoC設(shè)計創(chuàng)新

Arteris與晶心科技攜手推進(jìn)RISC-V SoC設(shè)計創(chuàng)新

晶心科技與Arteris攜手加速RISC-V SoC的采用

用于RISC-V SoC的TileLink互連驗證IP

用于RISC-V SoC的TileLink互連驗證IP

評論