本文分別對quartus和vivado防止信號被優化的方法進行介紹。

為什么要防止信號被優化

在FPGA開發調試階段,經常遇到這樣的情況,需要臨時添加信號,觀察信號變化,用來定位代碼中存在的問題,很多時候這些臨時添加的信號會被綜合工具優化掉,為了防止這種情況的發生,可以使用添加虛擬引腳(quartus)和代碼中添加屬性(vivado)。

下面分別對兩種方法進行說明,在原有代碼中加入如下代碼,觀察cnt信號是否被優化,能否通過邏輯分析儀進行觀測。

reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

Quartus中如何設置虛擬引腳

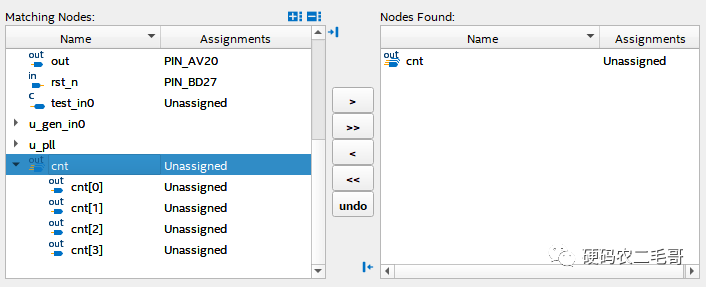

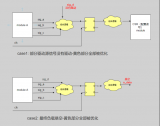

在quartus中加入上述代碼后,將cnt信號設置成輸出引腳。 下面將cnt信號設置為虛擬引腳。

方法1:

在qsf文件中添加如下內容:

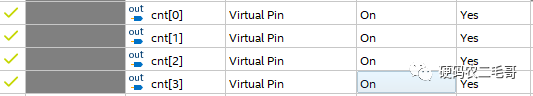

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[0]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[1]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[2]

set_instance_assignment -name VIRTUAL_PIN ON -to cnt[3]

編譯后,添加signal tap,cnt信號可以添加,說明沒有被優化。

方法2:

將cnt信號設置成輸出后,打開Assignment Editor,進行如下設置。

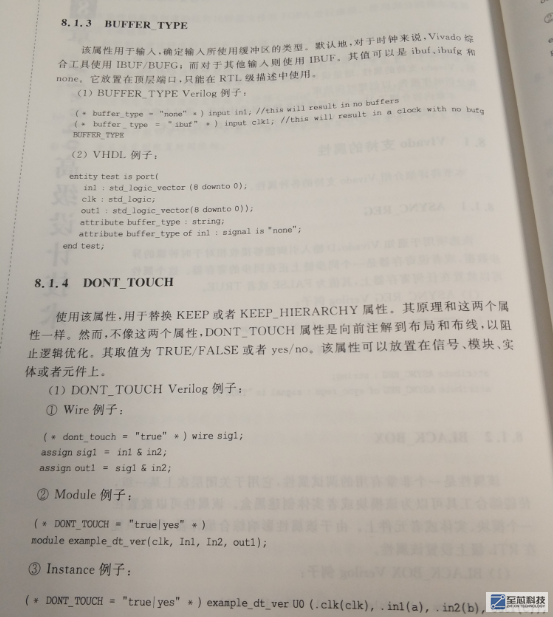

Vivado中防止信號被優化

在代碼中加入(* dont_touch = "true" *) 。

(* dont_touch = "true" *) reg [3:0] cnt;

always@(posedge clk,negedge locked)

begin

if(!locked)

cnt <= 4'd0;

else

cnt <= cnt + 1'b1;

end

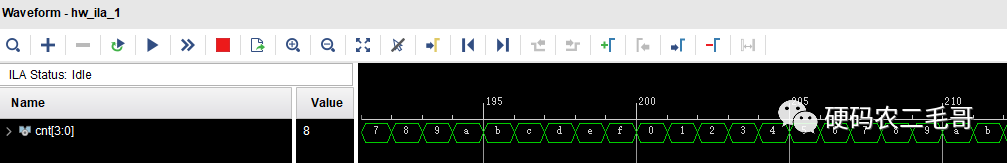

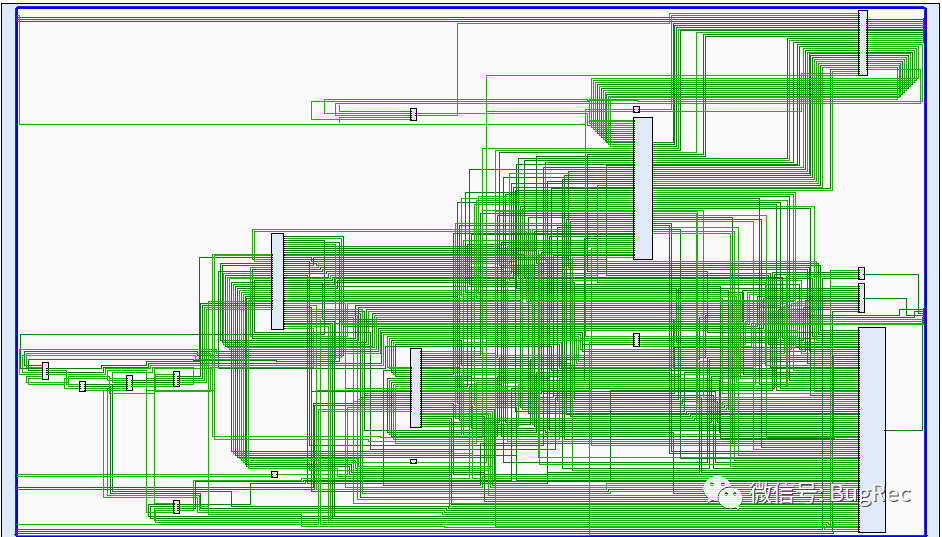

重新編譯后,使用ila觀測cnt,ila中有信號,證明信號沒有被優化。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602986 -

信號

+關注

關注

11文章

2789瀏覽量

76730 -

引腳

+關注

關注

16文章

1193瀏覽量

50411 -

quartus

+關注

關注

16文章

171瀏覽量

74622 -

Vivado

+關注

關注

19文章

812瀏覽量

66470

發布評論請先 登錄

相關推薦

FPGA中的I_O時序優化設計

FPGA中的I_O時序優化設計在數字系統的同步接口設計中, 可編程邏輯器件的輸入輸出往往需要和周圍新片對接,此時IPO接口的時序問題顯得尤為重要。介紹了幾種

發表于 08-12 11:57

今日說“法”:如何防止reg、wire型信號在使用邏輯分析儀時被優化

)對于reg型信號,為了防止Altera自帶綜合器將其優化掉,可以添加noprune屬性。這樣就可以防止某些寄存器信號

發表于 05-16 17:48

如何有效防止FPGA設計被克隆?

如何有效防止FPGA設計被克隆?

據估計,目前盛行的假冒電子產品已經占到整個市場份額的10%,這一數據得到了美國反灰色市場和反假冒聯盟(AGMA)的支持。AGMA是由惠普

發表于 01-04 15:32

?1402次閱讀

防止Wi-Fi信號被截獲的墻紙(英國開發)

防止Wi-Fi信號被截獲的墻紙(英國開發)

近日英國一家公司開發出了一種特殊的墻紙,可以有效的防止 Wi-Fi網絡信號

發表于 01-14 17:05

?1487次閱讀

FPGA信號處理算法設計、實現以及優化(南京)

利用FPGA實現信號處理算法是一個難度頗高的應用,不僅涉及到對信號處理算法、FPGA芯片和開發工具的學習,還意味著要改變傳統利用軟件在DSP上實現算法的習慣,從面向硬件實現的算法設計、

發表于 12-26 17:26

?12次下載

信號管腳任務可進行多個FPGA的I/O優化

信號銷任務之間可以自動優化PCB上的多個fpga同時尊重pin-specific規則和約束。減少路由層,減少跨界車和整體跟蹤PCB上的長度,并減少信號完整性問題較高的畢業率和更短的

PCB設計中的高速信號傳輸優化技巧

在現代電子設計中,高速信號的傳輸已成為不可避免的需求。高速信號傳輸的成功與否,直接影響整個電子系統的性能和穩定性。因此,PCB設計中的高速信號

FPGA在線調試信號被優化原因分析及防止優化方法總結

而我們常常會使用代碼中的信號名來抓取信號,后期布局布線階段,無法找到對應的電路信號,可能會導致無法抓取信號或者布局布線失敗。

發表于 06-20 10:32

?2202次閱讀

FPGA設計中如何防止信號被優化

FPGA設計中如何防止信號被優化

評論