半導體芯片一直在不斷發展,以滿足快速轉變的應用需求,因此測試技術也滿足這些芯片的測試目標。大約二十年前,應用受到限制,設計更簡單,因此對功耗、性能和面積 (PPA)、周轉時間、重復使用和上市時間等的關注很重要,但在當今競爭激烈的環境中并不像現在那么重要。帶有掃描鏈的結構測試足以滿足測試質量和成本目標,并且對設計的影響最小。應用空間的擴大推動了對芯片性能和功能提高的要求,使設計更大、更復雜。隨著半導體市場的發展和競爭的加劇,引入了功率門控、多核設計、片上系統 (SoC) 設計等新技術,以突出每一點性能、優化功耗并滿足緊迫的上市時間目標。同樣,為了控制測試成本,測試技術也取得了進步,例如測試壓縮編解碼器,大大減少了測試時間和數據量。將更大、更多內核集成到 SoC 的趨勢仍在繼續,導致測試邏輯和測試架構復雜性增加。物理感知DFT成為減輕測試結構的PPA影響的標準做法,分層方法使用靜態測試引腳復用的分階段測試成為首選測試策略。

現在,半導體設計正在經歷另一個轉折點,人工智能和自動駕駛等應用進一步推動了性能需求,需要采用3D-IC、基于小芯片的設計、具有數千個復制內核的大規模并行設計以及基于大型平鋪的架構等設計方法來滿足這些要求。這些下一代設計再次需要測試技術創新,Synopsys 正在引入突破性的流結構和順序壓縮技術,以滿足四個關鍵測試要求:

DFT 周轉時間短

最小化測試成本

高測試解決方案可擴展性

在芯片生命周期內進行高帶寬測試和測試重用

當前測試解決方案的挑戰

盡管現有的測試壓縮、靜態測試引腳復用和當前的流方法迄今為止為許多設計提供了令人滿意的測試結果,但由于即將推出的設計的重要測試需求,它們面臨著重大挑戰。對于較短的周轉時間,測試解決方案應提供簡化的DFT規劃和實施。靜態引腳復用通常需要芯片設計人員經歷一個耗時的迭代過程來估計編解碼器輸入-輸出引腳,將頂級引腳分配到內核并定義內核測試組,所有這些都在設計開發過程中完成,而無需完全了解其模式數量、功耗和測試時間。即使付出了很大的努力,這種方法也經常會導致固定的低效DFT,這使得管理測試功率具有挑戰性,并且由于無法在整個測試過程中最大限度地利用測試引腳而導致測試時間欠佳。固定的編解碼器分配在重用內核時也需要重新設計,從而進一步減慢周轉時間。當前的流解決方案解決了其中的幾個問題,但仍需要確定有效編解碼器配置的繁瑣過程,以減少測試量并保持流效率,這會增加開發時間和/或次優測試數據。需要能夠快速實施、快速生成碼型、最大限度地減少測試數據量和測試周期、同時保持測試質量的高級壓縮技術。

在 可 擴展 性 方面, 測試 解決 方案 的 物理 設計 應 隨著 高級 設計 擴展 和 集成 技術 的 采用, 而 應 輕松 擴展, 而 而 不會 影響 測試 成本 或 開發 進度。引腳復用技術導致進出編解碼器的長數據路徑在芯片級收斂,從而對路由和擁塞產生負面影響。在基于平鋪的基臺設計中,這種影響會進一步加劇,因為這些設計通常需要在具有此架構的每個內核中自定義邏輯和額外的布線。這給芯片設計人員在將設計從數百個內核擴展到數千個內核時提出了巨大的挑戰。

最后, 隨著 測試 擴展 到 硅 生命 周期 管理 (SLM) 以滿足 設備 可靠性 目標, 基于 高速 功能 I/ O (HSIO), 尤其是 PCIe 和 USB 的高 帶 寬 測試 趨勢 的 解決 了 測試 帶 寬 隨著 掃描 GPIO 的 減少 趨勢, 以及 將 測試 從 制造 到 系統 級 測試 (SLT) 到 現場 測試 簡化 的 需求。這是通過高速測試和在所有測試階段通過相同的HSIO重用測試模式來實現的。測試 解決 方案 必須 設計 能夠 利用 這種 能力, 并 在 芯片 生命周期 內 增強 測試 功能。雖然引腳復用架構可以由HSIO驅動,但其工作速度受到其復雜數據路徑和時序約束的限制,因此無法充分利用可用的高測試帶寬來縮短測試時間。現有的流式處理解決方案要么對使用功能性 HSIO 進行測試的支持有限,要么只能將此方法部署為使用非功能性 HSIO 的制造測試。

突破性的測試時間和測試數據縮減解決方案

Synopsys TestMAX DFT 的流結構功能具有順序壓縮解決方案,是一種可編程、可擴展的高速測試結構,具有先進的壓縮引擎,可解決靜態引腳復用架構和當前測試編解碼器和流技術的測試時間和 DFT 挑戰。它還 顯著 降低 了 硅 生命周期 測試 的 測試 成本 和 工作量, 并 完全 支持 通過 HSIO 進行 高 帶 寬 測試。

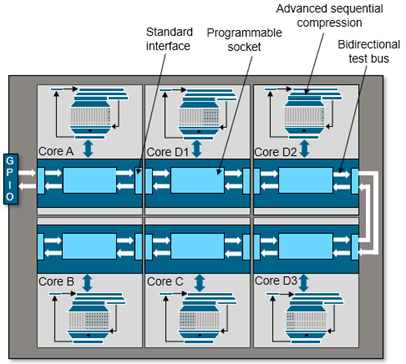

圖1:具有順序壓縮的 Synopsys 流結構。

順序壓縮使用基于種子的輸入、基于多輸入移位寄存器 (MISR) 的單位輸出和片上比較,提供簡單的編解碼器設計、快速的碼型生成和高測試體積壓縮,從而縮短測試時間和開發時間。如圖 1 所示,流結構具有統一的雙向測試總線,該總線穿過每個內核,并通過基于 IEEE 1687 設置的可編程邏輯(稱為套接字)與順序壓縮編解碼器接口。這些插座標準化了設計中所有內核的內核到測試總線接口,使設計人員能夠快速構建DFT,并避免開發過程中的迭代和困難的設計決策。插座可以在 DFT 和設計完成后根據編解碼器、內核分組及其測試時間和功率要求進行編程,從而使內核級 DFT 實現獨立于芯片級資源。這也允許在包含流結構的新設計中輕松重用內核,方法是插入內核并對內核的插槽進行編程,而無需任何頂級或內核級別的更改。流結構邏輯的這種可配置性極大地簡化了 DFT 實現并加快了周轉時間。

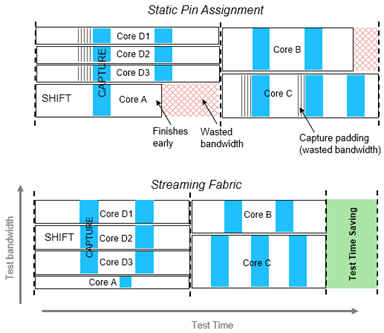

圖2:測試靜態引腳復用與流結構之間的帶寬分布比較。

流式結構通過有效地將高度壓縮的測試數據傳送到內核,進一步縮短了測試時間。它 根據 測試 數據 自動 確定 每 個 內核 的 測試 數據 帶 寬 要求, 并 配置 套 字 以 盡可能 最佳 地 將 測試 總 線 帶 線 帶 寬 分配 到 編 程, 從而 最大限度 提高 測試 引腳 利用率 并 最大限度 縮短 了 SoC 的 整體 測試 時間, 如 上圖 2 所示。

測試時間減少的另一個級別來自流結構的頻率縮放。GPIO 通常可以以比芯片掃描網絡更高的速度運行,并且流結構的架構還允許測試數據以比內核中的編解碼器和掃描網絡高得多的速度流動。借助 socket 的帶寬匹配功能,由幾個頂級引腳驅動的更快、更窄的流結構可以并行驅動多個較慢的較寬編解碼器,從而進一步縮短測試時間。然而, 對于 許多 設計, 流 解決 方案 的 測試 總 線 可能 運行 得 更快, 但 會 受到 GPIO 速度 的 限制, 這 導致 測試 總 線 帶 寬 未 得到 充分利用。當前的流技術建議使用許多 GPIO 來利用剩余帶寬,方法是通過自定義邏輯將許多較慢的 GPIO 轉換為較窄的較快的測試總線。對于由于需要大量片外數據訪問而見證了GPIO減少和芯片上HSIO增加的高級設計,這種方法是不可行的。

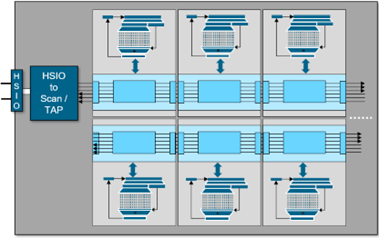

Synopsys 的流結構與 Synopsys 的高帶寬 HSIO 到掃描/TAP 測試解決方案無縫集成(如圖 3 所示),只需使用幾個 HSIO,就可以將測試數據以更高的速度傳送到更寬的流結構測試總線,并且與減少的 GPIO 相比,可以顯著縮短測試時間。與HSIO相比,測試的另一個優勢是,通過重用制造測試模式,它避免了為SLT和現場測試開發和維護單獨模式集的需要,在整個芯片生命周期中提供完整的測試解決方案,并加快了上市時間。

圖3:具有功能高速IO(HSIO)的高帶寬測試。很少有HSIO驅動寬流結構測試總線。

流結構的常規和統一架構允許為所有設計提供物理設計友好且可擴展的實施,包括 3D-IC、基于小芯片的設計、具有數千個復制內核的大規模并行設計以及基于相鄰瓦片的大型設計。核心邊界和流水線測試總線處的標準接口允許結構從一個內核到下一個內核,最終到達頂層引腳,以便為相鄰和非相鄰設計提供輕松的物理集成和時序收斂。流結構具有獨特的功能,可以在多個分層子分支上同時提供來自主測試總線的測試數據,這些子分支可以以不同的速度運行。此外, 設計人員 可以 根據 布局 中 每 個 核心 的 位置 實現 不同 寬度 的 子 分支, 以 在 物理 設計 和 減少 測試 時間 之間 實現 平衡。雖然 流 結構 可以 將 相同 的 測試 數據 廣播 到 芯片 上 任意 數量 的 相同 內核, 從而 大幅 縮短 測試 時間, 但 多 分支 架構 還 為 設計人員 提供 了 靈活 的 數據, 將 數據 廣播 到 具有 較小 分區 的 單個 分支 上 的 相同 內核, 或 同時 為 多個 設計 分區 提供服務 的 多個 分支 上 的 相同 內核, 以 優化 設計 的 PPA。由于3D-IC和基于小芯片的設計是單片設計的擴展,因此文章“大型SoC和AI架構的DFT實用方法,第二部分”詳細介紹了流結構如何完美擴展,以便為這些設計提供理想的測試數據傳輸機制。

現代應用正在推動設計擴展和集成方法的范式轉變,需要先進的測試技術來滿足這些設計的關鍵要求:較短的DFT周轉時間、最小化的測試成本、高測試解決方案可擴展性、高帶寬測試以及整個芯片生命周期的測試重用。Synopsys 的流結構具有順序壓縮和高帶寬 HSIO-to-Scan/TAP 測試技術,不僅為下一代設備提供了測試成本和周轉時間縮短,而且還提供了靈活、可擴展的結構架構,以使用 DFT 優化設計的 PPA 和整個芯片生命周期的完整解決方案。

審核編輯:郭婷

-

半導體

+關注

關注

334文章

27390瀏覽量

219033 -

人工智能

+關注

關注

1791文章

47314瀏覽量

238617 -

自動駕駛

+關注

關注

784文章

13826瀏覽量

166493

發布評論請先 登錄

相關推薦

下一代設計的測試數據流

下一代設計的測試數據流

評論