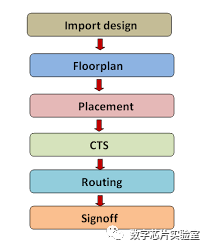

Physical design是將 電路描述(circuit description) 轉(zhuǎn)化成 物理版圖(physical layout) 的過程。在物理版圖中規(guī)定cell的擺放位置和相互之間的 連線 。

Import design: 物理設(shè)計(jì)流程的第一步就是**導(dǎo)入設(shè)計(jì)。**在綜合階段RTL被轉(zhuǎn)換成netlist,然后在物理設(shè)計(jì)階段被讀入物理設(shè)計(jì)工具中。

Floorplan: Floorplan階段定義了 芯片(die)的大小 , macro和io的位置 , power grid的定義和連接 。在擺放完macro的同時(shí),也定義了擺放std cell和routing的區(qū)域。

Placement: Placement是使用物理設(shè)計(jì)工具自動(dòng)擺放std cell的過程,其中在global placement階段,非常roughly地將std cell擺放在core里面,在detailed placement階段,將std cell legalize到siterow上 ,保證沒有overlap。

同時(shí)還需要通過GRC map來檢查congestion.

CTS(clock tree synthesis): 在CTS階段通過插入inverter和buffer來生成時(shí)鐘樹。因?yàn)閏lock信號(hào)對(duì)于基于DFF的ASIC設(shè)計(jì)非常重要,我們需要在CTS階段balance clock skew以及最小化insertion delay來滿足設(shè)計(jì)的時(shí)序(timing)和功耗(power)要求。

Routing: 在Routing階段之前,只有power進(jìn)行了實(shí)際的金屬連線,macro、std cell、clock和io都只是邏輯上定義了連接關(guān)系(logically)。在routing階段就需要用金屬線進(jìn)行物理上的連接(physical)。

**Signoff:**在routing階段完成以后,芯片的物理版圖已經(jīng)確定了。在sign-off階段需要保證芯片的質(zhì)量和性能滿足了要求,然后才能進(jìn)行 投片(tape-out) 。

-

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59934 -

STD

+關(guān)注

關(guān)注

0文章

36瀏覽量

14392 -

ASIC技術(shù)

+關(guān)注

關(guān)注

0文章

19瀏覽量

7605 -

dff

+關(guān)注

關(guān)注

0文章

26瀏覽量

3443

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

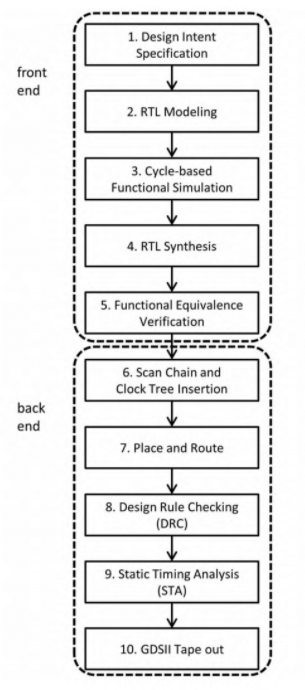

典型的基于RTL的ASIC設(shè)計(jì)流程分析

ASIC物理設(shè)計(jì)流程概述

ASIC物理設(shè)計(jì)流程概述

評(píng)論