三.CDM測試

目前針對CDM的測試規模主要有:ANSI/ESDA/JEDEC JS-002-2018 /IEC 60749-28/AEC-Q100-11。這三個詳規都是針對封裝后的芯片。

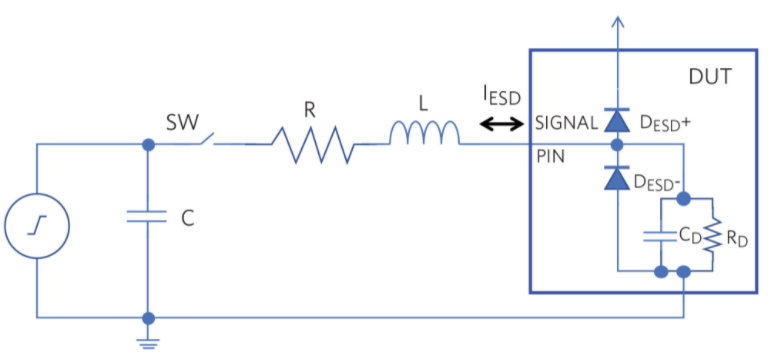

與HBM類似,CDM的測試儀器也只能提供一個靜態結果,并不能得到芯片在ESD電流下的動態結果。所以采用VF-TLP對CDM波形進行近似,但是目前VF-TLP的近似程度較差,只能起到參考作用。

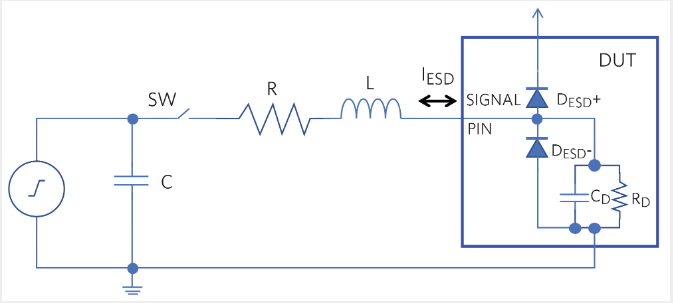

目前主流CDM的測試方法有兩種:一種是直接接觸測試。一種是電場測試。

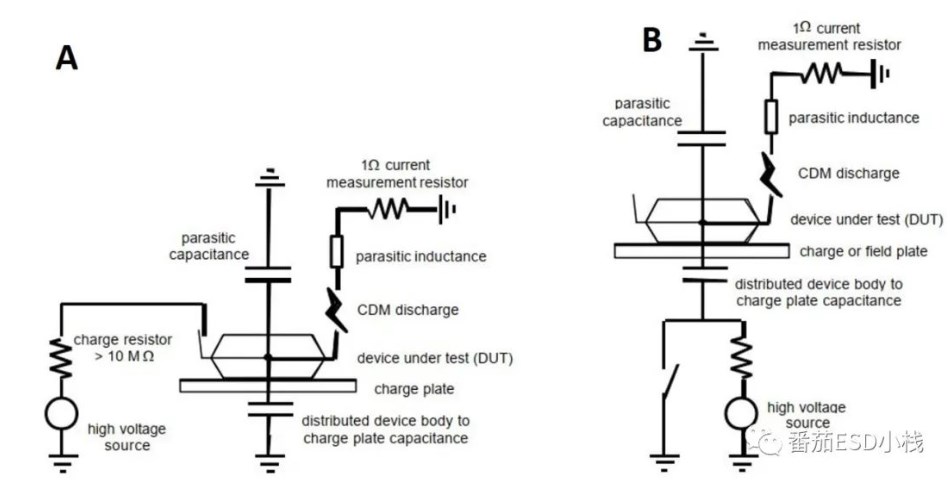

圖二.不同CDM測試方法,A.直接接觸測試,B.電場充放電測試。

直接接觸測試就是將探針直接與芯片引腳或者襯底接觸,提高探針的電勢從而對待測芯片進行充電,然后待測引腳連接另一根探針進行放電,實現CDM防護能力驗證。電場充放電檢測是將待測芯片放置到充電平板上,抬升充電平板的電勢能,從而對待測芯片進行充電。筆者所經手項目多以FI-CDM(電場放電測試)為主。

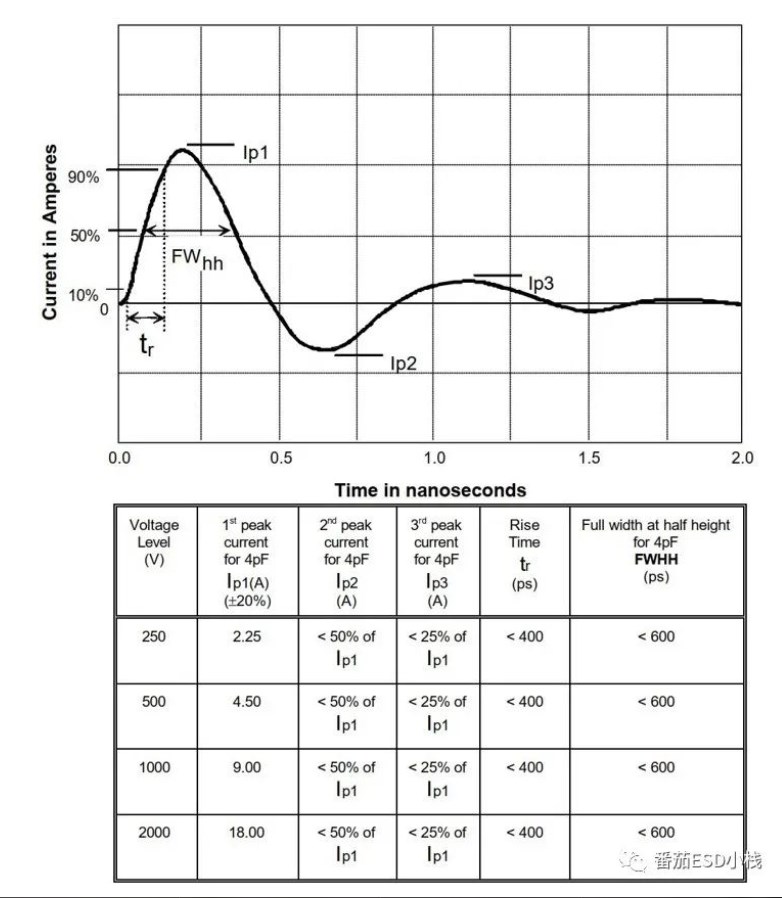

圖三.CDM脈沖校驗參數與波形。

測試前需要對脈沖波形進行檢測,滿足要求后才能對待測芯片進行測試。而針對待測芯片在測試前和測試后都需要進行ATE測試,從而校驗芯片是否失效。筆者也曾遇到在ESD測試后多次ATE結果不一的情況,ESD測試后即刻ATE結果表明芯片已經失效,而一段時間后的ATE又與之前的ATE結果相左,芯片似乎恢復正常了。這種情況筆者也是較為頭疼,從System ESD的角度來看,這種情況類似于Class C失效,其內部元器件肯定發生了損傷。

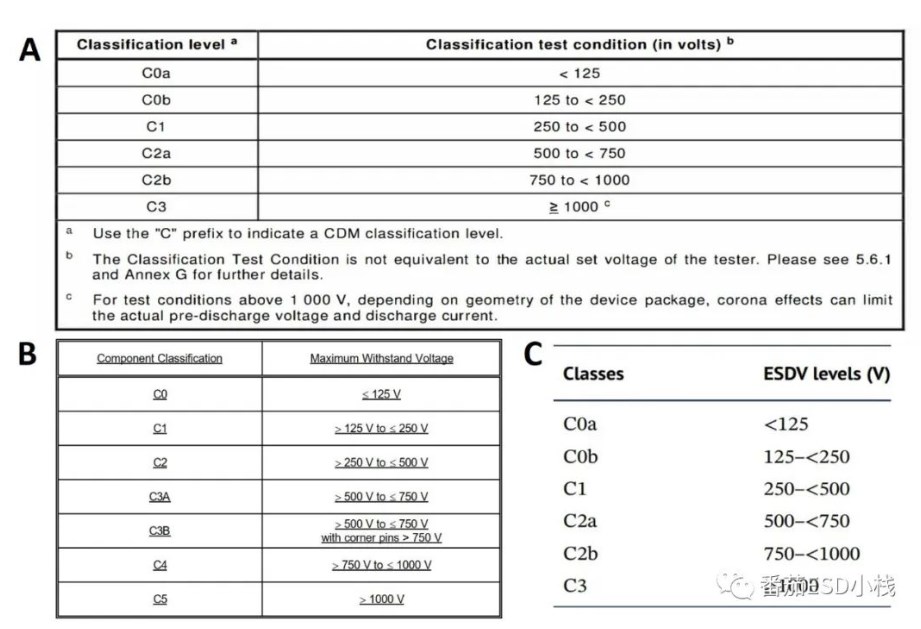

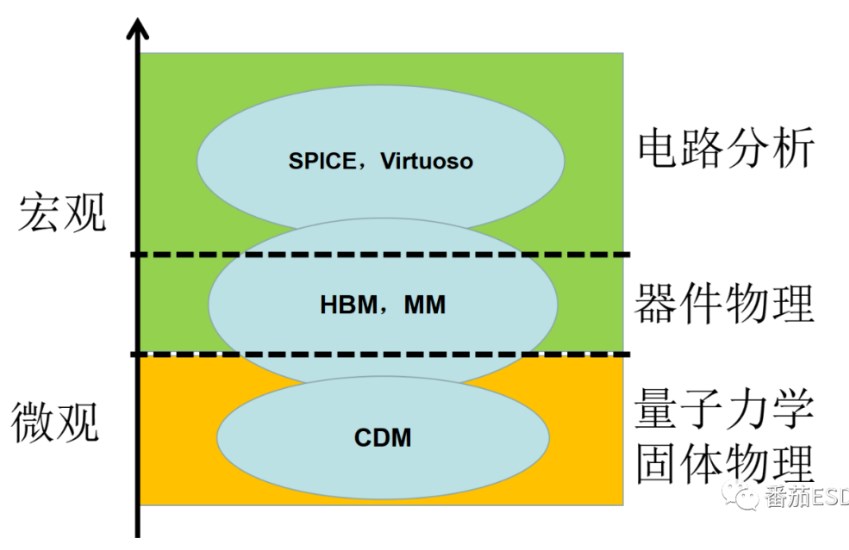

圖四.IEC 60749-28/AEC-Q100-11ANSI/ESDA/JEDEC JS-002-2018 對CDM防護等級。

不同標準針對CDM防護等級的分類大同小異,都是以125V,250V,500V,750V,1000V進行劃定。但是車規級AEC-Q100中單獨提到了Corner Pin的問題。Corner Pin是指位于封裝角落處的引腳,在DIP,SOIC,QFP,PLCC等封裝方式中較為常見,其它的封裝形式則需要工程師根據封裝方案進行判斷,這類引腳與GND的接觸概率較大,所面對的風險較高,所以需要格外關注其CDM防護能力。

四.CDM失效分析

CDM的失效基本都集中在柵級,尤其是隨著工藝線寬的縮減,柵氧化層的厚度越來越薄,其失效風險也顯著增加。像.35這種大線寬工藝,筆者在電路設計中未考慮CDM防護,其CDM測試結果反倒出人意料的好。所以越先進的工藝越需要重視CDM風險。

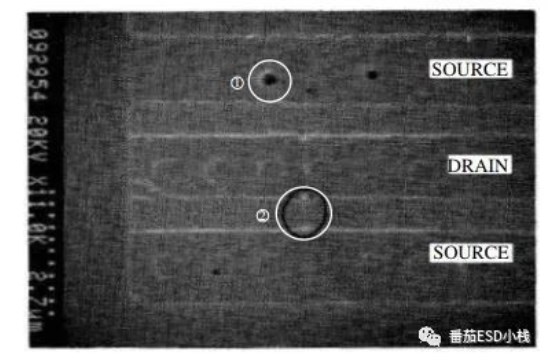

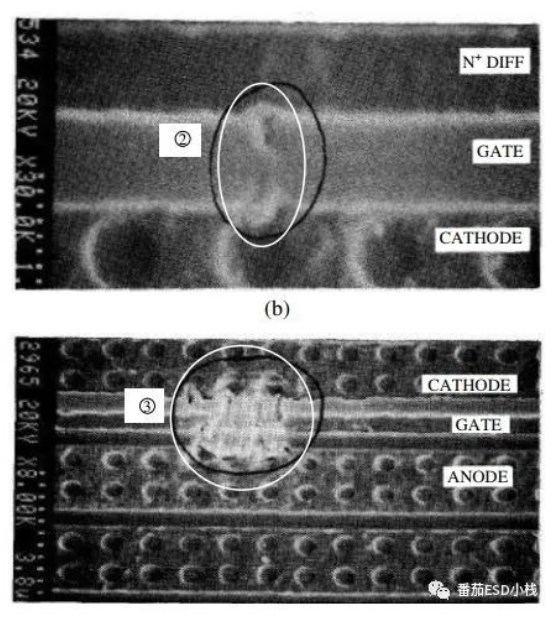

圖五.GCNMOS的ESD失效分析SEM圖像,②處為CDM損傷。

圖六.GGNMOS和SCR的ESD失效分析SEM圖像。

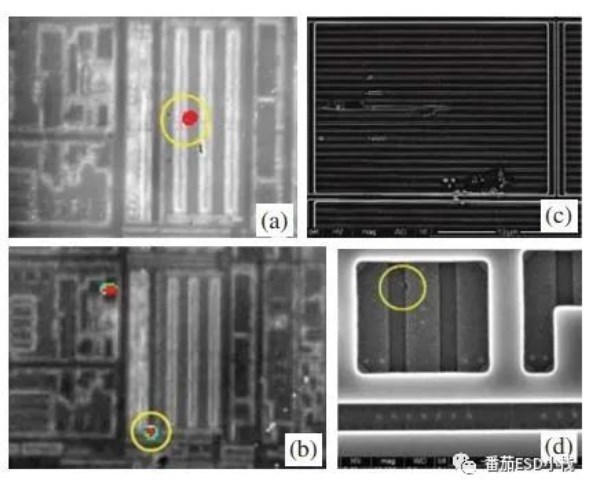

圖七.45nm工藝下不同類型ESD失效SEM圖像,a,c)HBM失效,b,d)CDM失效。

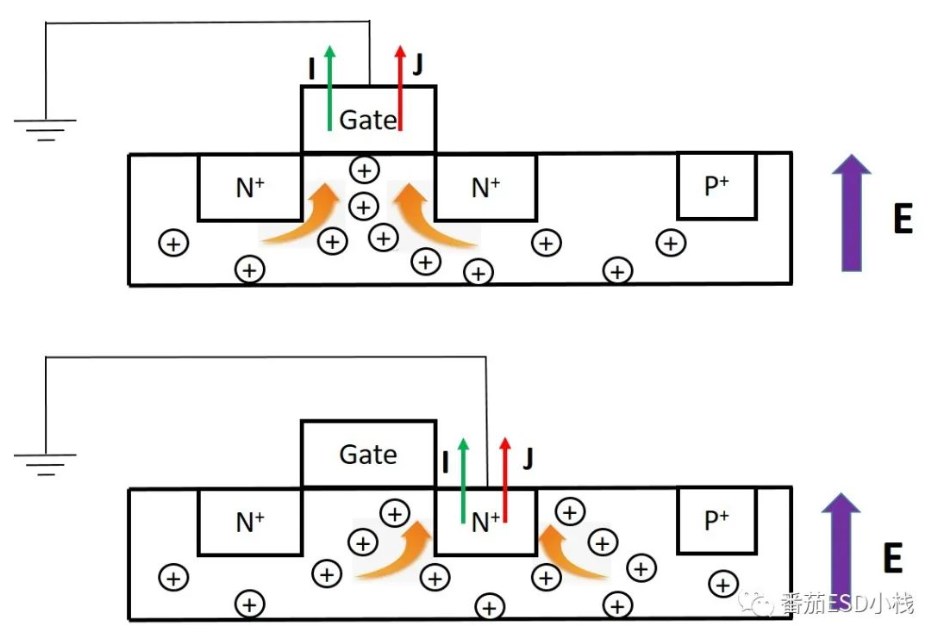

大量的實例都能看出CDM的失效全部集中在柵極。針對NMOS,正向電場下大量非平衡載流子(空穴)集中于襯底中,而當柵極接地后,柵電容兩側就會集聚大量正電荷,這部分載流子會抬高兩邊的電勢差,當電勢差過高時柵電容就會被擊穿。

圖八.NMOS-CDM示意圖。

而如果NMOS的源端或者漏端接地,因為襯底與有源區構成寄生二極管。襯底(P-WeLL)在CDM測試中為高電位,N+有源區為低電位,載流子就會從寄生二極管流出。

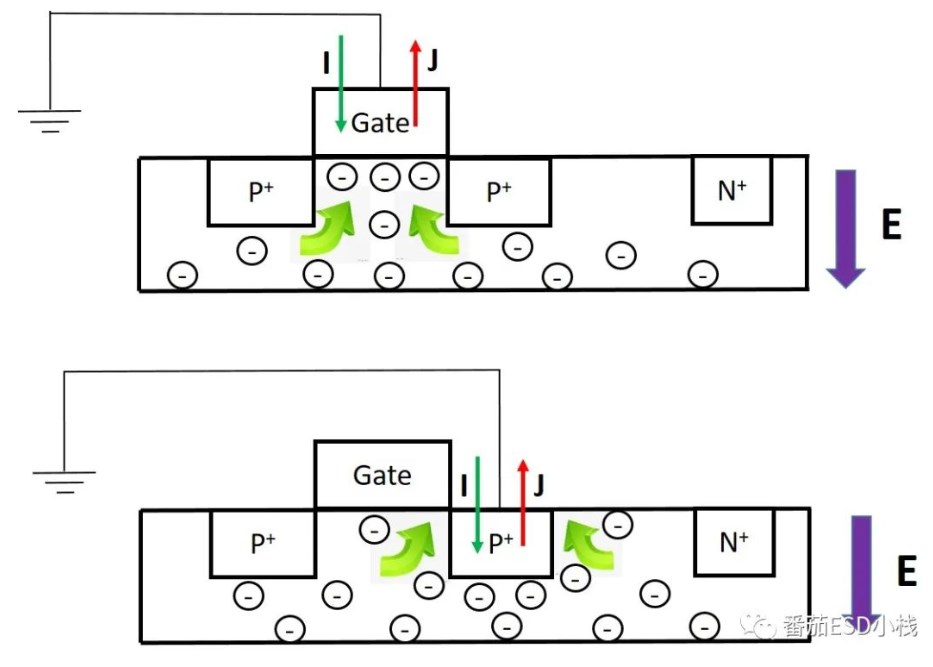

圖九.PMOS-CDM示意圖。

PMOS與NMOS類似,不過就是PMOS是在負場下發生CDM,其襯底內會集聚大量電子。

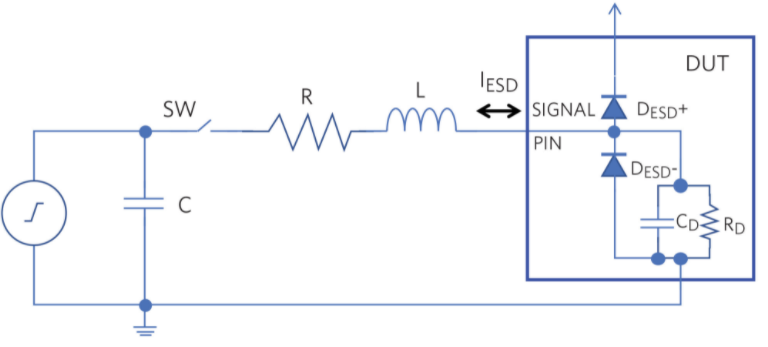

從電路的角度分析,CDM對柵極造成了損傷,使得電路功能發生異常。從器件物理的角度分析,CDM電荷積聚會對柵氧化層會造成物理上的破壞,圖中可以看出CDM脈沖造成了柵氧化層出現了空洞。

圖十.AFM下CDM失效圖像。

所以CDM防護需要重點關注對于柵極的保護,但是并不一定所有的柵極損傷都是由CDM造成,尤其是輸入端口的ESD事件,HBM和MM也會對柵極造成損傷。

-

ESD

+關注

關注

49文章

2221瀏覽量

174330 -

DIP封裝

+關注

關注

1文章

41瀏覽量

13741 -

CDM

+關注

關注

0文章

30瀏覽量

12335 -

GND

+關注

關注

2文章

540瀏覽量

39163

發布評論請先 登錄

相關推薦

什么是失效分析?失效分析原理是什么?

什么是小尺寸集成電路CDM測試?

失效分析方法---PCB失效分析

芯片IC可靠性測試、靜電測試、失效分析

芯片IC可靠性測試、ESD測試、FA失效分析

HBM、MM和CDM測試的基礎知識

HBM、MM和CDM測試的基礎知識

常用的芯片失效分析方法

淺談CDM的原因與機理

季豐電子CDM測試機已全部配備高帶寬的6G示波器

評論