對(duì)于DFF,之前理解的,DFF在時(shí)鐘的上升沿進(jìn)行對(duì)D端的數(shù)據(jù)采集,再下一個(gè)時(shí)鐘的上升沿來臨,Q端輸出D端采集的數(shù)據(jù)。能這么理解,是離開書本時(shí)間太長了,又觀察到了ModelSim仿真波形的影響,這么理解只是在描述仿真波形的表征現(xiàn)象,并非根本的原理。比如,在Modelsim仿真中,若通過DFF將數(shù)據(jù)組進(jìn)行延時(shí),用時(shí)鐘將寄存器進(jìn)行多個(gè)時(shí)鐘周期的同步,并帶有異步復(fù)位,對(duì)應(yīng)Verilog描述如下:

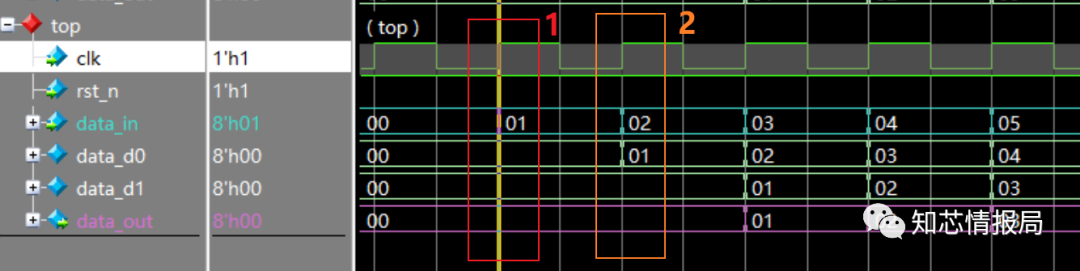

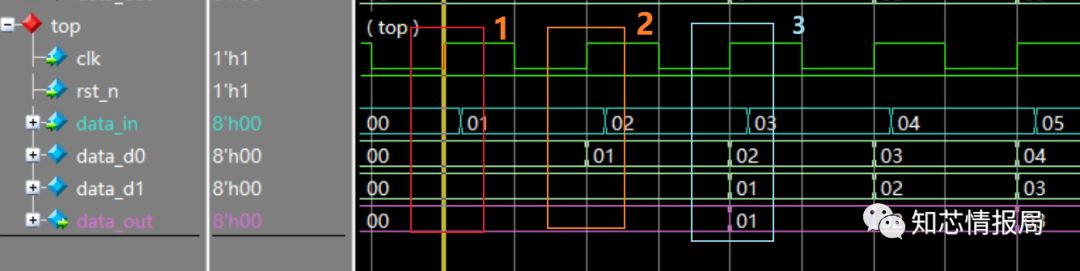

reg [7:0] data_d0, data_d1, data_d2; always @ ( posedge clk or negedge rst_n ) begin if ( !rst_n ) begin data_d0 <= 8'b0; data_d1 <= 8'b0; end else begin data_d0 <= data_in; data_d1 <= data_d0; end end對(duì)應(yīng)仿真波形如下:

? ???????

? ???????此時(shí),時(shí)鐘上升沿和數(shù)據(jù)的變化沿都是對(duì)齊的,就產(chǎn)生了不正確的理解:通過Modelsim的wave窗口查看仿真波形的時(shí)候,如果將光標(biāo)打到時(shí)鐘的上升沿時(shí)候(比如心在光標(biāo)在Event 1時(shí)刻),對(duì)應(yīng)的數(shù)據(jù)data_in應(yīng)該是從8‘h00->8‘h0’1,可是光標(biāo)處data_in的數(shù)值顯示為8’h01。

這樣,我就理解成了在Even1時(shí)刻,時(shí)鐘的上升沿對(duì)data_in(值為8’h01)進(jìn)行捕獲(接入到寄存器data_d0的D端),在下一個(gè)時(shí)鐘的上升沿到來的時(shí)刻(Event2時(shí)刻),寄存器data_d0的Q端數(shù)據(jù)發(fā)生改變(值為8’h01)。上述理解完全是根據(jù)波形描述出來的,是不全面的,是非本源的,是錯(cuò)誤的。

正確的理解

正確的理解應(yīng)該從DFF本身出發(fā),通過DFF的電路原理圖分析DFF的電路工作原理,了解時(shí)鐘上升沿之前和之內(nèi)部邏輯的如何變化,如何影響了從D端到Q端的數(shù)據(jù)輸出。

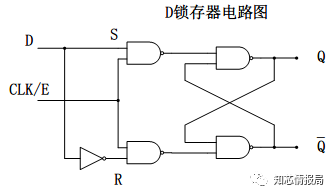

D鎖存器

在網(wǎng)上找到的很多電路圖講的都是D鎖存器,D鎖存器的電路為消除邏輯門控SR鎖存器不確定狀態(tài),在電路的S和R輸入端連接一個(gè)非門(Inverter),從而保證了S和R同時(shí)為0的條件,參考下圖由與非門構(gòu)成的D鎖存器電路圖:

如果D信號(hào)在E=1期間發(fā)生變化,電路提供的信號(hào)路徑將使Q端信號(hào)跟隨D端變化。

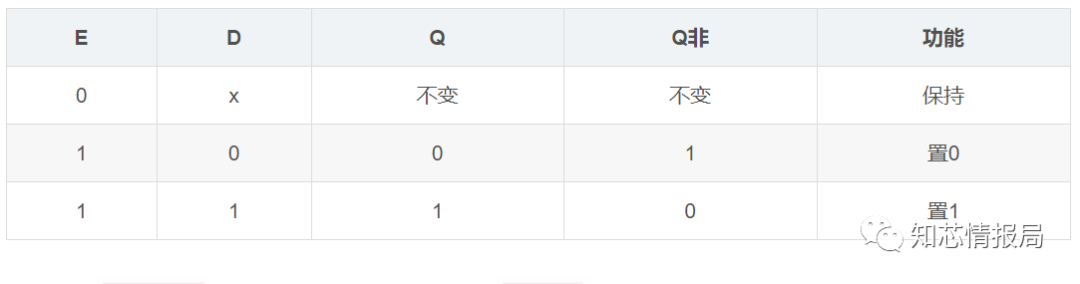

在E由1跳變?yōu)?以后,鎖存器將鎖存跳變前瞬間D端的邏輯值,可以暫存1位二進(jìn)制數(shù)據(jù)。又因?yàn)橛蠭nverter的存在,SR鎖存器不會(huì)存在S&R==1的狀態(tài),所以就有了D鎖存器的捕獲數(shù)據(jù),E為0的時(shí)候會(huì)一直維持?jǐn)?shù)據(jù)狀態(tài)。此D鎖存器的功能表為:

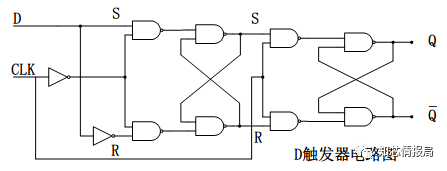

D觸發(fā)器

觸發(fā)和觸發(fā)器——時(shí)鐘脈沖邊沿作用下的狀態(tài)刷新稱為觸發(fā),具有這種特性的存儲(chǔ)單元電路稱為觸發(fā)器。D觸發(fā)器的電路圖如下(圖中的SR為了標(biāo)注有兩級(jí)SR鎖存器,方便邏輯推理):

以上升沿觸發(fā)為例,進(jìn)一步分析D觸發(fā)器在上升沿捕獲數(shù)據(jù),并維持鎖存的過程。

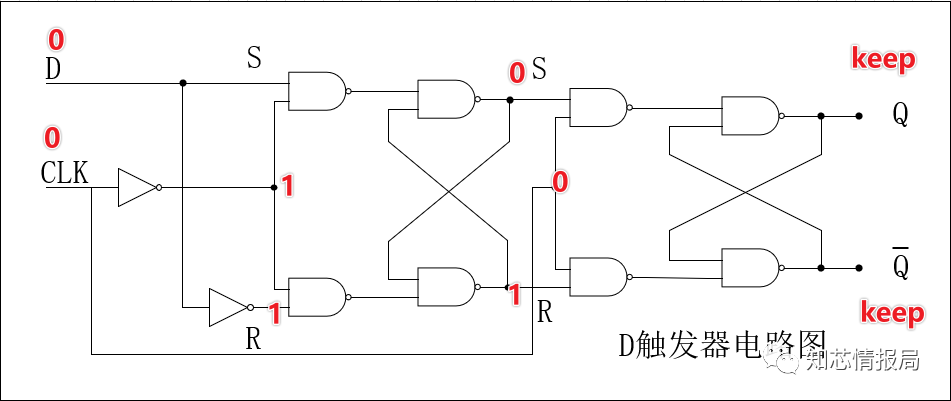

當(dāng)D端為0,CLK為0時(shí),此時(shí)第一級(jí)的D鎖存器輸出為0,第二級(jí)SR鎖存器處于保持狀態(tài),詳情參考下圖:

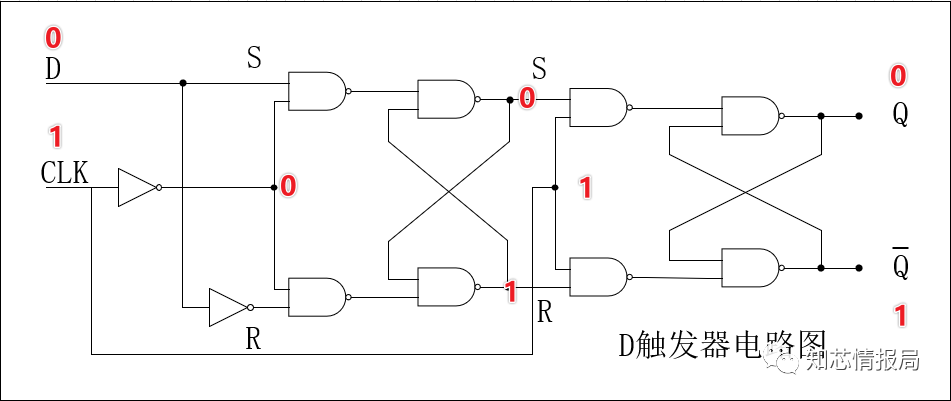

若繼續(xù)保持D端為0,CLK變?yōu)?時(shí),第一級(jí)D鎖存器處于保持狀態(tài),第二級(jí)的SR鎖存器將上一次的D值傳遞到Q端輸出,詳情參考下圖:

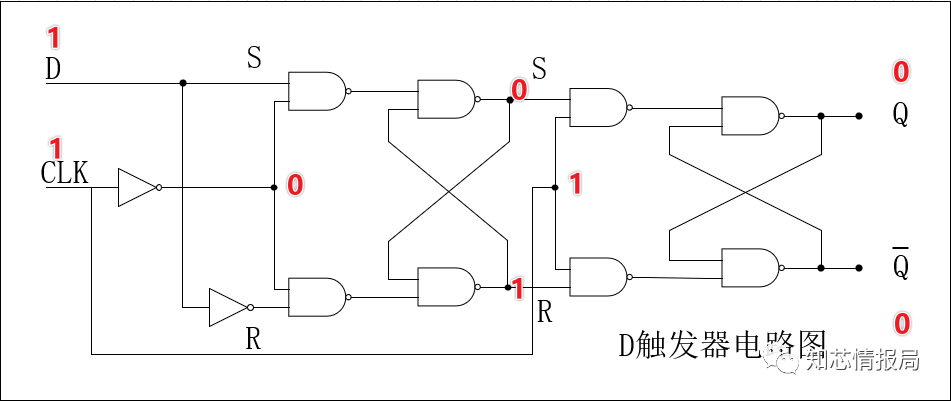

若在D端數(shù)值發(fā)生改變?yōu)?,且CLK仍然為1,第一級(jí)的D鎖存器仍處于保持狀態(tài),不會(huì)由于D端的變化而改變,更不會(huì)影響最后Q端的輸出。

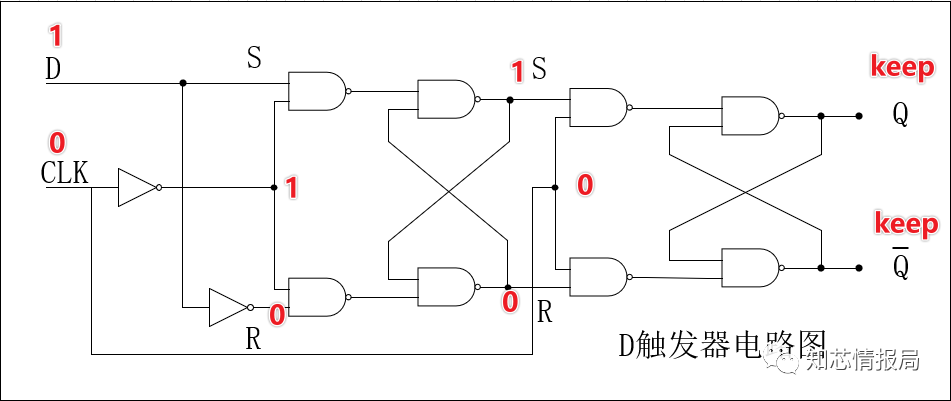

若D端繼續(xù)保持為1,CLK轉(zhuǎn)換為0,此時(shí)第一級(jí)D鎖存器的輸出為D端的數(shù)據(jù),Q端輸出仍為保持狀態(tài)。

若D端數(shù)據(jù)繼續(xù)保持為1,CLK轉(zhuǎn)換為高,第一級(jí)D鎖存器的結(jié)果就會(huì)輸出到Q端,Q端的值也就隨著CLK的上升沿,捕獲到了1,并進(jìn)行輸出到Q端;

從邏輯圖中,也可以看出DFF的數(shù)據(jù)捕獲和輸出都需要滿足一定的時(shí)間約束。比如:

時(shí)鐘上升沿之前前后的數(shù)據(jù)要做夠穩(wěn)定,否則在時(shí)鐘跳變時(shí)刻,可能無法將其傳遞到Q端進(jìn)行輸出;

時(shí)鐘上升沿捕獲數(shù)據(jù)之后,到Q端輸出也需要一定的時(shí)間,穩(wěn)定之后才能用于下一級(jí)工作;

DFF捕獲時(shí)鐘上升沿的D端數(shù)據(jù),并在Q端輸出,一直維持到下一時(shí)鐘上升沿到來之前。在此期間,D端的數(shù)據(jù)變化不會(huì)直接影響到Q端的輸出。

ModelSim仿真

將tb文件中的data_in輸入做5個(gè)單位的傳輸延時(shí),仿真結(jié)果見下圖:

????????

????????

可以看出,在時(shí)鐘的上升沿前后數(shù)據(jù)是不發(fā)生變化的,對(duì)于寄存器做延時(shí)的時(shí)序理解為:

Event 1時(shí)刻:

在Event 1時(shí)刻,時(shí)鐘上升沿之前data_in(值為8’h00),data_d0的D端為data_in(值為8’h00);

在Event 1時(shí)刻,時(shí)鐘上升沿之后data_in(值為8’h00),data_d0的Q端為data_in(值為8’h00);所以在Event 1時(shí)刻,data_d0的Q端保持為8’h00不變;

Event 2時(shí)刻:

在Event 2時(shí)刻,時(shí)鐘上升沿之后data_in(值為8’h01),data_d0的D端為data_in(值為8’h01);

在Event 2時(shí)刻,時(shí)鐘上升沿之后data_in(值為8’h01),data_d0的D端為data_in(值為8’h01);所以在Event 2時(shí)刻,data_d0的Q端從8’h00變?yōu)?’h01;

Event 3時(shí)刻:

在Event 3時(shí)刻,時(shí)鐘上升沿之后data_in(值為8’h02),data_d0的D端為data_in(值為8’h02);

在Event 3時(shí)刻,時(shí)鐘上升沿之后data_in(值為8’h02),data_d0的D端為data_in(值為8’h02);所以在Even 3時(shí)刻,data_d0的Q端從8’h01變?yōu)?’h02;

可以看出在Event 1到Event 2一個(gè)時(shí)鐘周期內(nèi),data_d0的數(shù)值保持為8’h00;Event 1到Event 2一個(gè)時(shí)鐘周期內(nèi),data_d0的數(shù)值保持為8’h01;在時(shí)序上就表明了使用data_d0寄存器,通過clk對(duì)data_in進(jìn)行了1個(gè)時(shí)鐘周期的延時(shí)。在Modelsim仿真中,若數(shù)據(jù)的變化沿與時(shí)鐘的上升沿對(duì)齊,cursor在時(shí)鐘上升沿時(shí)刻,對(duì)應(yīng)的數(shù)據(jù)需要往后加入延時(shí),才能與實(shí)際電路情況相符合。

總結(jié)

DFF捕獲時(shí)鐘上升沿的D端數(shù)據(jù),并在Q端輸出,一直維持到下一時(shí)鐘上升沿到來之前。在此期間,D端的數(shù)據(jù)變化不會(huì)直接影響到Q端的輸出。

審核編輯:劉清

-

寄存器

+關(guān)注

關(guān)注

31文章

5357瀏覽量

120660 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110158 -

時(shí)序電路

+關(guān)注

關(guān)注

1文章

114瀏覽量

21720 -

MODELSIM仿真

+關(guān)注

關(guān)注

0文章

15瀏覽量

7321 -

dff

+關(guān)注

關(guān)注

0文章

26瀏覽量

3424

原文標(biāo)題:時(shí)序電路之DFF再理解

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)字電路之時(shí)序電路

時(shí)序電路的分析與設(shè)計(jì)方法

什么是時(shí)序電路

組合電路和時(shí)序電路的講解

時(shí)序電路之觸發(fā)器

DFF的電路工作原理與ModelSim仿真

時(shí)序電路基本介紹

什么是時(shí)序電路?

什么是同步時(shí)序電路和異步時(shí)序電路,同步和異步電路的區(qū)別?

時(shí)序電路之DFF理解

時(shí)序電路之DFF理解

評(píng)論