一、AMBA概述

AMBA (Advanced Microcontroller Bus Architecture) 高級微處理器總線架構(gòu)定義了高性能嵌入式微控制器的通信標(biāo)準(zhǔn),可以將RISC處理器(精簡指令集處理器)集成在其他IP芯核和外設(shè)中,它是有效連接IP核的“數(shù)字膠”,并且是ARM復(fù)用策略的重要組件;它不是芯片與外設(shè)之間的接口,而是ARM內(nèi)核與芯片上其他元件進(jìn)行通信的接口。比如Xilinx公司的Zynq芯片,就是ARM與FPGA之間的連接通路 .主要包括:

AHB (Advanced High-performance Bus) 高級高性能總線

ASB (Advanced System Bus) 高級系統(tǒng)總線----用的很少

APB (Advanced Peripheral Bus) 高級外圍總線

AXI (Advanced eXtensible Interface) 高級可拓展接口

這些內(nèi)容加起來就定義出一套為了高性能SoC而設(shè)計的片上通信的標(biāo)準(zhǔn);

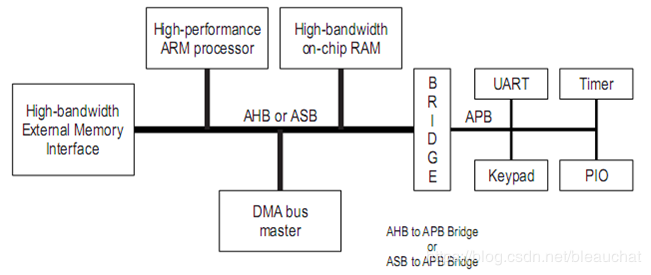

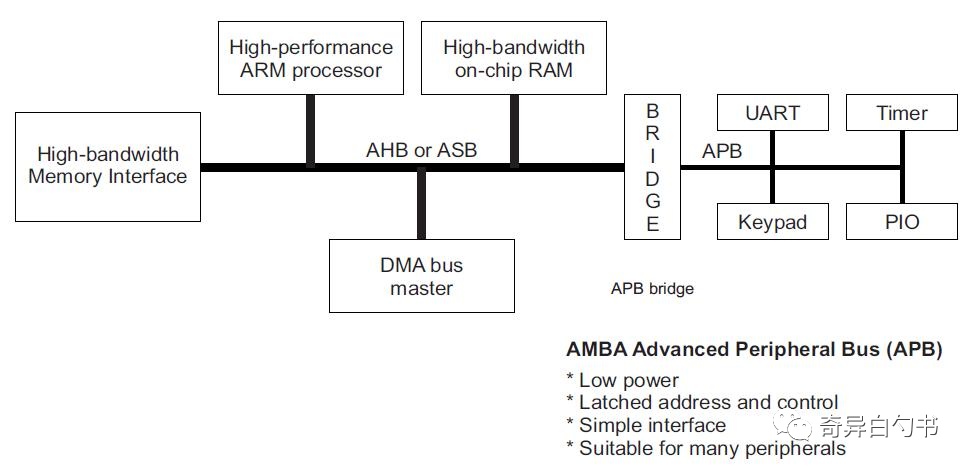

AHB主要是針對高效率、高頻寬及快速系統(tǒng)模塊所設(shè)計的總線,它可以連接如微處理器、芯片上或芯片外的內(nèi)存模塊和DMA等高效率模塊;

APB主要用在低速且低功率的外圍,可針對外圍設(shè)備作功率消耗及復(fù)雜接口的最佳化;APB在AHB和低帶寬的外圍設(shè)備之間提供了通信的橋梁,所以APB是AHB或ASB的二級拓展總線 ;

AXI:高速度、高帶寬,管道化互聯(lián),單向通道,只需要首地址,讀寫并行,支持亂序,支持非對齊操作,有效支持初始延遲較高的外設(shè),連線非常多;

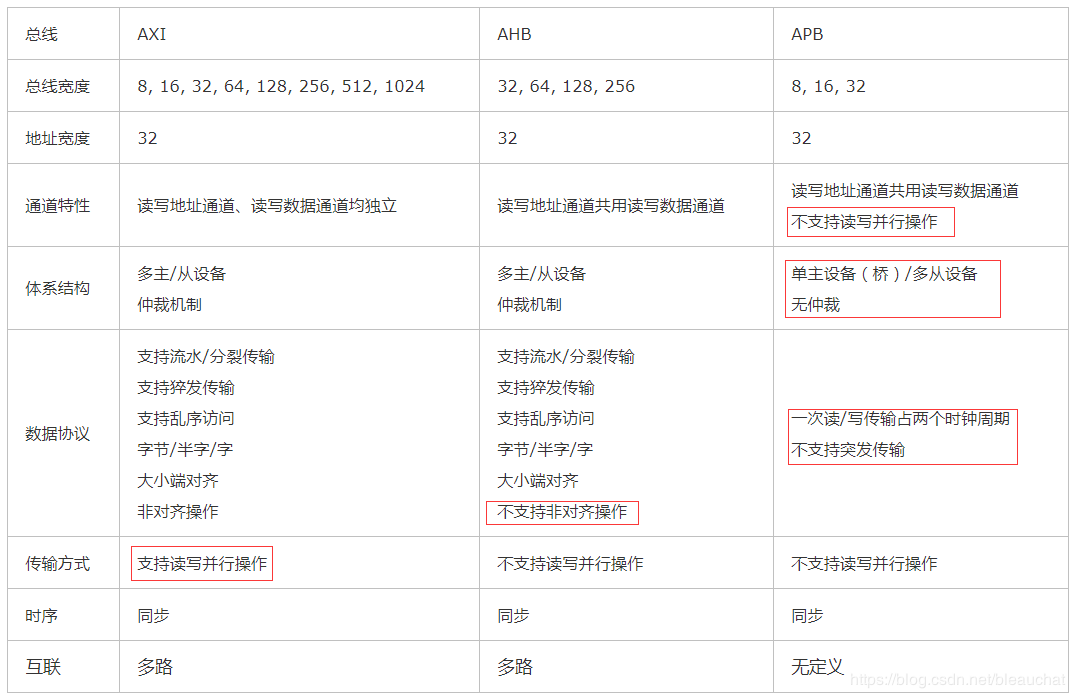

幾種AMBA總線的性能對比分析:

AHB與AXI、APB的區(qū)別與聯(lián)系

AHB是先進(jìn)的高性能總線,AXI是先進(jìn)的可擴展接口,APB是高級外圍總線;

AHB和APB都是單通道總線,不支持讀寫并行;而AXI是多通道總線,總共分為五個通道,能夠?qū)崿F(xiàn)讀寫并行;

AHB和AXI都是多主/從設(shè)備,且通過仲裁機制實現(xiàn)總線控制權(quán)的分配;而APB是單主設(shè)備多從設(shè)備,其主設(shè)備就是APB橋,不具有仲裁機制;

在數(shù)據(jù)操作方面,AHB和AXI支持突發(fā)傳輸,APB不支持;此外,AXI支持?jǐn)?shù)據(jù)的非對齊操作,AHB不支持;

二、AHB總線

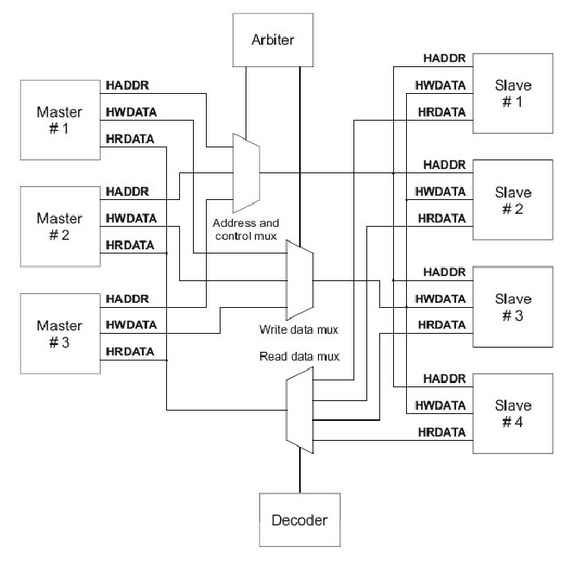

AHB總線強大之處在于它可以將微控制器(CPU)、高帶寬的片上RAM、高帶寬的外部存儲器接口、DMA總線控制器,以及各種AHB接口的控制器等連接起來構(gòu)成一個獨立的完整SOC系統(tǒng),還可以通過AHB-APB橋來連接APB總線系統(tǒng)。主要包括以下四個部分:

Master AHB主控制器:主控制器可以通過地址和控制信息,可以進(jìn)行初始化,讀,寫操作,同一時間只有1個Master會被激活;

Slave AHB從設(shè)備:從設(shè)備通常是指在其地址空間內(nèi),響應(yīng)主控制器發(fā)出的讀寫控制操作的被動設(shè)備,并對Master返回成功、失敗或者等待等狀態(tài),完成數(shù)據(jù)的傳輸控制;

Arbiter AHB仲裁器:仲裁器根據(jù)用戶的配置,確保在總線上同一時間只有一個主控制器擁有總線控制權(quán)限,從而保證總線上一次只有1個Master在工作;AHB總線只能存在一個仲裁器;

Decoder AHB譯碼器:負(fù)責(zé)對地址進(jìn)行解碼,并提供片選信號到各Slave;AHB總線只能有一個譯碼器;

每個AHB都需要1個仲裁器和1個中央解碼器,且有且僅有一個!

*AHB基本信號 *

HADDR:32位系統(tǒng)地址總線;

HTRANS:M指示傳輸狀態(tài),NONSEQ、SEQ、IDLE、BUSY;

HWRITE:傳輸方向1-寫,0-讀;

HSIZE:傳輸單位;

HBURST:傳輸?shù)腷urst類型;

HWDATA:寫數(shù)據(jù)總線,從M寫到S;

HREADY:S應(yīng)答M是否讀寫操作傳輸完成,1-傳輸完成,0-需延長傳輸周期。需要注意的是HREADY作為總線上的信號,它是M和S的輸入;同時每個S需要輸出自HREADY。所以對于S會有兩個HREADY信號,一個來自總線的輸入,一個自己給到多路器的輸出;

HRESP:S應(yīng)答當(dāng)前傳輸狀態(tài),OKAY、ERROR、RETRY、SPLIT;

HRDATA:讀數(shù)據(jù)總線,從S讀到M;

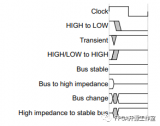

*AHB基本傳輸 *

兩個階段

地址周期(AP),只有一個cycle

數(shù)據(jù)周期(DP),由HREADY信號決定需要幾個cycle

流水線傳送

先是地址周期,然后是數(shù)據(jù)周期

AHB突發(fā)傳輸與AXI突發(fā)傳輸?shù)奶攸c

AHB協(xié)議需要一次突發(fā)傳輸?shù)乃械刂罚刂放c數(shù)據(jù)鎖定對應(yīng)關(guān)系,后一次突發(fā)傳輸必須在前次傳輸完成才能進(jìn)行;

AXI只需要一次突發(fā)的首地址,可以連續(xù)發(fā)送多個突發(fā)傳輸首地址而無需等待前次突發(fā)傳輸完成,并且多個數(shù)據(jù)可以交錯傳遞,此特征大大提高了總線的利用率;

AHB總線與AXI總線均適用于高性能、高帶寬的SoC系統(tǒng),但AXI具有更好的靈活性,而且能夠讀寫通道并行發(fā)送,互不影響;更重要的是,AXI總線支持亂序傳輸,能夠有效地利用總線的帶寬,平衡內(nèi)部系統(tǒng)。因此SoC系統(tǒng)中,均以AXI總線為主總線,通過橋連接AHB總線與APB總線,這樣能夠增加SoC系統(tǒng)的靈活性,更加合理地把不同特征IP分配到總線上;

三、APB總線

APB是一種優(yōu)化的,低功耗的,精簡接口總線,可以技術(shù)多種不同慢速外設(shè);主要應(yīng)用在低帶寬的外設(shè)上,如UART、 I2C,它的架構(gòu)不像AHB總線是多主設(shè)備的架構(gòu),APB總線的唯一主設(shè)備是APB橋(與AXI或APB相連),因此不需要仲裁一些Request/grant信號。

APB總線協(xié)議包含一個APB橋,它用來將AHB,ASB總線上的控制信號轉(zhuǎn)化為APB從設(shè)備控制器上可用信號。APB總線上所有的外設(shè)都是從設(shè)備,這些從設(shè)備有以下特點:

a 接收有效的地址和控制訪問

b 當(dāng)APB上的外設(shè)處于非活動狀態(tài)時,可以將這些外設(shè)處于0功耗狀態(tài)

c 譯碼器可以通過選通信號,提供輸出時序(非鎖定接口)

d 訪問時可執(zhí)行數(shù)據(jù)寫入

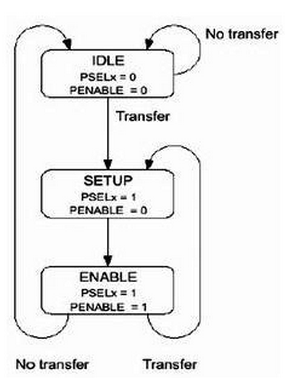

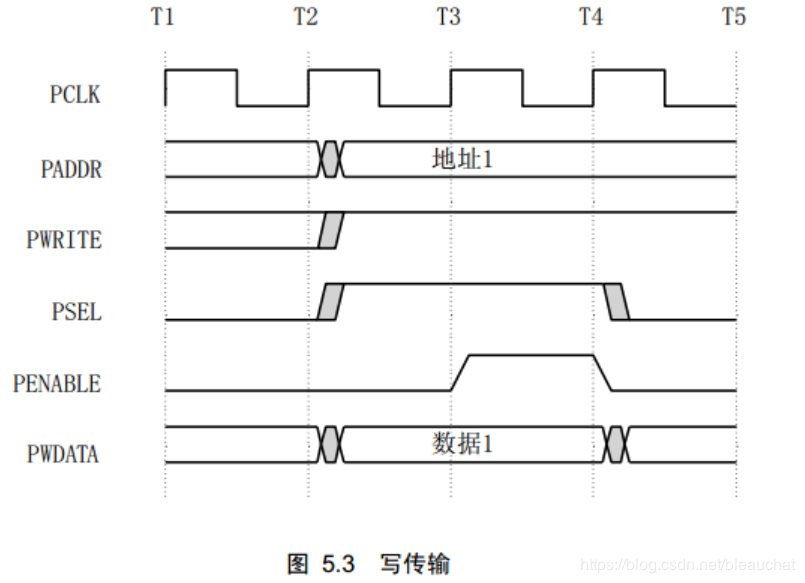

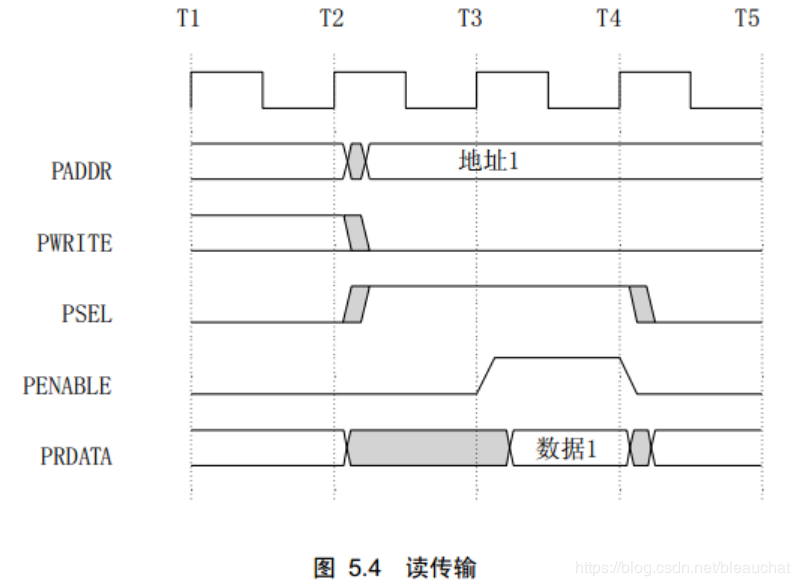

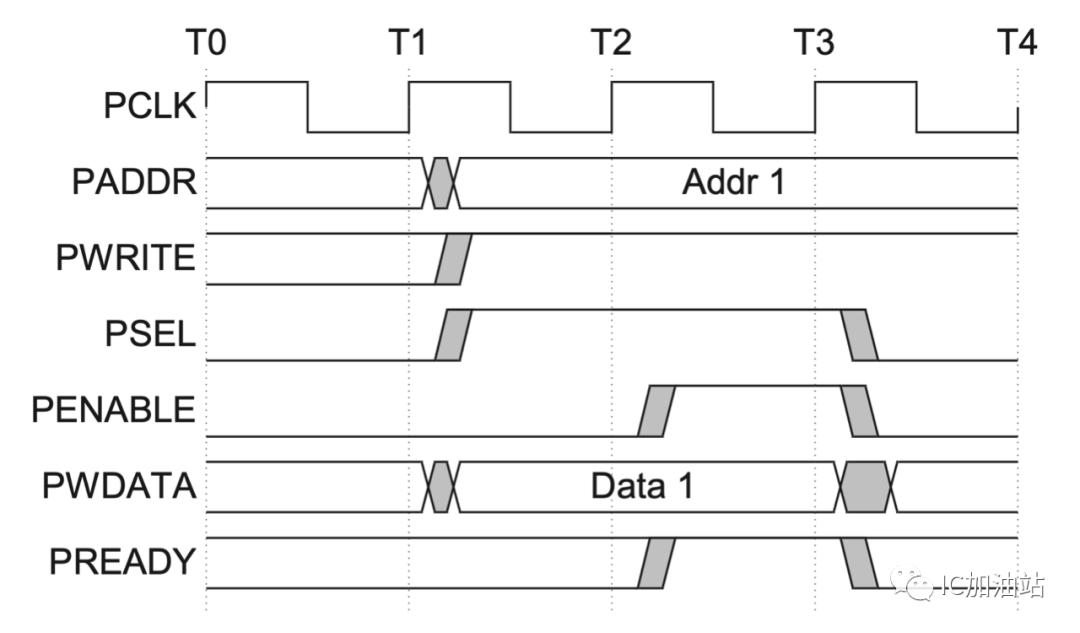

APB的協(xié)議也十分簡單,甚至不是流水的操作,固定兩個時鐘周期完成一次讀或?qū)懙牟僮鳌F涮匦园ǎ簝蓚€時鐘周期傳輸,無需等待周期和回應(yīng)信號,控制邏輯簡單,只有四個控制信號。APB上的傳輸可用如圖所示的狀態(tài)圖來說明:

1、系統(tǒng)初始化為IDLE狀態(tài),此時沒有傳輸操作,也沒有選中任何從模塊;

2、當(dāng)有傳輸要進(jìn)行時,PSELx=1,,PENABLE=0,系統(tǒng)進(jìn)入SETUP狀態(tài),并只會在SETUP狀態(tài)停留一個周期。當(dāng)PCLK的下一個上升沿到來時,系統(tǒng)進(jìn)入ENABLE狀態(tài);

3、系統(tǒng)進(jìn)入ENABLE狀態(tài)時,維持之前在SETUP狀態(tài)的PADDR、PSEL、PWRITE不變,并將PENABLE置為1。傳輸也只會在ENABLE狀態(tài)維持一個周期,在經(jīng)過SETUP與ENABLE狀態(tài)之后就已完成。之后如果沒有傳輸要進(jìn)行,就進(jìn)入IDLE狀態(tài)等待;如果有連續(xù)的傳輸,則進(jìn)入SETUP狀態(tài);

- 寫傳輸

- 讀傳輸

四、ASB總線

ASB總線主要用于高性能系統(tǒng)模塊。ASB是可用于AHB不需要的高性能特性的芯片設(shè)計上可選的系統(tǒng)總線。ASB也支持高性能處理器,片上內(nèi)存,片外內(nèi)存提供接口和慢速外設(shè)。高性能,數(shù)據(jù)傳輸,多總線主控制器,突發(fā)連續(xù)傳輸。ASB總線是位于APB總線架構(gòu)之上的用于高性能的總線協(xié)議,它有如下特點:

a 突發(fā)連續(xù)傳輸

b 單管道數(shù)據(jù)傳輸

c 多總線主控制器

五、基于AMBA的片上系統(tǒng)

大多數(shù)掛在總線上的模塊(包括處理器)只是單一屬性的功能模塊:主模塊或者從模塊。主模塊是向從模塊發(fā)出讀寫操作的模塊,如CPU,DSP等;從模塊是接受命令并做出反應(yīng)的模塊,如片上的RAM,AHB/APB 橋等。另外,還有一些模塊同時具有兩種屬性,例如直接存儲器存取(DMA)在被編程時是從模塊,但在系統(tǒng)讀傳輸數(shù)據(jù)時必須是主模塊。

如果總線上存在多個主模塊,就需要仲裁器來決定如何控制各種主模塊對總線的訪問。雖然仲裁規(guī)范是AMBA總線規(guī)范中的一部分,但具體使用的算法由RTL設(shè)計工程師決定,其中兩個最常用的算法是固定優(yōu)先級算法和循環(huán)制算法。AHB總線上最多可以有16個主模塊和任意多個從模塊,如果主模塊數(shù)目大于16,則需再加一層結(jié)構(gòu)(具體參閱ARM公司推出的Multi-layer AHB規(guī)范)。

APB 橋既是APB總線上唯一的主模塊,也是AHB系統(tǒng)總線上的從模塊。其主要功能是鎖存來自AHB系統(tǒng)總線的地址、數(shù)據(jù)和控制信號,并提供二級譯碼以產(chǎn)生APB外圍設(shè)備的選擇信號,從而實現(xiàn)AHB協(xié)議到APB協(xié)議的轉(zhuǎn)換。

-

處理器

+關(guān)注

關(guān)注

68文章

19343瀏覽量

230229 -

Xilinx

+關(guān)注

關(guān)注

71文章

2168瀏覽量

121672 -

總線

+關(guān)注

關(guān)注

10文章

2891瀏覽量

88165 -

AMBA

+關(guān)注

關(guān)注

0文章

68瀏覽量

15013 -

RISC

+關(guān)注

關(guān)注

6文章

463瀏覽量

83769

發(fā)布評論請先 登錄

相關(guān)推薦

AMBA總線概述

ARM總線協(xié)議AMBA中AHB、APB的區(qū)別與聯(lián)系

AMBA、APB、AHB簡介

AMBA總線AHB、APB、AXI性能對比分析及AHB詳解

基于AMBA總線介紹?

深度解讀AMBA、AHB、APB、AXI總線介紹及對比

淺述AMBA-APB總線

介紹AMBA2.0總線

數(shù)字IC驗證:ARM總線協(xié)議AMBA中AHB、APB的簡介、區(qū)別與聯(lián)系

AHB、AXI、APB分類

STM32菜鳥學(xué)習(xí)手冊——AMBA、APB、AHB簡介

AMBA、AHB、APB、AXI總線介紹

AMBA、AHB、APB、AXI總線介紹

評論