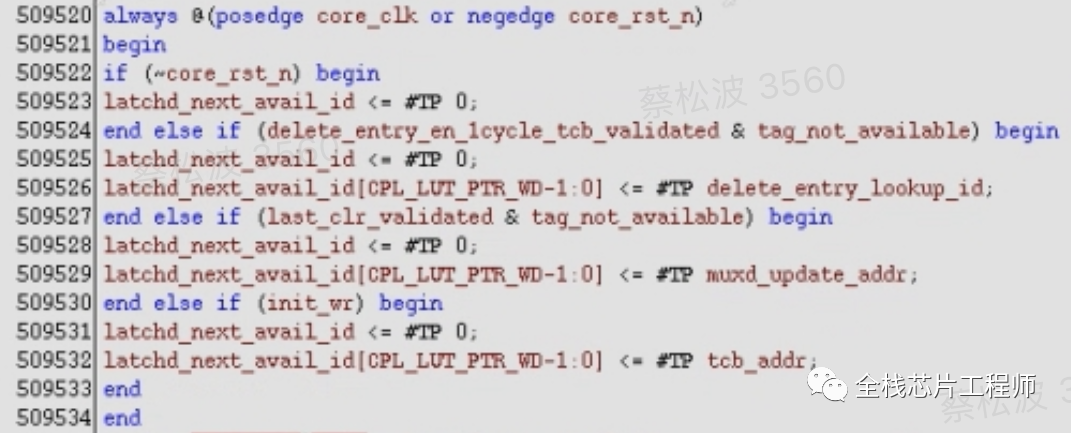

來,看看S家的第509525行PCIe代碼,一個寄存器在一個觸發信號里面賦值兩次,第一句所有bit直接全部賦值0,第二句部分低bit賦值,信號本身是9:0,第二句賦值那個是6:0的寬度。尊貴的ICer,您覺得這樣可以嗎?

作為當代IC designer,看到這種代碼風格首先視覺沖擊就很大,辣眼睛。估計就沒有做lint,是不是很像多驅動的罪名?跑一下lint看看報錯情況。

但必須說明的是,這是S家的老版本代碼了,硬核功能OK的,仿真行為也正確。所以這種代碼風格的設計意圖是后一句覆蓋前一句,前一句先把所有bit賦0,后一句再部分低位bit賦值,那么各家綜合工具編譯會理解錯設計者意圖嗎?個人強烈不推薦這種寫法,雖然SV語法也支持這種,各家綜合工具編譯結果可能有偏差,況且前面的高位賦0,綜合工具直接優化掉0的部分,那寫出來干嘛?為了接口位寬不變,只是里面用的部分按參數定義位寬嗎?還不如直接參數定義總位寬即可,這個就具體問題具體分析,小編造一個簡單實例:

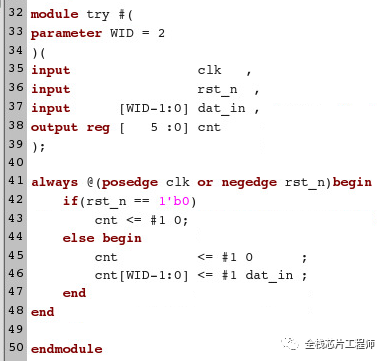

實踐出真知,寫一個代碼實踐下:

spyglass運行lint檢查:

代碼第45行報出來2個warning,我們來分別解析下兩個warning:

(一)第一個warning:STARC05-2.2.3.3,用以發現initial value assignments to flip-flops in always constructs,我們知道,……下文請移步知識星球。

審核編輯:湯梓紅

-

寄存器

+關注

關注

31文章

5343瀏覽量

120427 -

PCIe

+關注

關注

15文章

1239瀏覽量

82687 -

代碼

+關注

關注

30文章

4790瀏覽量

68650 -

編譯

+關注

關注

0文章

659瀏覽量

32877

原文標題:解析PCIe第50萬行代碼的風格

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

向代碼致敬,尋找你的第83行

嵌入式C代碼怎么實現?

800萬行代碼的鴻蒙系統,在世界上處于什么水平?

【HarmonyOS】800萬行代碼的鴻蒙系統,在世界上處于什么水平?

微軟發布了使用最多的應用程序之一——Windows 計算器的源代碼

濤思數據開源TDengine,10多萬行C代碼,登頂GitHub!

移植了20萬行代碼才發現樹莓派Pico雙核MCU竟是三無產品?是真香還是真不香?

什么樣的Verilog代碼風格是好的風格?

為什么 MySQL 單表不能超過 2000 萬行?

再創新高!深開鴻OpenHarmony社區代碼貢獻量超過200萬行!

解析PCIe第50萬行代碼的風格

解析PCIe第50萬行代碼的風格

評論