1.前言

之前做過一個(gè)項(xiàng)目,有個(gè)模塊例化了10次,流片回來測(cè)試,有9個(gè)正常工作,另外一個(gè)工作不起來。這時(shí)這個(gè)模塊的負(fù)責(zé)人就來找我,問到:IR仿真時(shí)這10個(gè)模塊結(jié)果是怎樣的?測(cè)試有問題那個(gè)是IR最差的那個(gè)嗎?后來把仿真結(jié)果拿出來,發(fā)現(xiàn)工作不起來這個(gè)模塊IR不是最差的,結(jié)果和我就沒關(guān)系了。不過后來這個(gè)模塊又可以工作了(具體原因不知道)。

另一個(gè)項(xiàng)目(不是我參與的),工藝不同,還是這個(gè)模塊,不過只例化只有一次,但是流片回來測(cè)試,這個(gè)模塊在func模式下可以正常工作,在scan模式下工作不起來,項(xiàng)目組懷疑是IR問題。結(jié)果后端負(fù)責(zé)人整天到處出差開會(huì)(和foundary廠、項(xiàng)目經(jīng)理、DFT負(fù)責(zé)人等等),雖然已經(jīng)做了很多工作,但是目前還沒有定論。

從以上項(xiàng)目情況可知,芯片流片回來后,測(cè)試有問題,如果定位不到原因,首先會(huì)懷疑IR問題導(dǎo)致的,做IR分析的人就很無辜了,因?yàn)镮R的實(shí)際情況無法測(cè)量(據(jù)某司后端負(fù)責(zé)人講,他們已經(jīng)可以測(cè)出來)。

為啥測(cè)試有問題首先會(huì)懷疑IR結(jié)果?隨著半導(dǎo)體工藝的演進(jìn),金屬線越做越窄(電阻越來越大)、電壓越來越低(噪聲容限越來越小)、電路頻率越來越高(cell 翻轉(zhuǎn)率越來越高)等一些列因素對(duì)IR都不太友好,也導(dǎo)致在先進(jìn)工藝IR分析越來越重要。加之IR沒法實(shí)測(cè),導(dǎo)致有問題不好定位,所以大家也稱IR分析為“玄學(xué)”。

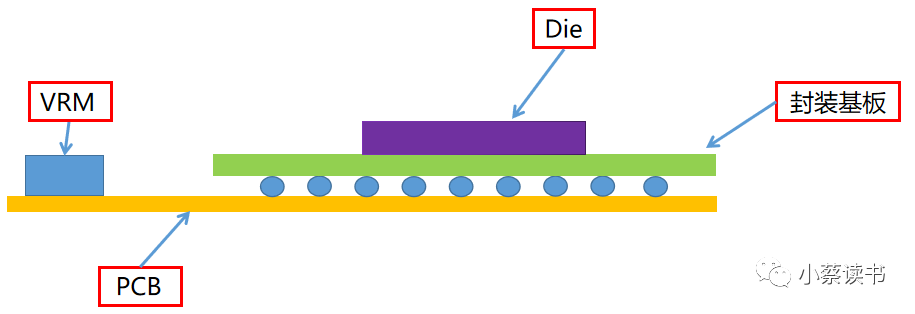

最初想寫這篇文章是在做上一個(gè)項(xiàng)目的時(shí)候。由于項(xiàng)目中有一些加速器設(shè)計(jì)(累加累乘功能),導(dǎo)致這些模塊在die+封裝仿真時(shí),模塊局部IR Drop特別大。當(dāng)時(shí)在沖刺signoff節(jié)點(diǎn),項(xiàng)目經(jīng)理和開發(fā)的人就問這個(gè)IR Drop不滿足標(biāo)準(zhǔn)到底有啥影響?可以waive不?哈哈,我就想說你不想讓流片回來芯片測(cè)試時(shí)正常工作你就waive吧。不過言歸正傳,IR Drop對(duì)芯片性能(timing)到底有什么影響?

2.IR Drop定義

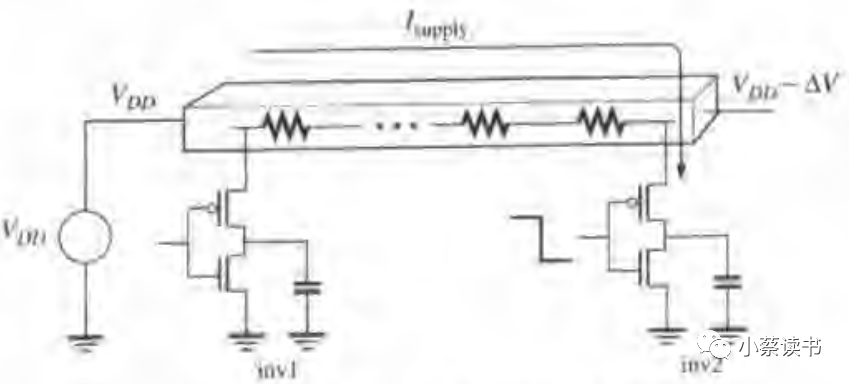

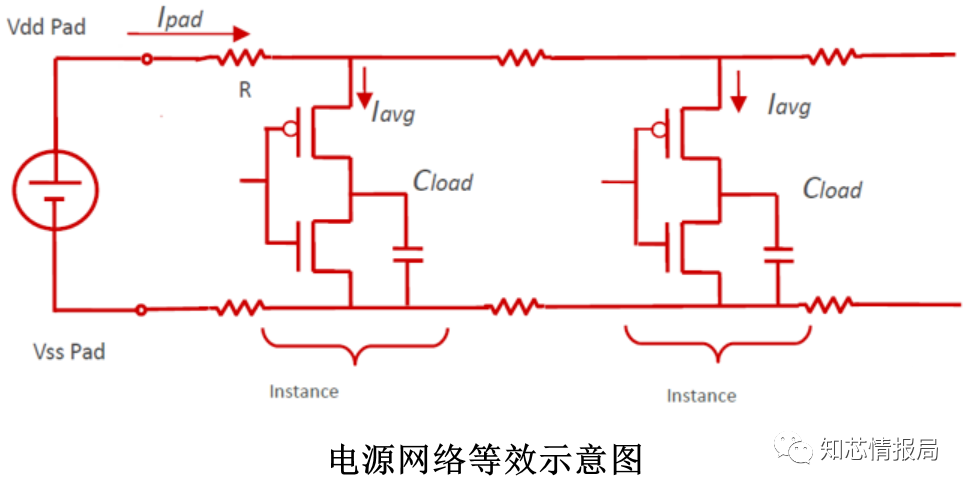

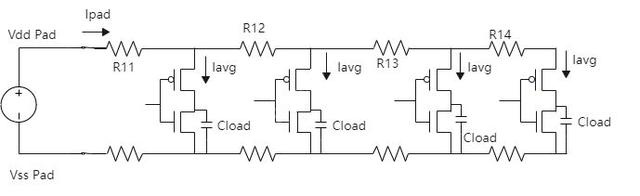

如下圖所示,描述了連接在一個(gè)有阻抗的電源上的兩個(gè)大緩沖器。最初,所有電源網(wǎng)格中的電平處于VDD。當(dāng)大驅(qū)動(dòng)器inv2開始變化時(shí),對(duì)電流的需求降低了電源網(wǎng)格的電壓。特別是導(dǎo)線電阻產(chǎn)生的電壓降會(huì)隨著電流從外部電源向inv2的流動(dòng)而增加。在芯片外圍的VDD連接點(diǎn)附近的電壓保持相當(dāng)高的水平,在連接到inv2時(shí)有V的壓降。實(shí)際上,IR壓降是由于時(shí)鐘緩沖器、總線驅(qū)動(dòng)器、存儲(chǔ)器譯碼驅(qū)動(dòng)器等的同時(shí)變化引起的。這些同時(shí)變化事件可以在芯片上的任何地方發(fā)生,因此,所有區(qū)域都可能受到IR壓降問題的影響。當(dāng)輸出電平變到低時(shí)地線網(wǎng)格也會(huì)受同樣類型問題的影響,只是這時(shí)的電壓值會(huì)增加,這有時(shí)稱為地線反跳(gound bounce)。

3. IRDrop對(duì)性能(timing)的影響

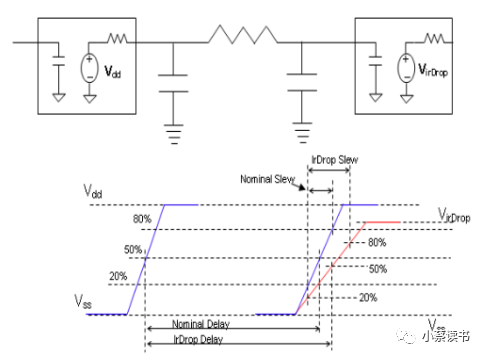

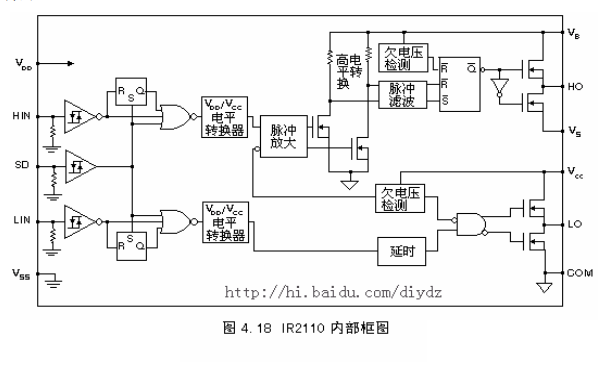

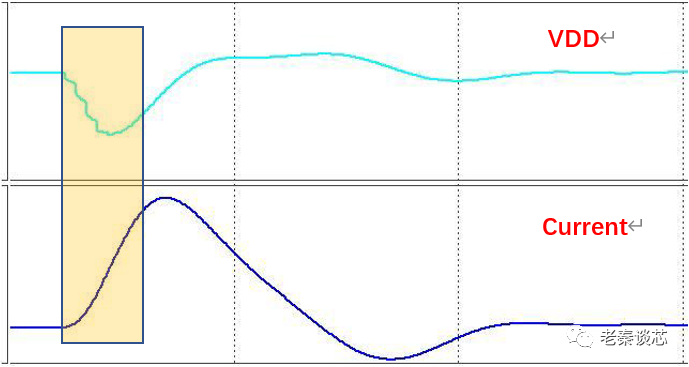

IR Drop可以影響net delay和cell delay。由于峰值電壓的減小,有IR Drop的instance的電壓擺幅會(huì)小于標(biāo)準(zhǔn)電壓。這會(huì)影響接收器的net delay和input slew(如下圖)。

假設(shè)driver工作在正常電壓Vdd,receiver工作在Virdrop電壓。由于cell delay是inputslew和outputload的函數(shù),所以IR drop也會(huì)影響cell delay。除此之外,電壓的降低也會(huì)影響cell delay。

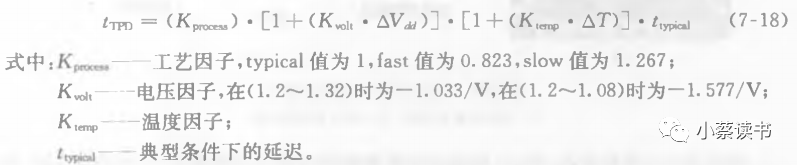

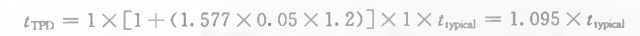

以SIMIC 0.13um工藝為例,總延遲的計(jì)算公式如下:

從公式中可以看出,當(dāng)電壓降為5%時(shí),延遲值如下所示,也即延遲增加9.5%。

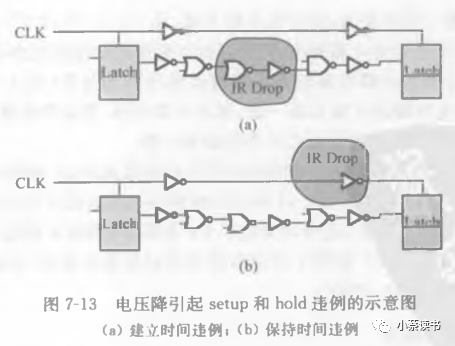

net delay和cell delay的增加會(huì)造成時(shí)序違例的產(chǎn)生,它可以引起setup和hold違例。如果電壓降或延遲位于數(shù)據(jù)路徑,他可能產(chǎn)生setup違例;如果電壓降或延遲是位于時(shí)鐘路徑,它可能會(huì)產(chǎn)生hold的違例。

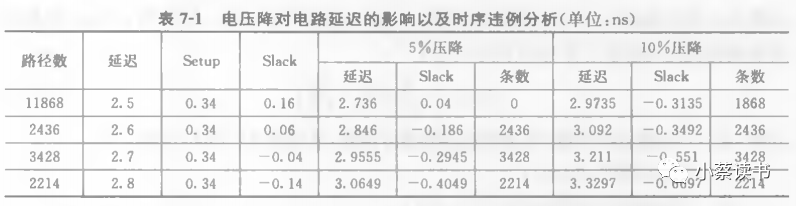

如下面某個(gè)設(shè)計(jì),其時(shí)鐘周期為3ns,則電壓降產(chǎn)生的時(shí)序違例分析如下表所示:

這個(gè)設(shè)計(jì)在沒有電壓降時(shí),其工作主頻可以達(dá)到318MHz,在5%電壓降時(shí)主頻為294MHz,如果有10%的電壓降,則主頻只有272MHz.可見在高頻數(shù)字電路中,降低電壓降對(duì)于提高芯片的性能有著至關(guān)重要的作用。

4.IR Drop對(duì)芯片功能的影響

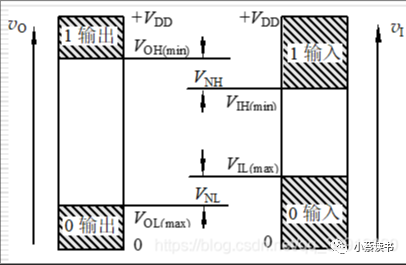

小編是不是搞錯(cuò)了?這玩意還能影響到功能。應(yīng)該沒有搞錯(cuò),IR Drop損害了邏輯門的噪聲容限,這不僅是因?yàn)殡娫淳W(wǎng)格的電壓降低,而且也因?yàn)榈鼐€網(wǎng)格的電壓升高。一旦噪聲容限降到預(yù)算值(典型值為10%)之下,設(shè)計(jì)就不保證正確工作了。近年來,電源電壓一直降低,以避免晶體管的穿通條件、熱電子效應(yīng)和器件擊穿。更近年來的情況是,VDD的降低主要是為了減小功耗而不是其他問題。無論那種情況都導(dǎo)致了越來越小的噪聲容限。由于有IR壓降,噪聲容限更進(jìn)一步降低,使得在百萬晶體管級(jí)的設(shè)計(jì)中處理連線耦合噪聲效應(yīng)變得更加困難。

審核編輯:湯梓紅

-

芯片

+關(guān)注

關(guān)注

459文章

51808瀏覽量

431813 -

模塊

+關(guān)注

關(guān)注

7文章

2763瀏覽量

48646 -

緩沖器

+關(guān)注

關(guān)注

6文章

2012瀏覽量

46161 -

封裝

+關(guān)注

關(guān)注

128文章

8248瀏覽量

144206 -

仿真

+關(guān)注

關(guān)注

50文章

4187瀏覽量

134894

原文標(biāo)題:IR Drop 對(duì)芯片性能及功能的影響

文章出處:【微信號(hào):處芯積律,微信公眾號(hào):處芯積律】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

談?wù)?b class='flag-5'>芯片設(shè)計(jì)中的IR-drop

什么是DC IR Drop?DC IR Drop仿真有何意義?

智能ODN功能及性能剖析

驅(qū)動(dòng)芯片IR2110的數(shù)據(jù)和功能及應(yīng)用簡介

IR Drop與封裝分析

Sigrity PowerDC是如何計(jì)算IR Drop Margin?

IR Drop對(duì)芯片性能及功能的影響

IR Drop與封裝(一)

SoC設(shè)計(jì)之功耗—IR drop

評(píng)論