前言:講解說明,因?yàn)楸救斯緦?duì)24V降壓5V有兩個(gè)方案,其主要原因降成本需求

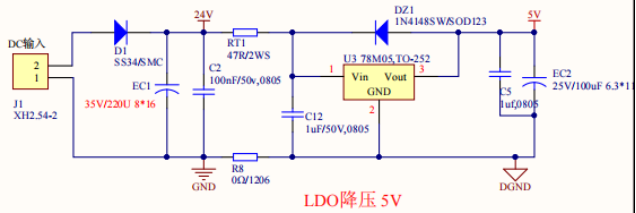

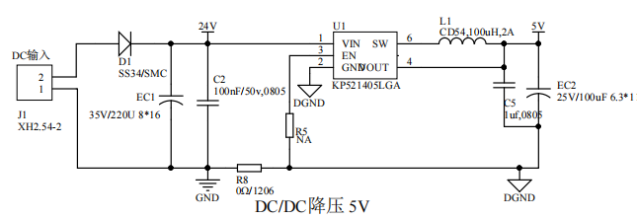

先看設(shè)計(jì)的原理圖

LDO降壓

dc/dc降壓

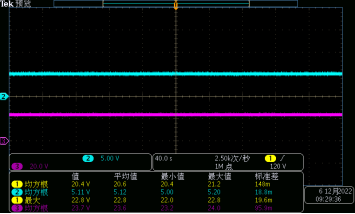

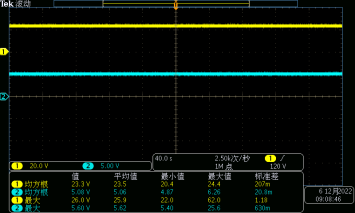

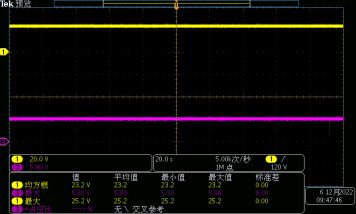

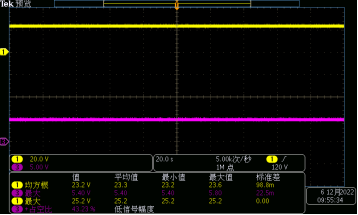

首先對(duì)于兩者電壓的輸入端和輸出端測(cè)量電壓是否平穩(wěn),如果波動(dòng)那就沒什么意義了。如下圖示波器測(cè)量所得:

空載下dc/dc

空載下LDO

負(fù)載下dc/dc

負(fù)載下LDO

可見輸入輸出都很穩(wěn)定,且空載和負(fù)載條件下也很平穩(wěn)。

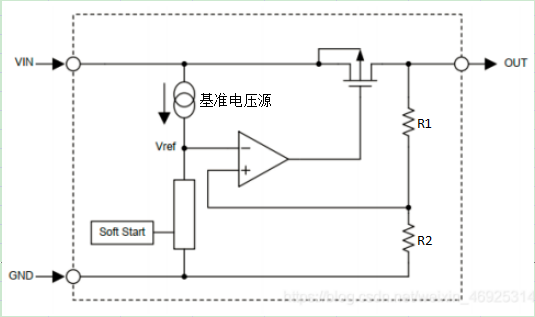

LDO的降壓原理

內(nèi)部邏輯圖

LDO內(nèi)部主要是基準(zhǔn)參考電壓、誤差放大器、分壓取樣電路和MOS管調(diào)整電路。

首先分壓取樣電路三個(gè)電阻分壓對(duì)輸出電壓進(jìn)行采集,誤差放大電路將采集的電壓輸入到誤差放大器的反向輸入端,與正向輸入端的基準(zhǔn)電壓(也就是期望輸出的電壓)進(jìn)行比較,再將比較結(jié)果進(jìn)行放大。MOS管調(diào)整電路把這個(gè)放大后的信號(hào)輸出到MOS管的柵極,從而這個(gè)放大后的信號(hào)(電流)就可以控制MOS管的導(dǎo)通電壓了,這就是一個(gè)負(fù)反饋調(diào)節(jié)回路。 MOS管輸出電壓就是輸入電壓減去導(dǎo)通電壓,因此控制了導(dǎo)通電壓就相當(dāng)于控制了LDO的輸出電壓了。當(dāng)輸出電壓與基準(zhǔn)電壓相差較大的時(shí)候,比較器輸出信號(hào)變強(qiáng),從而MOS管壓降變小,輸出電壓變小,從而基準(zhǔn)電壓與輸出電壓變得更加接近。從LDO工作原理我們可以得知,LDO只能降壓。

LDO的特點(diǎn)

1.LDO在使用的時(shí)候,非常方便,除了輸入、輸出端加上濾波電容,不需要其他外圍器件,而一般的DCDC模塊在使用時(shí)要電感、電容、二極管等外圍器件組合,且布局也需要特別講究,否則使用效果不盡人意。LDO芯片一般都比較便宜,且不需要很多外圍器件,非常適合低成本方案。

2.使用LDO時(shí),需注意輸入電壓與輸出電壓差不能太大,否則效率會(huì)非常低。LDO效率η=(Vin-Vout)/Vin,比如輸入電壓Vin為24V,輸出電壓Vout3.3V,計(jì)算得出效率η=13.75%,效率很低。所以使用LDO時(shí),盡量控制輸入輸出電壓差。

插入:

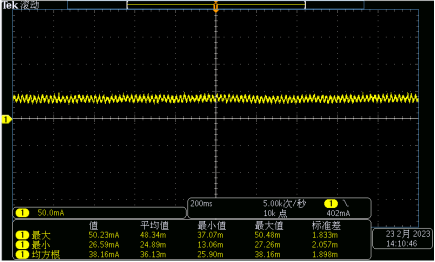

LDO輸出端電流

LDO效率η=Vout/Vin,輸入電壓Vin為24V,輸出電壓Vout為5V,計(jì)算得 出效率η=20.83%

3.因?yàn)槠湓頌榫€性調(diào)節(jié)方式,所以不會(huì)產(chǎn)生開關(guān)噪聲,同時(shí)電路紋波也很小,LDO重要參數(shù)之一也是巨大優(yōu)點(diǎn)之一便是紋波小,即PSRR好,PSRR是電源抑制比,是LDO對(duì)輸入電源紋波的抑制程度,PSRR的絕對(duì)值絕越大越好。看PSRR曲線有個(gè)轉(zhuǎn)折點(diǎn),左邊為L(zhǎng)DO自身起主導(dǎo)作用,右邊為輸出電容起主導(dǎo)作用自,PSRR性能好的LDO左邊的曲線會(huì)更高,加大輸出電容,右邊的曲線會(huì)升高。。

LDO選型需考慮的重要參數(shù)

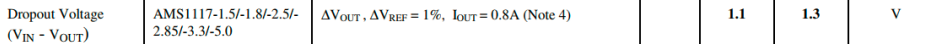

1.壓降Dropout Voltage

我們?cè)谶x型LDO時(shí),除了考慮輸入輸出電壓的范圍,還要考慮LDO本身存在壓降,這個(gè)是由LDO本身結(jié)構(gòu)(MOS管存在導(dǎo)通電阻)導(dǎo)致,這個(gè)參數(shù)我們很多設(shè)計(jì)人員都會(huì)忽略,最后就會(huì)導(dǎo)致電路工作不正常。比如我們常用的AMS1117-3.3,這個(gè)LDO最高可以輸入15V,輸出3.3V,假設(shè)我們的輸入電壓為4.2V,乍一看輸入電壓在手冊(cè)規(guī)定范圍內(nèi),同時(shí)也高于輸出,應(yīng)該是可以使用的。但是實(shí)際使用時(shí),卻發(fā)現(xiàn)輸出電壓沒有3.3V,大概在2.7V-2.9V左右,這就是設(shè)計(jì)時(shí)忽略的LDO本身存在的壓降。

AMS1117的壓降一般1.1V,最大1.3V,因?yàn)閴航颠€和電流、溫度有關(guān)系,所以推薦輸入電壓-輸出電壓≥1.5V,才可以保證電路穩(wěn)定。

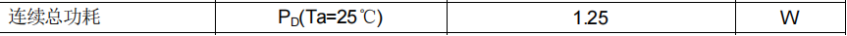

2.最大耗散功率Power Dissipation

LDO的耗散功率P=(Vin-Vout)*Iout,假設(shè)輸入電壓Vin24V,輸出電壓Vout3.3V,輸出電流Iout30mA,那LDO的耗散功率P=0.651W,這個(gè)功耗全部是通過熱量損耗了,所以不推薦LDO用于輸入輸出壓差過大,大輸出電流的場(chǎng)景。

如果實(shí)在需要使用的話,我們就要考慮LDO芯片能承受多大的功耗了,我們以78M05為例,下圖為其不同封裝的最大耗散功率,這個(gè)最大耗散功率就是這個(gè)芯片能承受最大的熱功耗,超過就會(huì)燒壞。

根據(jù)計(jì)算我產(chǎn)品上LDO的最大耗散功率0.72W,在規(guī)格書內(nèi),可以采用。

插入:LDO的耗散功率P=(Vin-Vout)*Iout,假設(shè)輸入電壓Vin24V,輸出電壓Vout5V,輸出電流Iout為38.16mA,那LDO的耗散功率P=0.72W

總結(jié),對(duì)于我產(chǎn)品來(lái)說,主要為了降成本,LDO符合采用標(biāo)準(zhǔn)。另一方面。輸入和輸出差值太大,從功耗和效率上來(lái)講不易采納;差值也不能太小,也要考慮到壓降,這樣可以更好地利用LDO。DCDC的降壓大家應(yīng)該都很好理解,主要是利用斬波,不多介紹。

Thanks!

審核編輯黃宇

-

芯片

+關(guān)注

關(guān)注

459文章

51893瀏覽量

433296 -

電路

+關(guān)注

關(guān)注

173文章

6009瀏覽量

174100 -

ldo

+關(guān)注

關(guān)注

35文章

2232瀏覽量

155279

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

DC-DC 和LDO 簡(jiǎn)單介紹

DC/DC和LDO的區(qū)別

LDO和DC/DC,那個(gè)更強(qiáng)?

DC/DC和LDO的區(qū)別是什么

DC/DC和LDO區(qū)別及選型

如何選擇合適的DC-DC、LDO器件?

DC/DC和LDO有哪些不同之處呢

DC/DC與LDO各自的主要特點(diǎn)

LDO與DC/DC參數(shù)選型描述

LDO和DC-DC有什么不同?

淺談LDO和DC/DC電源的區(qū)別

LDO與DC-DC

評(píng)論