當熱插拔控制器的輸出短路時,內(nèi)部斷路器功能跳閘以斷開電路。但在內(nèi)部斷路器響應(yīng)之前,初始電流可能為幾百安培。典型的熱插拔控制器斷路器延遲時間可能為200–400ns,由于柵極下拉電流有限,柵極關(guān)斷時間可能為10-50微秒。同時,高短路電流流動。

應(yīng)用筆記中描述的簡單外部電路可以最大限度地減小初始電流尖峰,并在200–500ns內(nèi)終止短路。

典型熱插拔電路

我們來看一個使用MAX12的典型+6V 4272A熱插拔控制電路(圖1)。檢查MAX4272規(guī)格,可以看到它包含慢速和快速比較器,跳變門限分別為50mV和200mV(在整個溫度范圍內(nèi)容差為43.5–56mV和180–220mV)。應(yīng)用通常放置在工作電流與跳閘電流比上的 1.5–2.0 乘數(shù),我們選擇 R意義= 5mΩ。允許 R 的容差為 5%意義,對于過載條件下,慢速比較器的跳變電流范圍為8.28–11.76A,當發(fā)生短路時,快速比較器的跳變電流范圍為34–46.2A。

圖1.典型的熱插拔控制器電路。

最小慢比較器跳變點比正常工作電流高38%,快速跳閘門限適合工作電流6-8倍的短路跳閘。

350ns快速比較器延遲意味著初始短路電流尖峰僅受該期間的電路電阻限制。此后,電流緩慢減小,因為 3mA 柵極下拉電流限制了 MOSFET M1 的 3–4nF 柵極電容放電速率,直到短路完全中斷。當柵極從15V拉至近地電位時,短路電流在40–19μs內(nèi)緩慢減小。

峰值短路電流

初始350ns期間的峰值電流取決于:

(a) 源ESR,(b)短路質(zhì)量,(c)RSENSE的值,(d)M1的RDS(ON),以及(e)M1的ID(ON)。

將近似的最佳情況實用值分配給這些值,我們的總短路電阻為

(源ESR≈4 mΩ)+(短路≈3 mΩ)-(RSENSE,5 mΩ)=(RD(ON)≈4米Ω)≈16米Ω。

這可能會產(chǎn)生短暫的峰值ISC≈750A,這取決于電源的儲能容量(750A將使具有2200μF電容器的低ESR背板在1μs內(nèi)僅放電340mV)。在這種情況下,實際峰值ISC可能會被M1的ID(ON)限制在≈400A。

ID(ON)取決于VGS,因此在此期間檢查電路以確定柵極-源極電壓是有指導(dǎo)意義的。MAX4272包含一個內(nèi)部電荷泵,可將工作柵極電壓設(shè)置在VIN以上約7V。因此,當MOS導(dǎo)通時,VGS為7V。

做空的第二個影響是它實際上增加了VGS。考慮短路使電壓階躍等于M1的漏極-源極兩端的全部輸入電壓的一部分。由于M1的RD(ON)約為估計的總短路電阻的1/3,因此施加≈12V階躍的1/3作為VDS。通過從漏極到柵極的cdg和從柵極到源極的cgs的分壓器作用,該步驟部分地轉(zhuǎn)移到柵極。適當?shù)挠嬎惚砻鳎擃~外的VGS為300–500mV,但在短路條件下進行的測量表明,其可能高達VGS=+3V。

到目前為止,可能很明顯,高質(zhì)量的短路會導(dǎo)致幾百安培的流動幾微秒到幾十微秒。

我們可能希望在50μs<將峰值Isc限制在1A,但如果不增加一個非常快速的比較器和柵極下拉電路,這是不切實際的。但是,我們可以考慮一些簡單的電路修改。

我們可以通過添加一個簡單的外部電路來加速柵極放電,同時電流被I限制,從而將短路周期限制在≤1/2μs。D(開)內(nèi)部快速比較器的前 350ns 響應(yīng)時間為幾百安培,或

我們可以使用稍微復(fù)雜的外部電路將峰值Isc限制在100A范圍內(nèi)的某個位置,持續(xù)時間≤200ns。

快速柵極下拉電路可限制高短路電流的持續(xù)時間

只需添加PNP達林頓晶體管Q1,即可最大限度地縮短大電流短路電流的持續(xù)時間,如圖2所示。二極管D1允許柵極在導(dǎo)通時正常充電,但控制器的3mA柵極放電電流在關(guān)斷時重定向到Q1的基極。然后,Q1在≈100ns內(nèi)對柵極快速放電。因此,短路的高電流部分被限制在僅略高于350ns快速比較器延遲時間。

圖2.具有快速柵極下拉功能的熱插拔控制器。

快速限流電路

短路電流可限制在≈100A,持續(xù)<200ns,電路如圖3所示。PNP晶體管Q1a-當電壓過R時觸發(fā)意義達到≈600mV - 驅(qū)動NPN晶體管Q1b快速放電M1的柵極電容。

圖3.具有快速短路峰值電流限制功能的熱插拔控制器。

C2放置在M1柵極至源極兩端,以進一步降低短路期間施加到柵極的正瞬態(tài)階躍電壓;其值可能在 10nF 到 100nF 之間。

增加齊納二極管D1以限制V一般事務(wù)人員低于MAX7提供的4272V電壓。

雖然齊納二極管在偏置在5mA時額定電壓為1.5V,但它會限制V一般事務(wù)人員本電路的柵極充電(齊納偏置)電流僅為≈3.4V,因為MAX100僅提供4272μA柵極充電(齊納偏置)電流。限量V一般事務(wù)人員降低 ID(開)- 以 R 為代價D(開),因為數(shù)據(jù)手冊顯示 5.3V 時為 4mΩ,3V 時為 7mΩ,并允許更快地關(guān)斷 M1。

齊納D1和電容C2也可以在圖1和圖2的電路中發(fā)揮一些優(yōu)勢,以減少ID(開)在短路期間。

測試方法 - 產(chǎn)生短路

還有什么比制造短路更簡單的呢?每輛英國跑車中至少有一個。

但是,具有足夠質(zhì)量和可重復(fù)性的短路用于測試則更具挑戰(zhàn)性。為該實驗評估了幾種產(chǎn)生短路的方法。

機械開關(guān)總是在幾毫秒的時間內(nèi)產(chǎn)生彈跳觸點閉合。旋轉(zhuǎn)多葉開關(guān)似乎具有一定的前景,但由于幾個大電流閉合產(chǎn)生的電弧,觸點被侵蝕,人們想知道可重復(fù)性。

大電流繼電器觸點也會產(chǎn)生彈跳觸點閉合,并在閉合過程中表現(xiàn)出可變的接觸電阻。

評估的可控硅整流器的電流上升率不太令人滿意。

大電流汞置換繼電器被認為是最佳方法,但結(jié)果并不令人滿意。發(fā)現(xiàn)具有指定電阻為 60mΩ 的 600A 4V 汞繼電器在觸點啟動時的初始電阻為 40mΩ,隨著電流脈沖的進展,在 4μs 的時間內(nèi)悠閑地松弛至 15mΩ。

手動操作短路連桿可提供隨意、間歇且不可重復(fù)的接觸 - 也許最接近英國跑車的理想!但是,可以實現(xiàn)非常陡峭的電流波前。最后,這是最有效(也是最經(jīng)濟)的方法,盡管接觸侵蝕限制了具有可重復(fù)結(jié)果的閉合次數(shù)。

最有前途的實驗室質(zhì)量方法是使用由多個高輸出CMOS施密特線驅(qū)動器驅(qū)動的多個并行布線低RD(ON)NMOS晶體管。由于時間和資源有限,沒有采用這條路線。

具有陡峭電流波前的真正的低電阻短路在實驗室中通過機械手段難以持續(xù)產(chǎn)生。幾乎可以肯定的是,在工作電路中會出現(xiàn)意外短路。

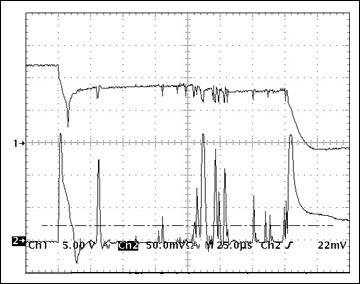

典型的手動短路會產(chǎn)生電容放電電流和電壓波形,如圖4所示。記錄5V/div.短路輸出電壓的上部曲線顯示,電容在大部分時間標度(25μs/div.)內(nèi)放電不到一半。下方記錄25A/div.短路電流的曲線清楚地顯示了觸點的間歇性。

圖4.參差不齊的機械短路波形。

創(chuàng)建ESR低于5mΩ的電源也不容易。然而,為了創(chuàng)建一個4–5mΩ的低ESR電壓源,仔細測量顯示440A短路期間的壓降為100mV,花費了大量精力。該電壓源采用一個 5500μF 計算機級電解電容器、一個 3.3μF 多層陶瓷電容器和六個 100μF 特種聚合物鋁電解電容器并聯(lián),直接安裝在由 10A 電源驅(qū)動的電路輸入端。

短路電流波形

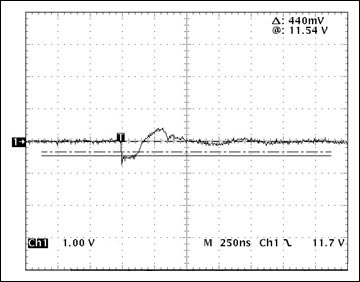

圖1的未改變電路表現(xiàn)出短路電流波形,如圖5所示。波形看起來是反轉(zhuǎn)的,因為測量是檢流電阻RS兩端的電壓,示波器在測試電路的+12V輸入端接地。RS為6mΩ,電壓標度為1V/格,峰值電壓為2400mV或400A。當前的波前并不像接觸更好的那樣陡峭。

圖5.400A 未改變電路中的峰值短路電流波形。

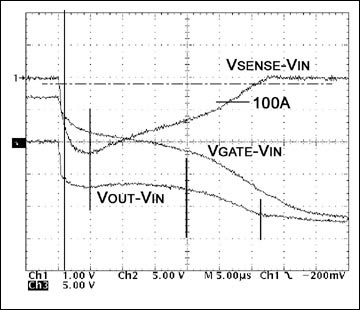

查看圖6的電壓波形也很有啟發(fā)性,其中短柵極和M1柵極電壓波形的輸出電壓與RS兩端的電壓相結(jié)合。所有電壓均以+12V輸入為基準。

圖6.未改變電路中的短路電壓和電流波形。

VOUT-VIN波形顯示,VOUT在短路期間下降7V,表明短路電阻僅略小于總電路電阻的?。較低電阻的短路可能會產(chǎn)生高于400A的峰值電流。相同的波形表明,在最初的300ns期間,短路不是完全有效的;這有助于緩慢下降的VSENSE波形。

VGATE波形顯示初始VGS E7V,由于VOUT下降,在1μs時增加到近10V。Vgs在5μs時僅降至9V,在20μs時降至6V,在33μs時跌至4V。柵極的緩慢放電是由于只有3mA的放電電流可用。因此,在短路開始后的27μs下,短路電流仍為100A。

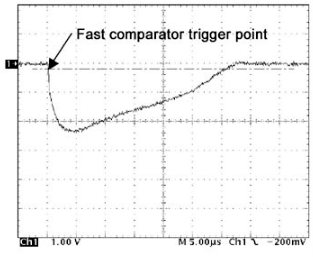

圖2的快速柵極下拉電路可能不會降低初始短路電流,但PNP達林頓下拉電路會快速終止電流波形。圖7所示的這種配置的短路電流波形仍表現(xiàn)出2400mV或400A的峰值電流,但在快速比較器觸發(fā)≈50ns后,電流在370ns內(nèi)終止。另請注意,短路電流波形非常陡峭,表明機械短路引發(fā)極佳。

圖7.快速下拉電路中的短路電流波形。

當電路電容對輸入電容進行再充電時,源電流反轉(zhuǎn),在+12V輸入端產(chǎn)生輕微的正過沖。

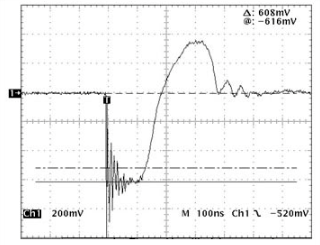

圖3所示的快速短路峰值電流限制電路可有效限制峰值電流和短路引起的電流持續(xù)時間。圖8所示RS兩端記錄的電壓在600mΩ中峰值約為100mV或6A。短路電流終止非常迅速,電流脈沖在 200ns <完全終止。

圖8.改進的熱插拔控制器電路中的短路電流脈沖。

如圖9所示,該技術(shù)將背板電源干擾降至最低,其中測試方法部分描述的+500V電源上的峰值電壓干擾為< ±12mV。

圖9.圖3所示電路短路引起的背板干擾。

請注意,陡峭的電流波前再次表明非常高質(zhì)量的短路引發(fā)。不幸的是,要復(fù)制這種陡峭的短路波形并不容易。

然后會發(fā)生什么?

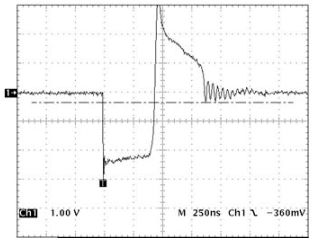

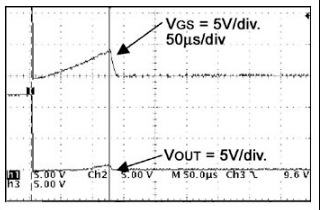

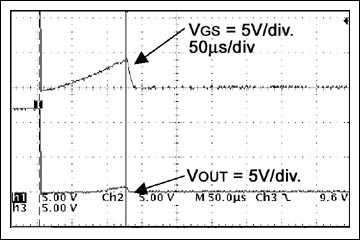

PNP-NPN檢測/下拉電路快速中斷短路電流(然后斷開),以至于MAX4272快速比較器沒有足夠的時間觸發(fā)(響應(yīng)時間350ns)。圖10顯示了500μs周期(短路啟動后450μs)內(nèi)的VGS波形。由于100μA的柵極充電電流仍然有效,已放電的柵極開始上升。大約130μs后,柵極充分增強(3V),VOUT上升到大約1V,短路電流再次開始流動。充電足夠慢,以至于快速比較器在33A(200mV/6mΩ)時觸發(fā),IC通過關(guān)閉和鎖存OFF來執(zhí)行其工作。

圖 10.V 的壓縮時間視圖一般事務(wù)人員在短路條件下。

總結(jié)

所討論的兩個電路中的任何一個都將通過最小化熱插拔控制電路短路時的能量耗散來保護背板電源。圖2中更簡單的電路大大縮短了短路電流流向略小于500ns的周期,而圖3中稍微復(fù)雜的電路將峰值短路電流降低到100A,并將脈沖寬度截斷到200ns以下。

這兩種技術(shù)都可以應(yīng)用于大多數(shù)熱插拔控制器電路。

個別測試結(jié)果將根據(jù)電源的阻抗、短路的阻抗,尤其是短路本身的質(zhì)量和攻擊時間而有所不同。

審核編輯:郭婷

-

控制器

+關(guān)注

關(guān)注

114文章

16827瀏覽量

182167 -

比較器

+關(guān)注

關(guān)注

14文章

1796瀏覽量

108209 -

熱插拔

+關(guān)注

關(guān)注

2文章

227瀏覽量

38051

發(fā)布評論請先 登錄

相關(guān)推薦

你知道熱插拔時的短路電流危害有多大嗎?

降低熱插拔控制電路的電路電流

降低熱插拔控制電路的電路電流

降低熱插拔控制電路的電路電流

熱插拔控制器構(gòu)成限流電路

什么是脈沖寬度_脈沖寬度是什么意思

為什么工程機械控制器需要脈沖寬度調(diào)制功能

脈沖寬度調(diào)制(PWM):工程機械控制器的常見技術(shù)

評論