觸發器使用中的幾個問題

觸發器邏輯功能的轉換

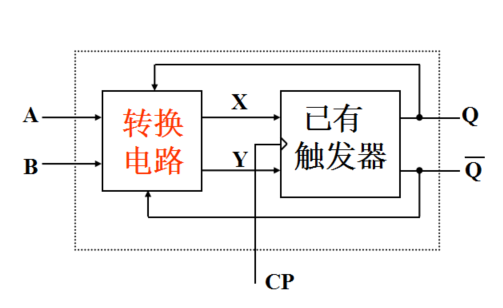

觸發器邏輯功能轉換示意圖:

將已有觸發器轉換為所需觸發器的功能,實際上是求轉換電路,即求轉換電路的函數表達式:

代數法

通過比較已有觸發器和待求觸發器的特性方程, 求轉換電路的函數表達式.

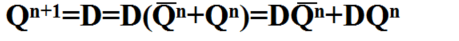

例: 把JK觸發器轉換為D觸發器.

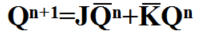

解: 已有JK觸發器的特性方程為:

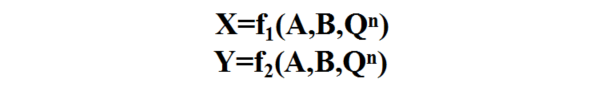

待求D觸發器的特性方程為:

為求出轉換電路的函數表達式,可將D觸發器的特性方程轉換為:

比較JK觸發器的特性方程,可得:

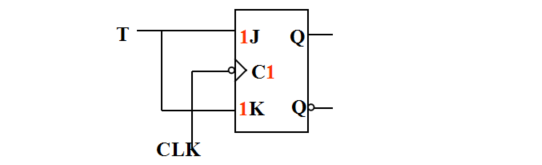

例: 將JK觸發器轉換為T觸發器.

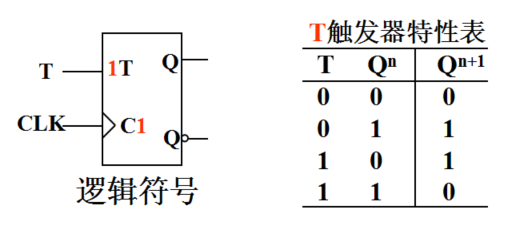

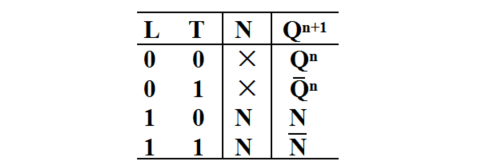

T觸發器的特性

歸納為:

T=0 保持

T=1 翻轉

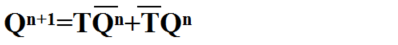

T觸發器的特性方程:

將上式和JK觸發器特性方程

比較,可得 J=K=T

注意:在這個電路中,由于采用的是下降邊沿JK觸發器,所以得到的T觸發器也是下降邊沿的。

圖表法

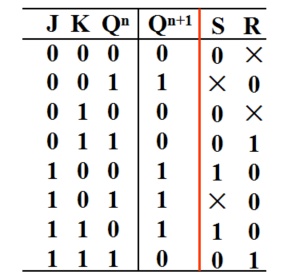

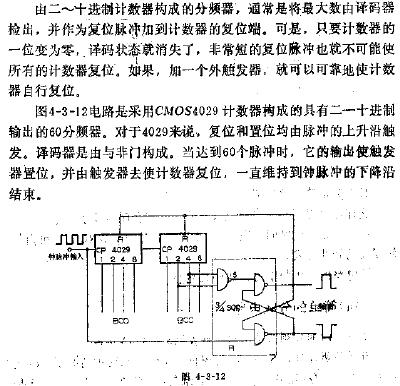

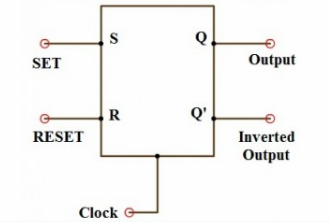

例: 把RS觸發器轉換為JK觸發器.

① 首先列出JK觸發器的特性表;

② 根據RS觸發器的特性,列出當滿足JK觸發器特性時S、R端應加的信號;

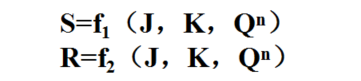

③ 寫出下列兩個表達式:

轉換電路圖

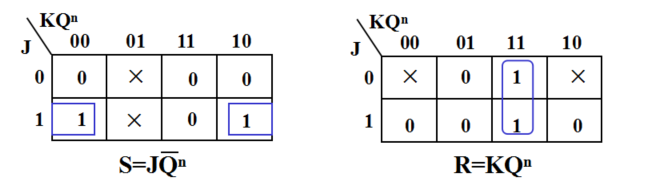

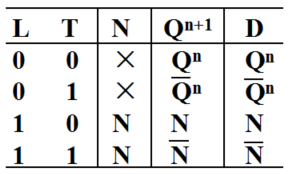

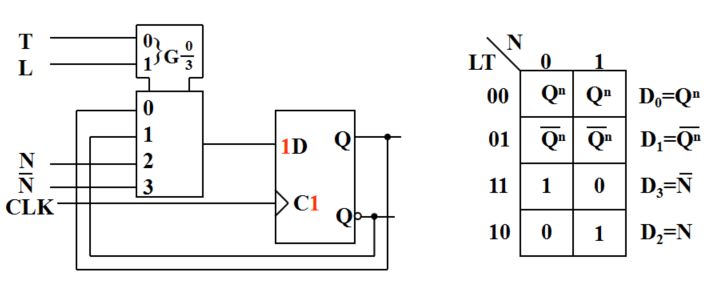

例:試用D觸發器和四選一MUX構成一個多功能觸 發器,其功能如下表所示。 表中L、T為控制變量,N為數據輸入變量。

解:① 列表;

② 設L、T為MUX的地址 變量,求MUX的數據端輸入信號;

③ 畫邏輯圖。

觸發器的脈沖工作特性

觸發器的脈沖工作特性:

指為了保證觸發器可靠的動作,而對時鐘脈沖、輸入信號以及它們之間的時間關系所提出的要求。

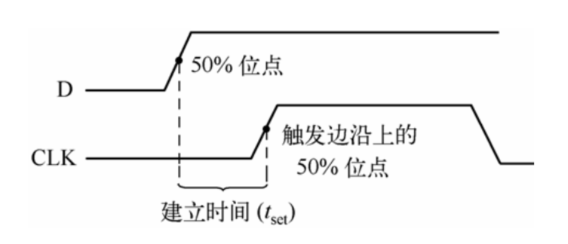

輸入信號的建立時間和保持時間

(1)建立時間

為使觸發器做好觸發準備,要求輸入信號在時鐘脈沖的邊沿到來之前,提前一段時間到來,提前的這段時間叫建立時間,用t_set表示。

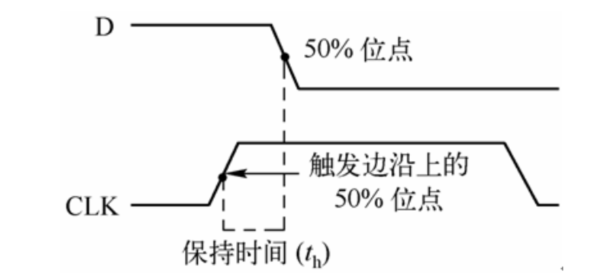

(2)保持時間

為了保證觸發器可靠翻轉,在時鐘脈沖到達后,輸入信號必須維持一段時間不變。 這段時間稱為保持時間,用t_h表示。

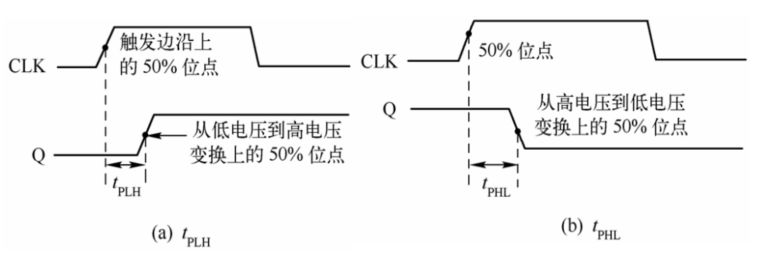

觸發器的傳輸延遲時間

從時鐘脈沖邊沿到達到觸發器的新狀態穩定建立起來,所需要的時間叫做傳輸延遲時間。

tPHL表示輸出端由高電平變為低電平的傳輸延遲時間

tPLH表示輸出端由低電平變為高電平的傳輸延遲時間

觸發器的最高時鐘頻率

在保證觸發器可靠翻轉的條件下, 所允許的時鐘頻率有一個上限值 (最高頻率) ,該上限值即為觸發器的最高時鐘頻率,用f_max表示。

脈沖寬度

為保證時序邏輯電路能夠正常穩定地工作,要求輸入信號的脈沖寬度大于最小脈沖寬度(tw)

功耗

數字電路的功耗是指它的總功率消耗,

例:在+5V直流電源上工作的一個D觸發器,如果流經它的電流是5mA,那么功耗就是

P=VCC×ICC=5V×5mA=25mW

假設某數字系統總共需要10個觸發器,并且每一個觸發器都耗用25mW的功率,則總功率需求是

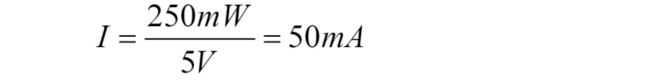

PT=10×25mW=250mW

說明直流電源所需要的輸出容量是250mW。

如果該數字系統也工作在+5V的直流電源上,那么電源必須提供的電流量為

觸發器的合理選用

1.從邏輯功能來選擇觸發器

如果要將輸入信號存入到觸發器中,則選擇 D觸器。

如果需要一個輸入信號,且要求觸發器具有翻轉和保持的功能,則選擇 T 觸發器。

如果只需要翻轉功能,則選用 T’觸發器。

如果需要兩個輸入信號,要求觸發器具有置 0、置 1、保持、翻轉功能,則選用 JK 觸發器。

從電路結構形式來選擇觸發器

如果觸發器只用作寄存一位二值信號,則可以選用門控鎖存器 ,這種器件電路簡單、價格低廉。

如果輸入信號不夠穩定或易受干擾,則選用邊沿觸發器; 可以避免空翻現象的發生,提高電路的可靠性。

從制造工藝來選擇觸發器

TTL觸發器的速度較快。

CMOS 觸發器的優點是功耗低和抗干擾能力強。

觸發器使用的注意事項

(1)集成觸發器中一般都設有異步置 0 和置1端,可以利用它們給觸發器設定初始狀態。

(2)每一片集成觸發器都有且只有一個公共的電源和地,若電路輸入信號 1 則和電源相連,若輸入信號 0 則和地相連。

(3)在使用觸發器時,應當注意其脈沖工作特性,時鐘脈沖輸入和信號輸入在作用時間上要很好地配合,否則就不肯能可靠地工作。

(4)一個集成電路中可能集成了一個或幾個觸發器,它們之間是相互獨立的,可以單獨使用。

-

CMOS

+關注

關注

58文章

5725瀏覽量

235715 -

電路圖

+關注

關注

10350文章

10721瀏覽量

531481 -

轉換電路

+關注

關注

2文章

205瀏覽量

30507 -

RS觸發器

+關注

關注

3文章

101瀏覽量

17995 -

觸發器

+關注

關注

14文章

2000瀏覽量

61228

發布評論請先 登錄

相關推薦

什么是觸發器 觸發器的工作原理及作用

jk觸發器是什么原理_jk觸發器特性表和狀態轉換圖

rs觸發器電路圖與rs觸發器內部電路圖

觸發器使用中的幾個問題

觸發器使用中的幾個問題

評論