高速和低速數據轉換器在現代寬帶移動無線電中發揮著關鍵功能。本應用筆記概述了如何確定基帶采樣無線電架構中的高速數據轉換器性能要求。此外,還概述了在考慮高速模擬前端(AFE)解決方案時的系統分區策略和優勢。

介紹

移動寬帶無線通信系統采用多種技術來提高頻譜效率。為了實現高數據速率、產生最佳系統容量并確保可靠的服務質量 (QoS),現代無線通信系統使用可變信道帶寬(帶寬 = 1.25MHz 至 20MHz)和高階調制(16QAM 至 64QAM)和碼分或正交頻分多址(CDMA、OFDMA)以及可擴展的智能天線技術(例如,多輸入多輸出或 MIMO、空間分集)。

3GPP標準UMTS,TD-SCDMA和長期演進(LTE)以及IEEE 802.16e,IEEE 802.11n和IEEE 802.11ac等其他標準是使用這些技術的一些常見系統。例如,使用 4QAM 調制、具有 100 個子載波的正交頻分復用 (OFDM)、64MHz 信道帶寬和 2048×20 MIMO 架構,2G LTE 無線電可以實現大于 2Mbps 的峰值數據速率和強大的性能。

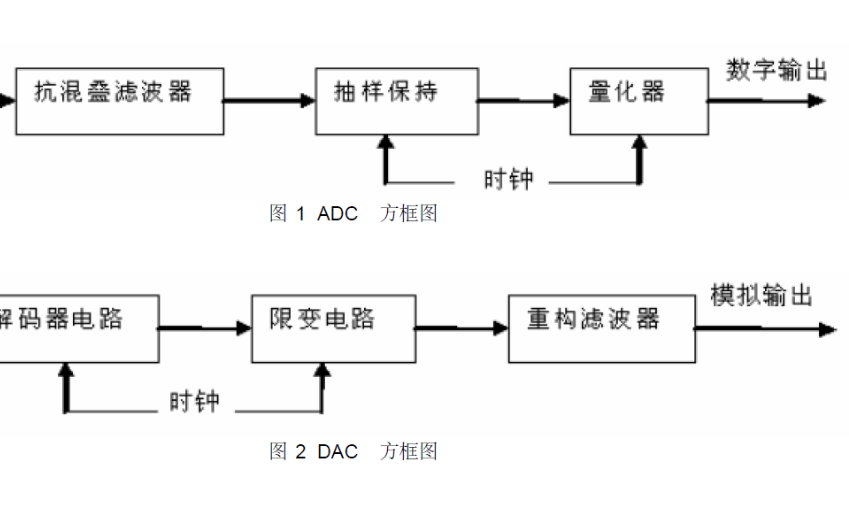

采用 OFDM 的高階調制、寬通道帶寬和 MIMO 架構都要求接收模數轉換器 (Rx ADC) 和發射數模轉換器 (Tx DAC) 具有更高的性能。高速數據轉換器的要求包括更快的采樣速率、更高的動態范圍、改進的頻譜性能和多通道。此外,由于最終產品的通信設備是移動和電池供電的,因此數據轉換器必須低功耗和微型尺寸。在選擇合適的高速數據轉換器解決方案時,這些因素帶來了迷宮般的設計挑戰。以下主題介紹了一種幫助設計人員應對這些挑戰的方法。

無線電和數據轉換器功能

小尺寸、低功耗和低成本是智能手機、數據卡、嵌入式無線電、公共安全無線電、戰術軍用無線電或移動衛星無線電等移動無線產品的重要設計目標。因此,直接變頻零中頻(ZIF)架構是一種常見的無線電解決方案。與外差無線電相比,ZIF 架構消除了多個中頻組件,如 IF 混頻器、VGA、LO 合成器和鏡像抑制濾波器。這種消除降低了成本并減小了尺寸。此外,在具有可變通道帶寬的應用中,如LTE,ZIF架構適用于可編程基帶濾波。

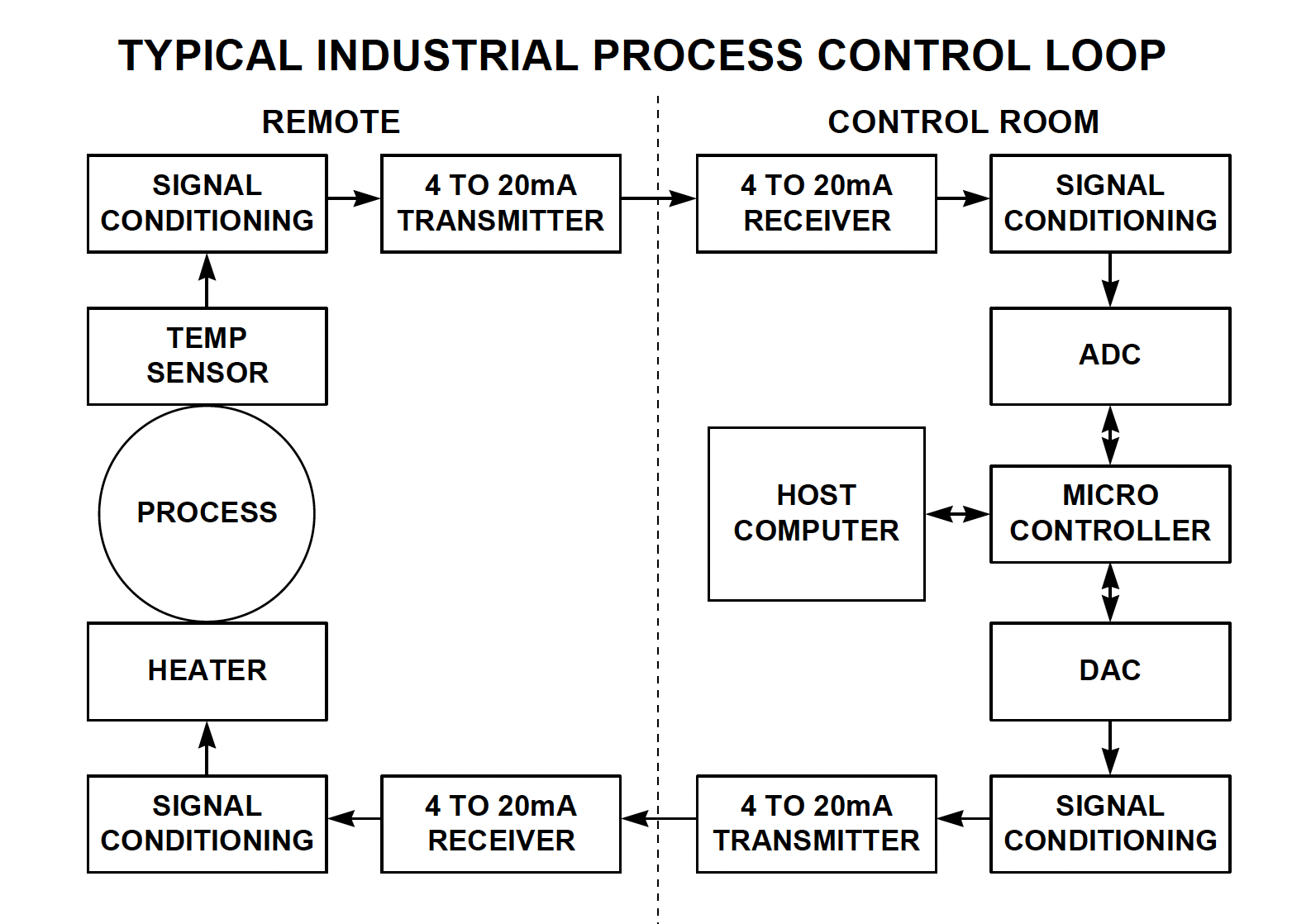

圖1顯示了典型移動應用中使用的無線電陣容。無線電架構、ZIF接收器和準直接變頻發送器需要雙通道高速Rx ADC和雙通道高速Tx DAC,用于同相和正交相位(I/Q)基帶信號采樣和構建。其他低速轉換器用于RF前端增益控制和輔助模擬信號測量,如RF功率放大器溫度和發射器RF功率電平。轉換器的數字總線以現場可編程門陣列 (FPGA)、數字信號處理器 (DSP) 或專用集成電路 (ASIC) 的形式與數字基帶處理器接口。數字基帶處理器執行信號處理功能,如通道編碼、調制映射和數字濾波。如圖1所示,單模無線電可能需要多達<>個數據轉換器通道。

圖1.典型的ZIF無線電基于高度集成的模擬前端芯片。

進入高速模擬前端 (AFE)

如圖1所示,高速轉換器通道和無線電收發器之間的比率為4:1。每增加一個無線電收發器,數據轉換器的密度就會增加四倍。數據轉換器和無線電之間的4:1關系可以在4×4 MIMO設計中看到,其中需要四個無線電收發器和16個高速數據轉換器通道。這使得數據轉換器功能成為密集模擬集成的重要領域,有助于縮小尺寸、降低成本和降低功耗,而這些對于移動無線電設計都至關重要。

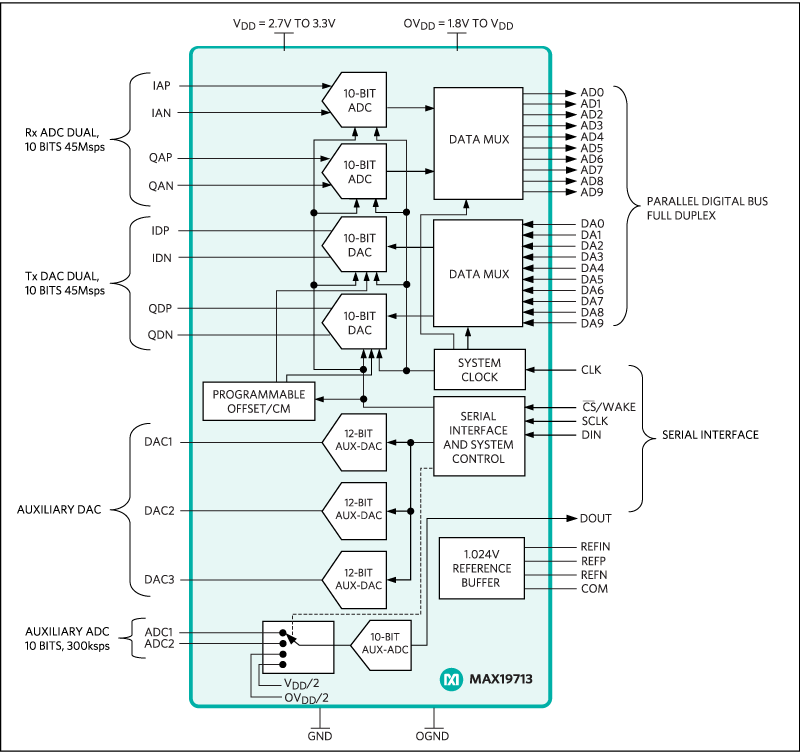

高速和低速數據轉換器可以組合到單個器件中,以滿足移動產品的尺寸、成本和功耗目標。高速AFE可以用作集成轉換器解決方案。MAX19713就是其中一種AFE,如圖2所示。AFE集成了與無線電前端接口所需的所有數據轉換器。

圖2.MAX19713高速AFE框圖

高速AFE在多模設計中具有應用。一個例子是支持UMTS的雙模無線電,采用基于Wi-Fi或MIMO的設計,如LTE、WiMAX和IEEE 802.11n/ac,這需要多個無線電和多個轉換器通道。無線電數據轉換器和射頻收發器之間的 4:1 關系使 AFE 成為基于 FPGA 和基于 DSP 的設計的有吸引力的解決方案。??

由于獨立的DSP和FPGA通常是純數字器件,因此它們不集成混合信號數據轉換器功能。高速AFE可滿足數據轉換器要求,理想情況下,功耗低,占用空間小。AFE 分區的另一個優點是可伸縮性。當給定的設計從 1×1 單輸入單輸出 (SISO) 擴展到 2×2 MIMO 或 4×4 MIMO 時,AFE 可以根據需要用螺栓固定。這樣,數字基帶調制解調器就不必集成多個AFE配置來支持不同的MIMO無線電場景。將轉換器移出數字基帶可優化調制解調器芯片尺寸,降低測試成本并降低硅成本。因此,獨立的 AFE 分區提供了設計靈活性和可擴展性。但是,充分了解系統要求是成功執行 AFE 分區的關鍵因素。

為無線通信系統選擇高速AFE時,必須知道目標空中接口信道帶寬、調制順序和所需的符號錯誤率(SER)。必須識別與無線電前端相關的所有數據轉換器功能。必須確定轉換器成本和功率目標。并且必須了解轉換器的動態性能要求和權衡。

出于幾個原因,了解高速轉換器的性能要求至關重要。轉換器的動態性能主要決定了無線電的性能水平。Rx ADC和Tx DAC必須忠實地數字化和合成接收器和發射器信號,而不會降低系統信噪比(SNR)和SER性能。此外,過度指定轉換器將導致更大的芯片尺寸,從而產生更高功率和更高成本的解決方案。此外,為了最大限度地減小系統尺寸并降低總成本,模擬和數字物理接口必須與相應的無線電前端和數字基帶處理器無縫協作。無縫物理接口消除了電平轉換、增益設置和失調調整所需的外部分立器件。

系統對調制階數、所需 SER、不需要的高干擾電平、雜散發射電平和接入編碼的要求決定了 Rx ADC 和 Tx DAC 動態規格。使用高階調制的信號需要更多的量化電平。通道帶寬決定了轉換器的采樣速率。信號峰均功率比(PAPR)決定動態范圍,系統雜散發射限值決定輸出頻譜純度。

在移動無線終端中,Rx ADC 或 Tx DAC 的分辨率范圍從正交相移鍵控 (QPSK) 中使用的 4 位到 12QAM 中使用的 14 或 256 位,對于 2.5MHz 至 80MHz 通道帶寬,轉換速率可在 1.25Msps 至 40Msps 之間變化。

高速轉換器采樣率

奈奎斯特準則規定轉換器采樣頻率必須至少是目標最高頻率分量的兩倍,否則信息將丟失。例如,在 802.11g 無線局域網 (WLAN) 無線電中,信道帶寬為 16.25MHz。在基帶上,I/Q頻率分量均為8.125MHz。因此,從理論上講,Rx ADC和Tx DAC的采樣速率必須至少為16.25Msps (FCLK = 16.25MHz)。

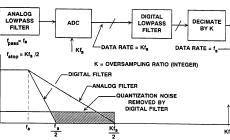

該采樣速率需要一個“磚墻”(即高階)濾波器來衰減帶外頻率分量,以防止Rx ADC混疊或DAC發射路徑中的雜散發射。當采樣速率增加四倍或八倍時,基帶I/Q濾波器階數要求可以放寬,因為混疊和鏡像頻率被移動到第一奈奎斯特區域之外。

此外,通過增加FCLK,可以最大限度地減少由Tx DAC sin(x)/x響應引起的衰減。歸一化Tx DAC輸出幅度由下式給出:

AOUT = sin (πfOUT/fC) × (πfOUT/fC)-1

fOUT = 輸出頻率

fC = 時鐘頻率

歸一化輸出幅度方程表明,對于f外= FCLK/8,sin(x)/x 衰減降低到 0.22dB。工藝增益是過采樣的另一個好處,因為轉換器SNR提高了3dB,FCLK增加了兩倍。

隨著空口通道帶寬的增加,數據轉換器的采樣速率必須提高。需要至少2倍的過采樣率,以降低基帶濾波器要求,提高SNR,并最大限度地減少sin(x)/x效應。為了滿足覆蓋4.1MHz至4MHz的20G可變通道帶寬,高速數據轉換器應至少具有2倍過采樣率,范圍為2.8Msps至40Msps。

Rx ADC:多少位?

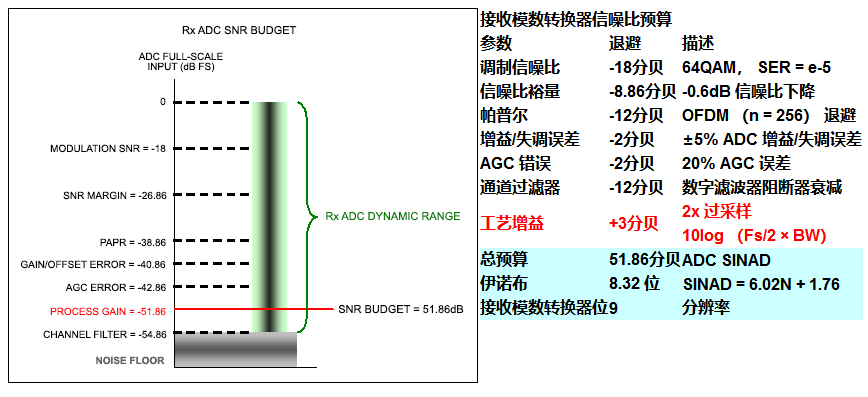

Rx ADC動態性能要求可以使用圖3中的示例Rx ADC SNR預算分析來計算。分析確定可靠的信號恢復所需的Rx ADC動態范圍。在基帶采樣應用中,重要的ADC參數是信噪比和失真(SINAD),它轉化為有效位數(ENOB)。以 ENOB 表示的動態性能(而不是以位為單位的絕對分辨率)是關鍵參數。ENOB和SINAD通過以下等式相關:

| 過程增益 | |

|

|

| SINAD = | 6.02n + 1.76dB + 10log10fS/(2 × BW) |

| n = 有效位數 | |

| fS= 采樣頻率 | |

| 帶寬 = 信號帶寬 | |

SINAD參數考慮了奈奎斯特頻帶內的噪聲和失真,以及過采樣引起的過程增益。選擇RF前端靈敏度、噪聲系數和濾波,以滿足所需SER的基帶解調信號處理要求。Rx ADC的主要工作是量化ZIF接收器的模擬I/Q輸出信號,而不會顯著降低SNR。此外,Rx ADC不會引入抑制可靠信號恢復的失真。

圖3中的分析使用64QAM調制和OFDM,通道帶寬= 5MHz和1e-5 SER,并考慮了ADC SNR下降、ADC增益/失調誤差和RF前端自動增益控制(AGC)誤差。該分析適用于任何空中接口標準,包括LTE、高速分組接入(HSPA)和802.11a/b/g/n/ac。

圖3.RX ADC SNR 預算顯示了不同系統方面對總動態范圍要求的影響。

接收ADC SNR預算涉及幾個因素:

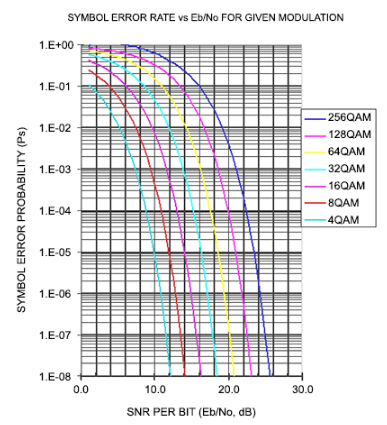

調制信噪比:對于SER = 64e-1的5QAM調制,數字解調器需要18dB SNR。這是基于已知的符號誤差概率理論(圖 4)。

信噪比裕量:由于ADC具有內部噪聲源,因此它的行為不像理想的量化器。ADC固有地會增加輸入信號的噪聲和失真。設計目標是選擇噪聲和失真水平為可接受水平的ADC,以滿足數字解調器SNR要求。通常,良好的品質因數是0.6dB的劣化。這意味著ADC不會將輸入SNR降低超過0.6dB。因此,ADC的SNR必須比輸入信號SNR電平高8.86dB。換句話說,如果輸入信號的SNR為18.6dB,要實現18dB的SNR,ADC需要26.89dB的SNR,以防止輸入降級超過0.6dB。以下公式計算系統 SNR:

帕普爾:對于 2n載波(子載波= 256, 512, 2048)OFDM信令,PAPR為8dB至12dB。這意味著ADC輸入必須后退12dB,以防止峰值期間出現削波。應避免ADC削波,因為它會產生失真,從而降低SER性能。

增益/失調誤差:ADC增益誤差的主要因素是內部基準電壓源。內部基準在整個溫度范圍內的容差±5%。失調是內部ADC放大器電壓失調的殘余。增益和失調誤差是ADC誤差預算中的重要考慮因素,因為它們會減小可用動態范圍。如果增益誤差和失調誤差均為滿量程的10%,則每個誤差都會使動態范圍降低1dB。由于該誤差,ADC必須后退1dB以防止輸入削波,另外1dB后退以考慮有限的動態范圍。使用內部ADC基準電壓源可節省成本和尺寸,并消除庫存中的額外組件。合理的成本尺寸折衷方案是使用帶有集成基準的高速AFE,并增加2dB動態范圍裕量。

AGC 錯誤:典型的ZIF接收器集成AGC以設置基帶模擬I/Q輸出電壓信號電平。由于工藝、溫度和電源電壓的變化,AGC電平可能具有20%(±10%)的精度誤差。這意味著AGC中的誤差為2dB。為了在Rx ADC輸入端保持所需的SNR電平和PAPR退避,在SNR預算分析中應考慮AGC誤差。例如,如果實際AGC設置比預期設置低2dB,則SNR將低2dB。

通道過濾器:在某些情況下,RF接收器無法充分濾除不需要的相鄰信道干擾源。在這種情況下,Rx ADC必須具有足夠的動態范圍來處理阻塞信號電平和目標信號,同時保持所需信號的數字解調所需的SINAD。額外的動態范圍用于對不需要的干擾源進行數字濾波。或者,為了降低成本和芯片尺寸,可以減少基帶模擬濾波器階數,并以數字方式完成額外的濾波。模擬濾波器階數和數字濾波器階數之間存在dB對dB的關系,因此必須通過將Rx ADC的動態范圍提高6dB來彌補模擬濾波減少6dB。在本例中,假設阻塞信號衰減為12dB。

工藝增益:假設Rx ADC對基帶模擬I/Q信號進行2倍過采樣。由于基帶信號的帶寬 = 2.5MHz 和 FCLK = 10MHz,因此所得過程增益為 3dB。過程增益可將SNR提高3dB,可以從所需的Rx ADC SNR中減去。

上述分析得出的結論是,在FCLK = 51Msps時,SINAD = 86.10dB的Rx ADC可確保在SER = 5e-64時恢復1MHz、5QAM OFDM信號的數字解調器信號。

關于接收型 ADC 動態范圍的說明:請務必仔細查看Rx ADC數據手冊中指定SINAD和輸入滿量程電平的電氣特性表。為了充分利用完整的Rx ADC動態范圍,RX ADC輸入滿量程電平應與ZIF接收器的模擬I/Q輸出信號電平緊密匹配。例如,假設Rx ADC滿量程輸入為2VP-PSINAD指定為50dB。現在假設ZIF接收器的最大滿量程輸出為1VP-P.這意味著Rx ADC的有效后退6dB,從而使A的SINAD降低6dB在= 1VP-P.因此,可實現的SINAD在A時為44dB。在= 1VP-P.相反,如果Rx ADC設計為滿量程輸入A。在= 1VP-P并指定SINAD = 50dB,則可以使用完整的50dB動態范圍。

圖4.該圖顯示了給定符號錯誤概率和不同調制階數所需的SNR。

Tx DAC:多少位?

Tx DAC動態性能要求可以使用圖5中的示例Tx DAC SNR預算分析來計算。該分析基于ZIF發射器系列的誤差矢量幅度(EVM)規格。EVM 是許多空中接口標準(3G、4G 和 802.11)中使用的調制質量指標,定義為 RMS 星座誤差幅度與峰值星座符號幅度的比值。它以百分比表示,是發射機總性能的衡量標準,包括增益/相位誤差、符號誤差和通道內雜散發射等損傷。EVM 通過以下等式與 SNR 相關,因此可以與 SER 相關:

信噪比 = -20log (EVM/100%)

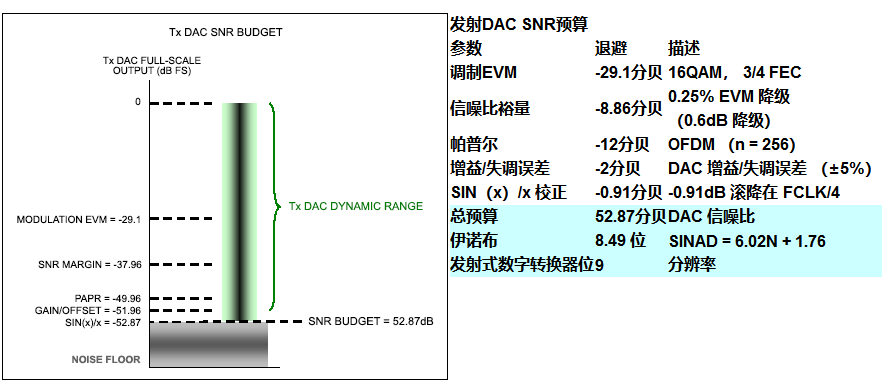

圖5中的性能預算分析使用16QAM調制,具有OFDMA、1e-6 SER、通道帶寬= 8.75MHz,并允許Tx DAC降級、DAC增益/失調誤差和PAPR。該分析以WiBro空中接口標準為例,但適用于任何無線寬帶標準。?

圖5.Tx DAC SNR預算包括許多影響整體動態范圍的因素。使用這種方法,設計人員可以確定所需的TX DAC ENOB。

發射DAC SNR預算涉及幾個因素:

調制 EVM:給定的空中接口參考設計(如WiBro)使用MAX2837 RF收發器,為3QAM提供5.16%的發射EVM,在POUT = 3dBm時提供4/3前向糾錯(4/23-FEC)編碼信號。EVM 規范以天線為參考,包括射頻調制器和功率放大器 (PA) 損傷。3.5% EVM 性能轉化為 -29.1dB SNR。

信噪比裕量:假設Tx DAC不能將系統SNR降低0.6dB以上,這意味著Tx EVM降級0.25%。總體而言,Tx EVM(包括Tx DAC貢獻)必須為3.75%(3.5%+ 0.25%)或28.5dB SNR。調制器和PA基于29QAM調制產生1.16dB SNR。因此,Tx DAC必須具有8.86dB的SNR才能產生0.6dB的衰減。Tx DAC需要37.96dB SNR (29.1dB + 8.86dB)。

帕普爾:對于 2n載波(子載波= 256, 512, 2048)OFDMA信令,PAPR為8dB至12dB。這意味著Tx DAC輸出必須回退-12dB,以防止峰值期間發生削波。DAC削波會產生信號失真,導致雜散輻射,從而降低SER性能。

增益/失調誤差:DAC增益誤差的主要因素是內部基準電壓源。內部基準在整個溫度范圍內的容差±5%。失調是內部DAC放大器電壓失調的殘余。增益和失調誤差是DAC誤差預算中的重要考慮因素,因為它們會降低可用動態范圍。如果增益和失調誤差均為滿量程的10%,則每個誤差都會使動態范圍降低1dB。由于該誤差,DAC必須后退1dB以防止輸出削波,另外1dB以考慮有限的動態范圍。

罪(x)/x 更正:f時的sin(x)/x頻率響應C/f外= f 時 -4.0dB 衰減為 91 個結果外= FCLK/4。在數字基帶中實現的有限脈沖響應(FIR)濾波器可以對此進行校正。或者,如果這種滾降是可以接受的,則可以在SNR預算中增加+0.91dB裕量,這解釋了在f時-0.91dB SNR下降的原因。外= FCLK/4。

上述分析得出結論,在FCLK = 52.87Msps時SNR = 17.5dB的Tx DAC可以在SER = 8e-75時合成16.1MHz,6QAM OFDMA WiBro信號頻譜。

輔助數字轉換器

輔助DAC通道主要用于電平控制功能,如接收器AGC和PA輸出功率。影響輔助DAC分辨率和轉換速率的因素包括增益控制電壓電平、增益范圍、增益步長和建立時間。典型的ZIF無線電具有大約60dB接收器AGC基帶增益范圍(0.5dB步長)、50dB發射器VGA范圍(步長為1dB)和30dB AFC范圍。輔助功能通常具有2V滿量程范圍和100ms建立時間。為了計算輔助DAC分辨率,AGC功能提供60dB增益范圍和0.5dB步長= 120步。因此,2n= 120 和 n = 6.9 位。

DAC通道需要保證單調性,積分非線性(INL)小于±2 LSB。不需要絕對精度,因為DAC通道用于閉環系統。然而,保證單調性對于保持環路穩定性很重要。為了確保系統線性度,在指定的可用代碼范圍內提供INL就足夠了。

輔助模數轉換器

輔助ADC參數主要由輸入信號電平和精度決定。但是,在某些應用中,例如802.11a,需要快速RSSI轉換(t<5μs)。通常,PA功率電平、電壓駐波比(VSWR)和溫度檢測等測量對于速度并不重要。典型的RF功率檢波器,如MAX4003,工作在RFIN = 1900MHz,模擬輸出電壓范圍為360mV (P在= -45dBm) 至 1.58V (P在= 0dBm)。MAX6613等典型溫度傳感器具有400mV至2V的模擬輸出范圍,精度為±4°C。通用轉換器的分辨率和轉換速率通常分別為8至10位和50ksps至300ksps。

轉換器摘要

與ZIF無線電接口時,以下數據轉換器參數可以支持64QAM下行鏈路,16QAM上行鏈路與OFDM;1 倍過采樣時為 25.5MHz 至 8MHz 通道帶寬,或 10 倍過采樣時高達 4MHz 通道帶寬:

雙通道、10 位、40Msps 高速接收 AD,SINAD = 51.86dB

雙通道、10位、40Msps高速發射DAC,SNR = 52.87dB

單個集成高速AFE器件,如MAX19713,可以滿足上述系統要求,并提供以下特性和優勢:

雙通道、10位、45Msps高速接收放大器,SINAD = 54.3dB,裕量為2.4dB

雙通道、10位、45Msps高速發射DAC,SNR = 56.1dB,裕量為3.2dB

Tx DAC 共模調節,帶 I/Q 失調調整

三通道、10位、低速輔助DAC,帶串行接口

10位、低速輔助ADC,具有2:1多路復用器和串行接口

在溫度范圍內經過生產測試

超低功耗,87mW (29mA, 3.0V),FD 模式,40Msps

結論

為了實現高頻譜效率和提供高數據吞吐量,當今的無線寬帶系統采用了先進的通信技術,如具有 OFDM 的高階調制、寬可變信道帶寬和 MIMO 無線電架構。這些先進的通信技術提高了無線電相關高速數據轉換器的性能要求,包括密集集成更多轉換器通道、更快的采樣速率、更高的動態范圍、更低的功耗和更小的尺寸。隨著數字基帶處理器的CMOS幾何尺寸從45nm擴展到28nm,以降低功耗并提高處理速度,將高性能、高速數據轉換器集成到大規模ASIC中變得更加困難,成本更高,風險也更高。

設計人員還面臨著更短的產品開發周期。他們必須以有限的資本支出實現快速上市,以控制成本。使這些問題更加復雜的是,無線終端產品不可阻擋的趨勢是集成更多的無線電功能,如WLAN、WAN、PAN、GPS和移動電視。無線電功能集成的這種趨勢迫使設計人員應對多種高速轉換器通道,這些通道必須與一系列不同的無線電接口,以支持各種空中接口標準。

高速AFE提供了一種有吸引力的解決方案,有助于應對這些相互關聯的IC工藝和產品開發趨勢。像MAX19713這樣的高速AFE具有多種產品開發優勢,包括快速上市、低初始投資和經過驗證的功能。這些器件還提供可靠且靈活的現成解決方案,可與高靈敏度射頻前端和亞微米數字基帶處理器調制解調器無縫連接。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8707瀏覽量

147236 -

濾波器

+關注

關注

161文章

7826瀏覽量

178187 -

adc

+關注

關注

98文章

6501瀏覽量

544741

發布評論請先 登錄

相關推薦

IF/RF數據轉換器中的數字信號處理在實際應用中是如何工作的呢?

使用現代高速數據轉換器的硬件設計人員面臨的挑戰

支持寬帶無線電的技術之RF轉換器

移動無線終端導航AFE和數據轉換器

軟件無線電中的模數轉換器和數模轉換器的性能分析及應用

請問A/D轉換器的模擬地和數字地如何分割才能更好的降低噪聲?

AFE78201,AFE88201低功耗的數模轉換器(DAC)數據表

在移動無線終端中的AFE和數據轉換器迷宮中導航

在移動無線終端中的AFE和數據轉換器迷宮中導航

評論