信號的時序設(shè)計

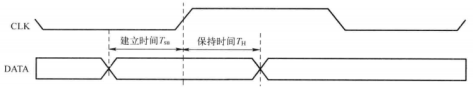

信號的時序要求就是數(shù)據(jù)信號與其對應(yīng)的時鐘信號保持某種同步關(guān)系。數(shù)據(jù)的采樣同樣依賴于某特定的時鐘,由于信號邊沿頻譜高最容易受干擾,因此在采樣時鐘對數(shù)據(jù)信號進行采樣時,應(yīng)盡可能遠離信號變化的邊沿。如下圖所示:

時鐘CLK采樣數(shù)據(jù)DATA的示意圖

數(shù)據(jù)DATA發(fā)生變化后,需要等待Tsu的建立時間才能被采樣,采樣之后,相對于采樣點,數(shù)據(jù)需要保持TH時間,這樣才能實現(xiàn)對數(shù)據(jù)的有效接收。也就是說,為了使信號具有較好的時序設(shè)計余量,需要盡可能加大信號采樣需要的信號建立時間和保持時間。

時序系統(tǒng)

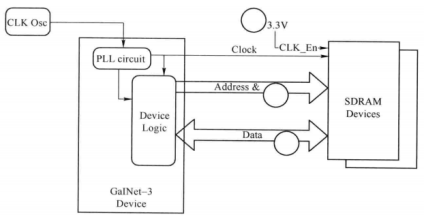

高速電路設(shè)計中所涉及的時序系統(tǒng)主要分為兩類:源同步系統(tǒng)和共同時鐘系統(tǒng)。源同步系統(tǒng)的同步時鐘由發(fā)送數(shù)據(jù)或接受數(shù)據(jù)的芯片提供;而共同時鐘系統(tǒng)的時鐘是由另外的時鐘芯片提供。如下圖所示:

源同步系統(tǒng)示例

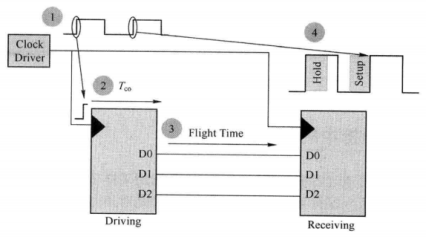

共同時鐘系統(tǒng)示例

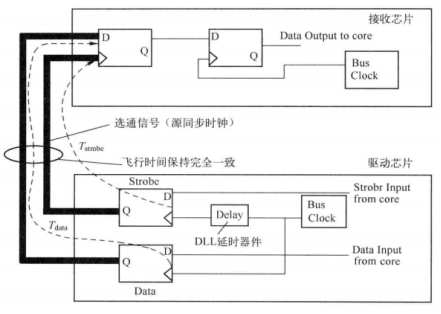

作者舉了一個例子,一個基本的源同步時鐘系統(tǒng)的結(jié)構(gòu)示意如下圖所示:

源同步時鐘系統(tǒng)的結(jié)構(gòu)示意圖

驅(qū)動芯片在發(fā)送數(shù)據(jù)信號的同時也產(chǎn)生了選通信號,而對于接收端的觸發(fā)器,接收該選通信號脈沖數(shù)據(jù),這個選通信號也可以稱為源同步時鐘信號。

在源同步時鐘系統(tǒng)中,數(shù)據(jù)和源同步時鐘信號是同步傳輸?shù)模谠O(shè)計中要保證這兩個信號的飛行時間完全一致,說白了就是信號怎么發(fā)送的,就要怎么接收到。例如在進行DDR類存儲的電路設(shè)計時所進行的PCB蛇形走線,都是為了滿足信號之間的時序要求。

S參數(shù)模型、IBIS參數(shù)模型

作者對信號完整性分析中的S參數(shù)模型、IBIS參數(shù)模型的概念做了介紹。S參數(shù)是一種描述線性無源互連結(jié)構(gòu)的行為模型,S參數(shù)模型把互連結(jié)構(gòu)看成一個黑盒子,僅通過端口處的能量就可以描述互連結(jié)構(gòu)的行為特征。

IBIS是用來描述IC器件的輸入、輸出和I/O Buffer行為特性的文件,也是一個行為模型,可以反映器件開關(guān)速度和驅(qū)動能力等特性,并且可以用來模擬Buffer和板上電路系統(tǒng)的相互作用,工程人員可以利用這個模型對PCB上的電路系統(tǒng)進行SI、串?dāng)_、EMC及時序的分析。

審核編輯:劉清

-

PCB設(shè)計

+關(guān)注

關(guān)注

394文章

4730瀏覽量

88044 -

emc

+關(guān)注

關(guān)注

170文章

4030瀏覽量

185183 -

高速電路

+關(guān)注

關(guān)注

8文章

161瀏覽量

24457 -

數(shù)據(jù)信號

+關(guān)注

關(guān)注

0文章

59瀏覽量

12061 -

時鐘信號

+關(guān)注

關(guān)注

4文章

459瀏覽量

28933

發(fā)布評論請先 登錄

相關(guān)推薦

評論