本文介紹了達拉斯半導體如何改進傳統的8051微控制器,創建可執行高達33MIP的高性能直接替代品。多個數據指針、擴展內存尋址(高達 16MB)和閃存等附加功能提高了設備的速度和實用性。

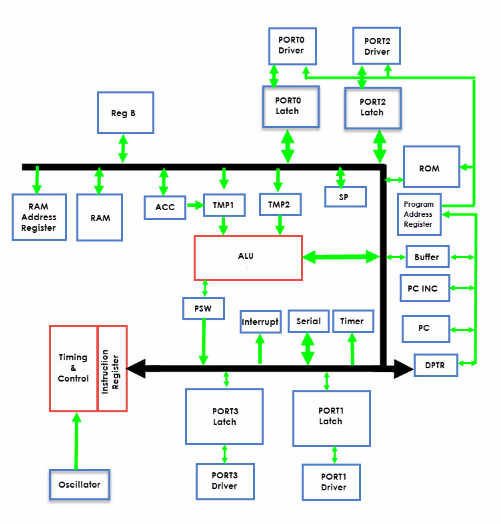

系統設計人員知道,微控制器是任何嵌入式系統的核心,而這正是行動發生的地方。ADI公司的全資子公司達拉斯半導體一直在重新定義無處不在的8051微控制器。也許過去10年中最大的改進是在指令執行速度方面。我們的 1 個機器周期時鐘處理器達到了一個非凡的性能目標 — 每個機器周期 1 個時鐘,目前為每秒 33 萬條指令 (MIPS)。利用這一內核,我們的安全、聯網和混合信號 8051 微控制器系列繼續為功能集成和創新設定標準。

為什么基于古老的 8051 指令集構建一系列創新微控制器?因為,很簡單,它是世界上最受歡迎的8位微控制器架構之一。該指令集易于理解,使其成為嵌入式系統設計人員的最愛。許多指令直接針對I/O引腳,允許快速操作(位敲擊)外部外設。片上外設種類繁多,組合數量幾乎不受限制。此外,8051微控制器系列的開發工具廣泛可用,因此開始開發應用既簡單又便宜。

安全可靠

1987年,達拉斯半導體/模擬公司推出了DS5000T,這是一款基于8051指令和功能集的獨立開發的微控制器。為了提供新的功能和優勢,我們的工程師基于NV SRAM技術而不是EPROM進行設計。憑借其在低功耗技術方面的領先地位,存儲器分區和電池備份電路直接集成到微控制器芯片上。該系統的主要優點是速度。寫入大多數非易失性存儲器的速度很慢,但NV SRAM可以在單個周期內高速讀取或寫入。這使其成為必須實時捕獲數據的高速、非易失性數據記錄應用的理想選擇。當與外部SRAM和電池結合使用時,結果是一個完整的微控制器系統,具有高達64kB的非易失性程序和數據存儲器。

NV SRAM技術使數據和程序存儲器能夠在系統內逐字節動態重新編程。在標準微控制器系統中,程序存儲器需要從系統中物理移除(EPROM)或塊擦除,從而禁止在擦除(閃存)期間訪問存儲器。基于NV SRAM的微控制器可以通過其串行端口從PC或設備編程器快速輕松地進行編程。駐留在ROM中的自舉加載程序將程序和數據直接下載到微控制器,從而實現快速調試或現場升級。

NV SRAM的獨特優勢為固件安全提供了新的視角。由于引導加載程序完全控制程序加載到 NV SRAM 中,因此我們使用 40 位或 80 位加密密鑰對地址和數據總線進行了加密。加載到微控制器中的任何程序或數據在存儲在SRAM中之前都會自動加密。這種加密可以阻止黑客竊取微控制器中的程序或數據。在執行指令期間,微控制器獲取加密的操作碼,在單個機器周期內解密并執行它。使用NV SRAM允許全速讀/寫訪問,指令解碼沒有延遲。

這些安全特性最終形成了DS5250,這是一款用于全球金融終端和支付系統的安全8051微控制器。這些防篡改響應微控制器集成了每機器周期 4 個時鐘的 8051 內核,并對其程序存儲器進行了增強的三重 DES 加密。通過添加入侵檢測輸入和片上篡改傳感器,可自動擦除存儲器作為篡改響應,進一步增強了安全性。一體式微探頭屏蔽層可防止芯片篡改。同樣,NV SRAM最適合高安全性應用。其高速寫入時序允許微處理器比任何其他類型的存儲器更快地擦除機密或敏感數據。

DS5250是唯一能夠提供最高安全性同時全速執行每條指令的微控制器。

更快的速度,更低的功率

盡管 8051 處理內核從 1970 年代后期到 1980 年代的概念一直保持靜止,但嵌入式系統卻沒有。系統設計人員通過添加新的軟件功能和外設,繼續改進和升級其基于 8051 的應用程序。這種“功能蠕變”突破了可用 8051 性能的極限。不幸的是,8051內核的改進未能跟上步伐,系統設計人員似乎不得不切換到另一個處理器并執行昂貴的重新設計來升級他們的系統。

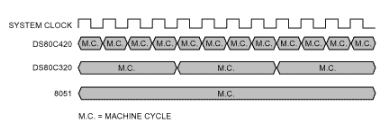

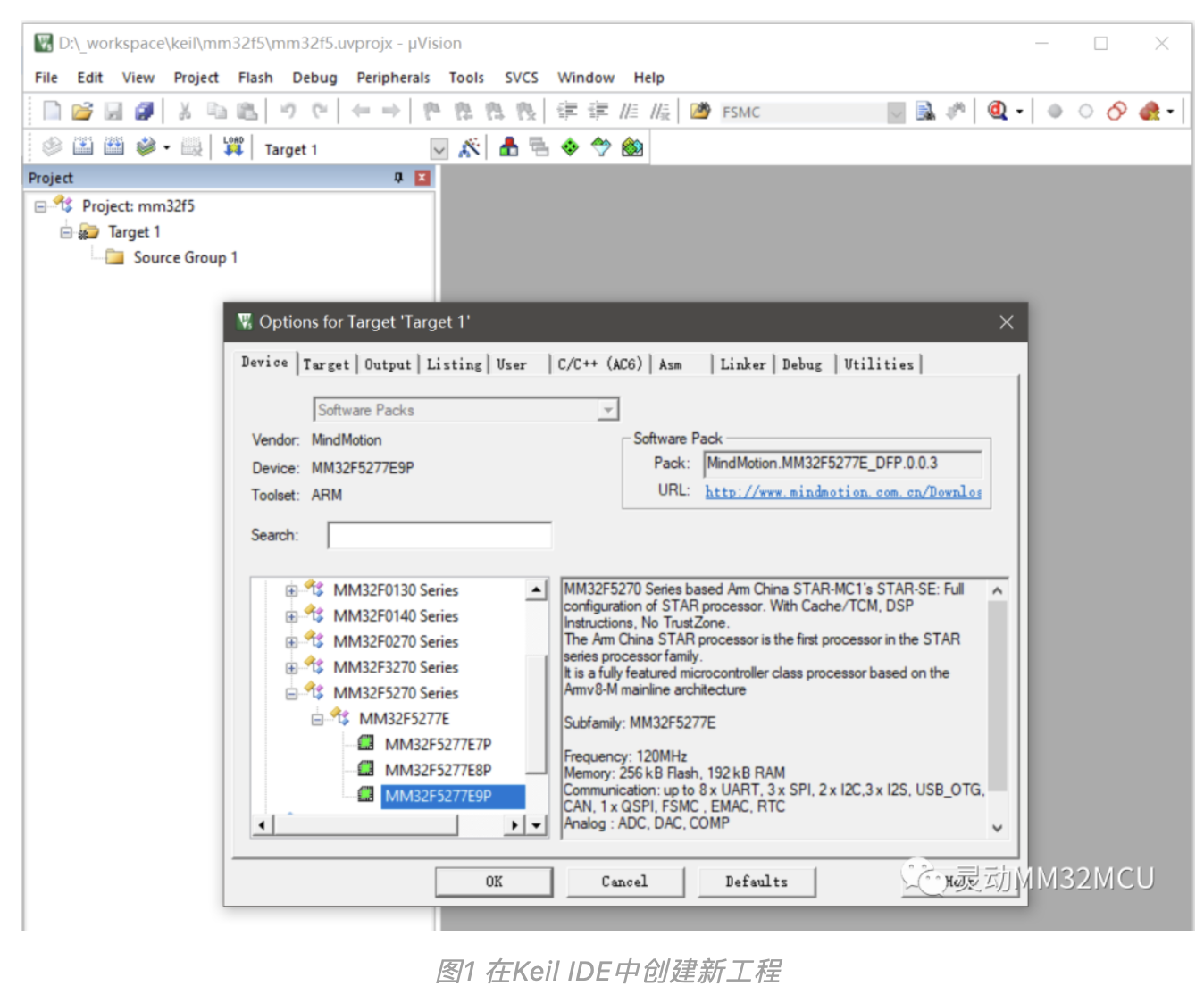

性能瓶頸是 1970 年代 8051 微控制器的老式處理內核。盡管外部晶體速度接近40MHz,但傳統的8051仍然需要12個時鐘來執行單個機器周期。每條指令需要 1 到 4 個機器周期,這意味著一條指令可能需要少至 12 個或多達 48 個振蕩器時鐘。因此,吞吐量被限制在略高于 3 MIPS,即使在執行一串 1 周期 NOP 指令這樣基本的東西時也是如此(圖 1)。

圖1.減少每個機器周期的時鐘數量可以在相同的指令集下實現 3 倍的性能(每個機器周期 12 對 4 對 1 個時鐘)。

1991 年,我們著手重新設計 8051 微控制器以提高性能。工程團隊首先分析了傳統的 8051 設計。最初的每臺機器周期 12 個時鐘架構非常浪費;大多數指令被迫執行虛擬循環。工程師從頭開始重建 CPU,使其每個機器周期只需要 4 個時鐘,而不是 12 個。第二條內部數據總線消除了可能影響性能的架構瓶頸。高功率 I/O 驅動器提高了外部存儲器操作期間的開關速度。所有內部外圍設備(如定時器和串行端口)都以更快的時鐘速度運行。但每一步都有一個絕對必要性——指令集必須與 8051 指令集保持操作碼兼容。

結果呢?基于 8051 的新型微控制器的效率是原始 8051 內核的三倍,在相同的振蕩器頻率下,大多數指令的運行速度提高了三倍。除了內核效率的提高外,大多數器件的最大外部振蕩器頻率增加到33MHz或40MHz。系統設計人員以前受到較舊、速度慢得多的 8051 的阻礙,無需更改軟件即可將系統升級到 10 MIPS 的最高速度。

除了速度改進之外,內核重新設計還帶來了另一個好處:降低功耗。物理定律規定,數字電路消耗的功率與開關晶體管的數量和開關速率(頻率)成正比。由于新內核每個機器周期使用的振蕩器時鐘更少,因此與傳統的 8051 相比,它每秒每條指令消耗的功率要少得多。

電源管理模式通過使用軟件可配置的內部時鐘分頻器暫時降低了微控制器的功耗。通過將機器循環速率從每個機器循環 4 個時鐘降低到每個機器周期 64 或 256 個時鐘,進一步降低了功耗。回切功能允許器件在收到外部中斷或檢測到串行端口起始位時返回到4分頻模式。這使得器件能夠保持低功耗狀態,但在需要時可以快速恢復全速運行。圖2顯示了不同模式下的相對功耗。

圖2.在活動減少期間,我們的電源管理模式消耗的電流比空閑模式少,但仍允許 CPU 運行。

33 MIPS 及以上

1997年,達拉斯半導體/模擬公司開始設計終極性能的內核。基于 8051 的應用程序不斷發展,客戶要求更高的性能。工程團隊將目光投向了性能峰值:一個執行 8051 指令集但每臺機器周期僅使用 1 個時鐘的微控制器。使用高度并行的架構和新的制造工藝,設計了一種引腳對引腳的直接替代品 8051。

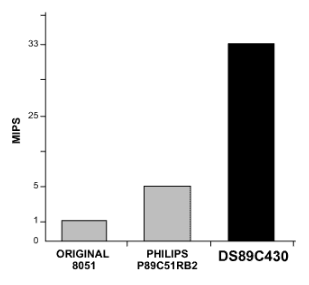

其結果是新型DS89C430/DS89C450,超高性能每機器周期1時鐘微控制器,能夠執行高達33 MIPS(圖3)。這些器件打破了以前的性能障礙,以 16 位價格提供 8 位微控制器性能。各種總線尋址模式允許用戶根據特定應用設計的需要微調處理器操作。但最重要的是,它們仍然與 100 指令集 8051% 兼容,并且仍然比任何其他基于 8051 的微控制器更快地執行現有的 8051 應用。

圖3.DS89C430的時鐘頻率為33 MIPS,超越了競爭對手。

除了閃電般的內核外,DS89C430/DS89C450還集成了高達64kB的系統內可編程閃存。基于ROM的自舉加載器允許在最終組裝之前、期間或之后修改微控制器代碼,從而提供最大的靈活性。與其他使用專有或非標準接口的微控制器不同,DS89C430自舉加載程序可通過其串行端口從標準PC訪問,使用任何終端仿真器軟件。

快速執行時間乞求更大的程序規模

如果程序員沒有足夠的內存地址空間來存儲他們的表達式,那么速度的優勢就會喪失。傳統的8051使用16位內存總線,將內存范圍限制為64kB。對于某些應用程序,這種有限的內存范圍就足夠了。但隨著應用程序代碼大小和復雜性的增加,我們意識到應用程序需要一種盡可能保持 8051 兼容性的解決方案。

一些設計人員發現,通過使用組交換技術可以擴展尋址范圍。I/O 線兼作地址線,以犧牲外設 I/O 為代價擴展內存。但這有兩個主要缺點。首先,必須將代碼分割成 64kB 或更小的塊,這是一項耗時的任務,每次修改代碼時都必須重做。其次,必須編寫軟件例程,以便在每次代碼在段之間轉換時手動將 I/O 行切換到適當的狀態。與這些工作相關的軟件開銷會降低性能。

更好的解決方案是實現具有更大地址總線的設備,該總線可尋址更多內存。DS80C400具有24位地址總線,可直接尋址16MB程序存儲器和16MB數據存儲器。這不需要在 8051 指令集中使用任何新的操作碼即可完成。提供兩種模式。第一種是分頁尋址模式,它結合了先進的自動庫切換,大大加快了擴展內存訪問的速度,同時保持與傳統 8051 編譯器的二進制兼容。第二種連續模式允許對整個 16MB 內存映射進行透明尋址,并且需要一個編譯器來提供 24 位地址所需的額外操作數。更大的地址空間允許更快地訪問更大的程序,開辟了新的可能性,如大型數學函數庫、查找表,甚至Java?虛擬機,由網絡微控制器支持,包括執行模擬微型網絡接口(MxTNI?)運行時環境的DS80C390和DS80C400。

每一步都有一個絕對必要性——指令集必須與 8051 指令集保持操作碼兼容。

數據指針性能翻倍

有必要對芯片的各個方面進行深遠的改進,以避免產生性能瓶頸。最重要的改進涉及訪問MOVX數據存儲器。在原始8051上操縱數據存儲器是一件繁瑣的事情。在讀取或寫入目標地址之前,訪問MOVX存儲器的單個字節需要多個周期來加載單個16位數據指針。

DS89C430保持100%8051指令集兼容性,因此它執行現有8051應用的速度仍然比任何其他基于8051的微控制器快。

如果軟件需要執行塊復制操作,則效率低下會成倍增加,這涉及將數據從一個MOVX內存位置移動到另一個MOVX內存位置。單個數據指針限制迫使它在塊復制操作中兼作源地址和目標地址。傳統 8051 微控制器上的操作是一個復雜的多步驟過程:

將源地址加載到數據指針中。

遞增或修改指向下一個基準的數據指針。

將數據從MOVX存儲器獲取到累加器中。

將修改后的源地址保存到存儲寄存器。

將目標地址加載到數據指針中。

遞增或修改指向下一個基準的數據指針。

將數據從累加器寫入 MOVX 內存。

將修改后的目標地址保存到存儲寄存器。

較大的地址空間允許更快地訪問更大的程序,例如網絡微控制器支持的 Java 虛擬機。

人們很快注意到,上述過程中幾乎一半的步驟專門用于在單個數據指針中處理源地址和目標地址,這會影響整體性能。該解決方案添加了第二個數據指針,為源和目標創建專用寄存器。使用第二個數據指針,大部分數據操作可以在硬件中處理,從而減少軟件開銷。雙數據指針可單獨尋址,專用數據指針選擇位指示MOVX指令期間哪個數據指針是活動數據指針。使用雙數據指針執行相同的塊復制操作所需的步驟要少得多。

僅執行一次初始化:

將源地址初始化為第一個數據指針。

將目標地址初始化為第二個數據指針。

主循環:

將數據提取到累加器中。

遞增或修改指向下一個源基準的第一個數據指針。

將數據指針選擇器切換到第二個數據指針。

將數據從累加器寫入 MOVX 內存。

遞增或修改指向下一個基準的數據指針。

圖4所示為1000MHz DS33C89上的430字節塊復制例程,當雙數據指針消除了處理單個數據指針的相關開銷時,執行時間減少了33%。高速和超高速微控制器系列的一些成員還具有額外的可選數據指針增強功能。自動遞增/遞減功能(在圖4中表示為AID)根據MOVX相關指令自動遞增或遞減數據指針,無需INC DPTR指令。自動切換功能(在圖4中表示為TSL)在MOVX相關指令之后自動切換活動數據指針,消除了在數據指針之間切換的指令。圖 4 顯示了將所有這些功能一起考慮時的相對執行時間。請注意,啟用所有功能后,DS89C430執行1000字節塊復制程序的速度比原來的103微處理器快8051%。

圖4.雙數據指針增強功能可提高塊復制操作的速度。

展望未來

隨著應用對速度的要求越來越高,模擬越來越努力地超越以前的性能設計。無論是更快的堆棧訪問、擴展尋址,還是原始處理速度,我們的微控制器設計都能繼續滿足嵌入式系統設計人員的需求。

但有競爭力的設計需要的不僅僅是速度。更復雜的應用需要更大的程序,因此我們正在擴展我們的嵌入式 8051 微控制器產品線,以包括 64kB 閃存。我們的新產品管線在設計上具有外設,以提高其嵌入式系統的功能,同時減少電路板空間。聯網微控制器具有先進的功能,包括CAN、以太網和用于多層網絡的1-Wire?網絡連接。安全微控制器具有用于公鑰加密的基于硬件的數學加速器,并支持密鑰的快速歸零作為篡改響應。混合信號微控制器執行實際信號處理,以制造更好的終端設備。

我們對微控制器性能的承諾不僅限于 8051 內核。我們新的MAXQ? 16位RISC微控制器系列實現了高性能功率比。實現此目的的基本方法是通過單周期指令執行。單周期指令執行通過增加指令帶寬從而提高性能和/或通過降低時鐘頻率的能力降低功耗,使最終用戶受益。所有MAXQ指令在單個時鐘周期內執行,但跳遠/長調用和某些擴展寄存器訪問除外。雖然許多RISC微控制器聲稱支持單周期執行,但這通常適用于一小部分指令或尋址模式。使用MAXQ,單周期執行是常態。

此外,MAXQ架構不需要指令流水線(許多RISC微控制器通用)來實現單周期工作,因此提高了時鐘周期利用率。MAXQ指令解碼和執行硬件非常簡單(時序也非常快),這些操作與程序獲取本身進入相同的時鐘周期,對最大工作頻率的影響最小。為了說明消除指令流水線的好處,請考慮從流水線執行的通用RISC CPU。當程序分支發生時,CPU 使用一個或多個時鐘周期(取決于管道深度)將程序提取轉移到目標分支地址,并丟棄已獲取的指令。顯然,使用時鐘周期丟棄指令而不是執行指令是浪費和不可取的,因為它會降低性能并增加功耗。雖然該操作對用戶來說是不希望的,但 CPU 為重新加載管道而竊取的時鐘是體系結構的產物,并且是不可避免的。MAXQ架構區別于其他8位和16位RISC微控制器,提供單周期執行,無需指令流水線(以及隨之而來的浪費時鐘周期)。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7573瀏覽量

151665 -

嵌入式

+關注

關注

5087文章

19149瀏覽量

306218 -

cpu

+關注

關注

68文章

10882瀏覽量

212252

發布評論請先 登錄

相關推薦

8051微控制器的基礎知識

如何使用ISP1763作為替代品?

Commodore 6540 ROM的替代品

高速8051微控制器:引領成長與創新之路

如何改進8051微控制器創建可執行高達33MIP的高性能直接替代品

如何改進8051微控制器創建可執行高達33MIP的高性能直接替代品

評論