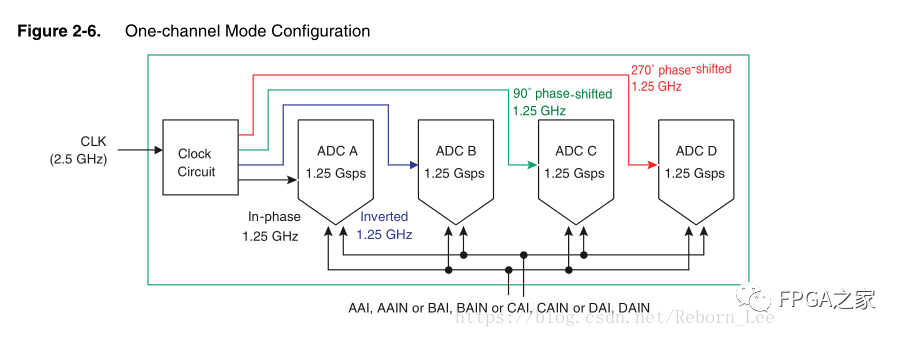

直接看框架圖吧:

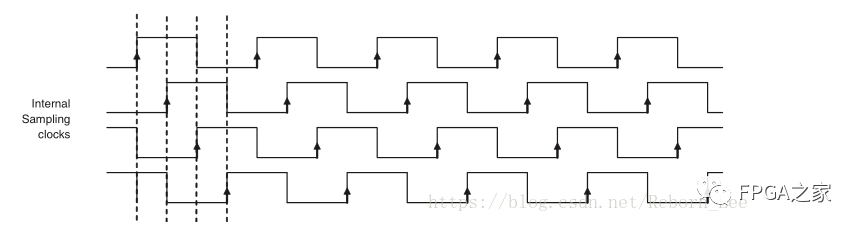

直接說重點(diǎn),任意一個(gè)輸入端口輸入的模擬信號(hào)同時(shí)進(jìn)入ADC芯片的四個(gè)核(也可以理解為4個(gè)通道),這四個(gè)核的時(shí)鐘輸入是由內(nèi)部時(shí)鐘電路(Clock Circuit)產(chǎn)生的,這四個(gè)時(shí)鐘之間是什么關(guān)系呢?

首先這四個(gè)時(shí)鐘頻率一致,都是1.25GHz。

其次,假設(shè)以ADC A這個(gè)核的時(shí)鐘為坐標(biāo)系(稱之為標(biāo)準(zhǔn)時(shí)鐘),那么由上圖易知,ADC B的時(shí)鐘輸入為偏移了180°的時(shí)鐘,同理,ADC C的輸入時(shí)鐘偏移了90°,ADC D的輸入時(shí)鐘偏移了270°。

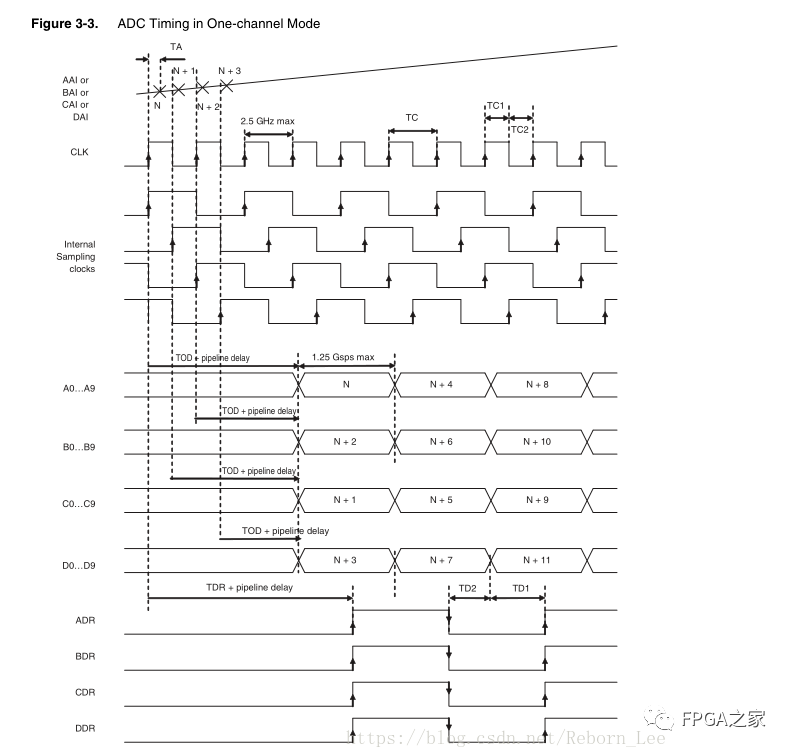

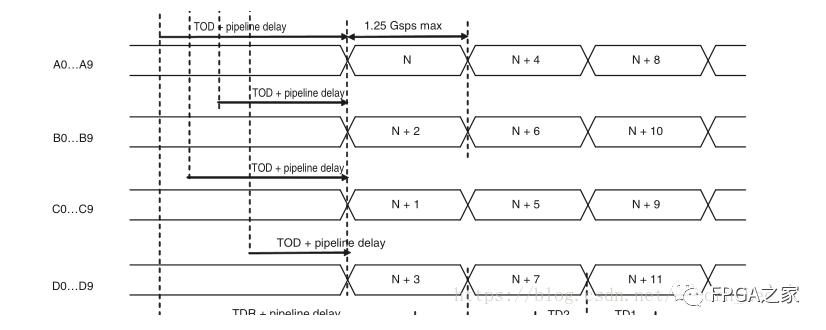

其時(shí)序圖如下:

我們分解開來看:

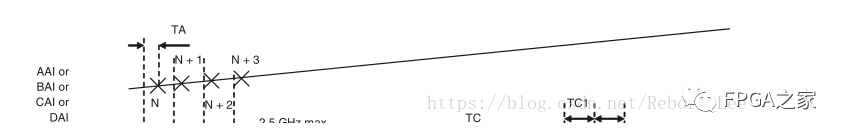

模擬輸入XAI:

基準(zhǔn)時(shí)鐘CLK:

將上面的基準(zhǔn)時(shí)鐘2分頻,然后各種相位偏移得到如下內(nèi)部采樣時(shí)鐘:

可以將上面的內(nèi)部時(shí)鐘由上到下編號(hào)為clk_a、clk_c、clk_b、clk_d,每個(gè)時(shí)鐘的上升沿到達(dá)時(shí),都會(huì)對(duì)輸入模擬數(shù)據(jù)進(jìn)行一次采樣,這樣就相當(dāng)于采樣時(shí)鐘的最高頻率為5GHz,多么充分地應(yīng)用了4個(gè)核的優(yōu)勢(shì)呀!

由完整的時(shí)序圖還可以看出clk_a的第一個(gè)時(shí)鐘上升沿到達(dá)時(shí),核A(ADC A)采樣的數(shù)據(jù)為N,clk_c的第一個(gè)時(shí)鐘上升沿到達(dá)時(shí),采樣的數(shù)據(jù)為N+1,adc_b的第一個(gè)時(shí)鐘上升沿到達(dá)時(shí),采樣的數(shù)據(jù)為N+2,adc_d的第一個(gè)時(shí)鐘上升沿到達(dá)時(shí),采樣的數(shù)據(jù)為N+3,后面依次循環(huán)。

從下面這張圖上也能看出上面的采樣數(shù)據(jù)關(guān)系:

A0...A9就是ADC A采樣得到的數(shù)據(jù);(N)

B0...B9就是ADC B采樣得到的數(shù)據(jù);(N+2)

C0...C9就是ADC C采樣得到的數(shù)據(jù);(N+1)

D0...D9就是ADC D采樣得到的數(shù)據(jù);(N+3)

恰好第一個(gè)時(shí)鐘時(shí)鐘上升沿到達(dá)時(shí),4個(gè)核采樣四個(gè)數(shù)據(jù)。

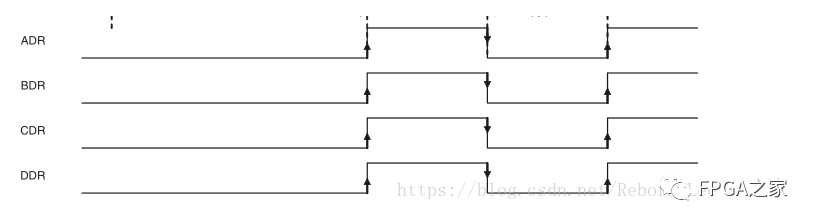

同樣,下面就進(jìn)入了數(shù)據(jù)同步環(huán)節(jié):

同步時(shí)鐘仍然是基準(zhǔn)時(shí)鐘的4分頻,也就是說同步時(shí)鐘的頻率是基準(zhǔn)時(shí)鐘CLK的1/4。

ADR的第一個(gè)時(shí)鐘上升沿到達(dá)時(shí),同步數(shù)據(jù)N,之后是同步數(shù)據(jù)N+1,再之后同步數(shù)據(jù)N+2,然后是N+3,ADR、BDR、CDR、以及DDR四個(gè)同步時(shí)鐘理論上是一致的,時(shí)鐘上升沿以及下降沿同時(shí)有效。

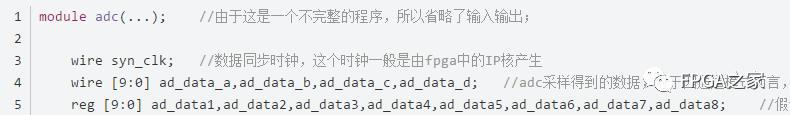

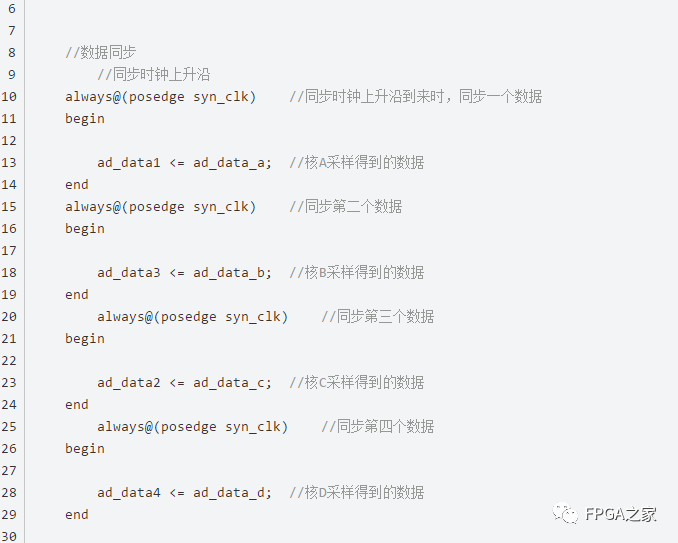

程序的部分思路如下:

module adc(...); //由于這是一個(gè)不完整的程序,所以省略了輸入輸出;

wire syn_clk; //數(shù)據(jù)同步時(shí)鐘,這個(gè)時(shí)鐘一般是由fpga中的IP核產(chǎn)生

wire [9:0] ad_data_a,ad_data_b,ad_data_c,ad_data_d; //adc采樣得到的數(shù)據(jù),對(duì)于四通道模式而言,此為A端口輸入模擬信號(hào),采樣得到的數(shù)據(jù)

reg [9:0] ad_data1,ad_data2,ad_data3,ad_data4,ad_data5,ad_data6,ad_data7,ad_data8; //假設(shè)該寄存器變量用于存放adc采樣得到的數(shù)據(jù)

???

審核編輯:劉清

-

模擬信號(hào)

+關(guān)注

關(guān)注

8文章

1135瀏覽量

52523 -

時(shí)鐘電路

+關(guān)注

關(guān)注

10文章

237瀏覽量

50759 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17185 -

ADC采樣

+關(guān)注

關(guān)注

0文章

134瀏覽量

12872 -

ADC芯片

+關(guān)注

關(guān)注

3文章

78瀏覽量

20352

原文標(biāo)題:解讀ADC采樣芯片(EV10AQ190A)的工作模式(單通道模式)

文章出處:【微信號(hào):zhuyandz,微信公眾號(hào):FPGA之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

解讀ADC采樣芯片(EV10AQ190A)的工作模式(四通道模式)

高性能DAC與ADC轉(zhuǎn)換技術(shù)

EV10AQ190AVTPY 模擬多路復(fù)用器現(xiàn)貨

EV12DS460

解讀ADC采樣芯片(EV10AQ190A)的工作模式(單通道模式)

ADC10模塊的寄存器及其工作模式

EV8AQ160型ADC在2.5 Gsps雙通道高速信號(hào)采集系統(tǒng)中的應(yīng)用

一種高速ADC接口電路設(shè)計(jì)方案

EV12AQ605,EV12AQ600面向競爭激烈的大用量應(yīng)用的優(yōu)化版本

解讀ADC采樣芯片EV10AQ190A的工作模式

解讀ADC采樣芯片EV10AQ190A的工作模式

評(píng)論