Umesh Jayamohan

自從第一個(gè)單芯片、硅基模數(shù)轉(zhuǎn)換器(ADC)問(wèn)世以來(lái),ADC一直跟上硅處理技術(shù)的快速發(fā)展。多年來(lái),硅處理技術(shù)已經(jīng)足夠先進(jìn),現(xiàn)在可以經(jīng)濟(jì)地設(shè)計(jì)具有更強(qiáng)大數(shù)字處理功能的ADC。早期的ADC設(shè)計(jì)除了糾錯(cuò)和數(shù)字驅(qū)動(dòng)器外,很少使用數(shù)字電路。新系列GSPS(每秒千兆采樣)轉(zhuǎn)換器(也稱為RF采樣ADC)采用先進(jìn)的65 nm CMOS技術(shù),可以集成更多的數(shù)字處理能力,以增強(qiáng)ADC的性能。

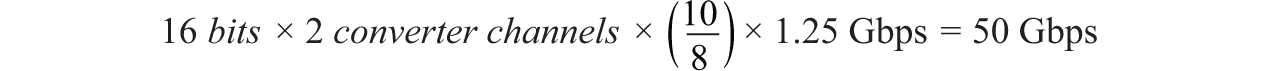

高采樣率(在GSPS領(lǐng)域)也帶來(lái)了巨大的數(shù)據(jù)有效載荷(每秒比特?cái)?shù))。以雙通道9680位、14.1 GSPS/25 GSPS/1 MSPS/820 MSPS雙通道JESD500B模數(shù)轉(zhuǎn)換器AD204為例。在 1.25 GSPS 的最大采樣速率下,ADC 流

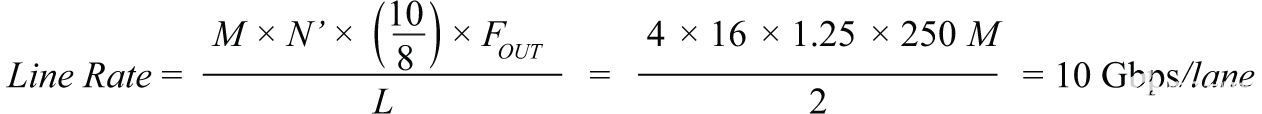

如此大量的數(shù)據(jù)將需要大量的LVDS路由通道來(lái)提取數(shù)字?jǐn)?shù)據(jù)。為了便于實(shí)現(xiàn)這種大吞吐量,采用了JESD204B標(biāo)準(zhǔn)。JESD204B是一種高速數(shù)據(jù)傳輸協(xié)議,采用8b/10b編碼和加擾等功能,旨在提供足夠的信號(hào)完整性。使用JESD204B標(biāo)準(zhǔn),總吞吐量現(xiàn)在變?yōu)?/p>

使用JESD204B標(biāo)準(zhǔn),數(shù)據(jù)吞吐量可以分布在四個(gè)高速串行通道上,每個(gè)通道上以12.5 Gpbs的速度分配。將其與LVDS接口進(jìn)行比較,在LVDS接口中,在大約1 Gbps/通道的線速上限下,芯片將需要超過(guò)28對(duì)!

快速檢查AD9680數(shù)據(jù)手冊(cè)就會(huì)發(fā)現(xiàn),在設(shè)置鏈路方面,有相當(dāng)多的字母湯。早期LVDS ADC更容易實(shí)現(xiàn),而新一代JESD204B ADC則稍微復(fù)雜一些。當(dāng)您考慮到內(nèi)部數(shù)字下變頻器(DDC)設(shè)置時(shí),它們變得更加復(fù)雜。但是,ADC設(shè)置主要由該字母表中的三個(gè)字母決定:

L = 每個(gè)JESD204B鏈路的通道數(shù)

M = 每個(gè)JESD204B鏈路的轉(zhuǎn)換器數(shù)量

F = JESD204B鏈路中每幀數(shù)據(jù)的八位字節(jié)數(shù)

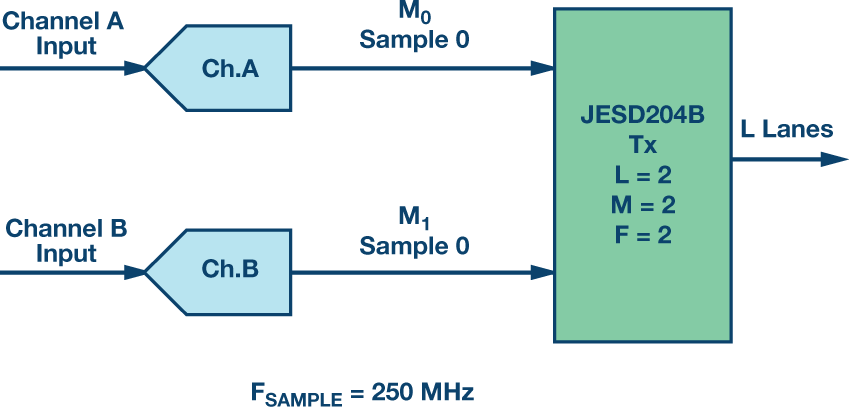

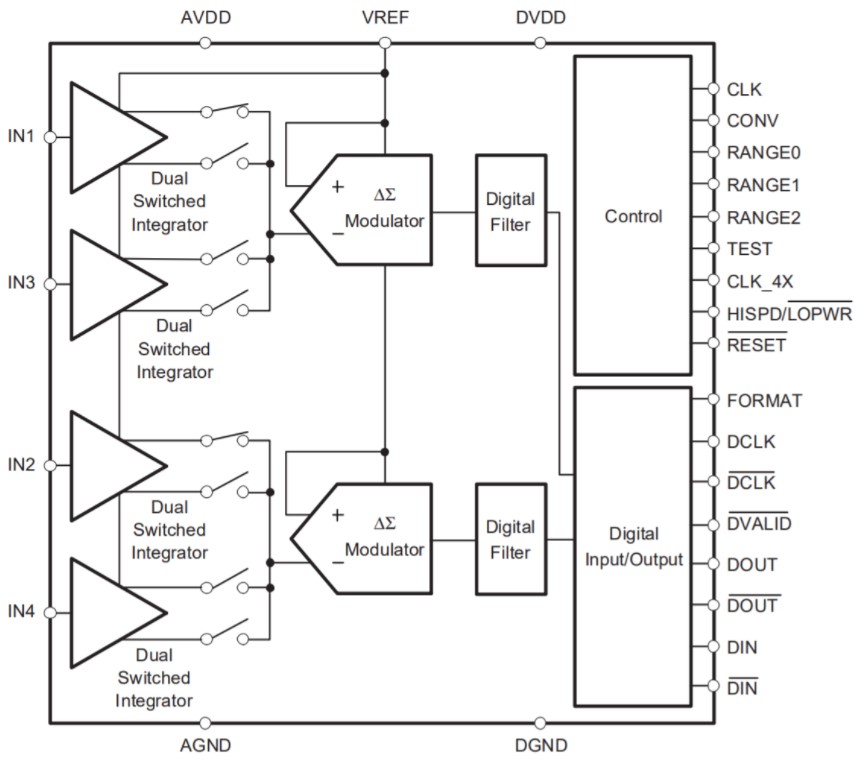

以AD9250為例,它是一款雙通道14位、250 MSPS JESD204B模數(shù)轉(zhuǎn)換器。圖1顯示了AD9250在默認(rèn)設(shè)置下的框圖。

圖1.設(shè)置AD9250。

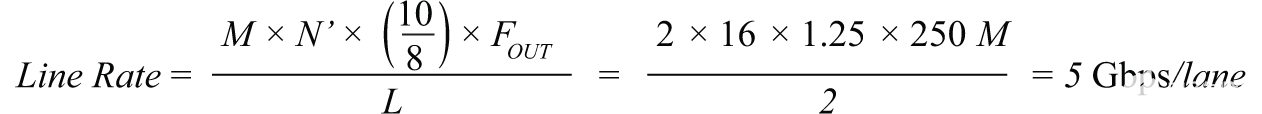

在此設(shè)置中,JESD204B鏈路(JESD204B發(fā)送器)非常簡(jiǎn)單,因?yàn)锳D9250無(wú)需進(jìn)行額外的數(shù)字處理。對(duì)于JESD204B鏈路,通道A變?yōu)檗D(zhuǎn)換器0 (M0),而通道 B 變?yōu)檗D(zhuǎn)換器 1 (M1),這意味著 M 的值變?yōu)?2。此設(shè)置的總線速為

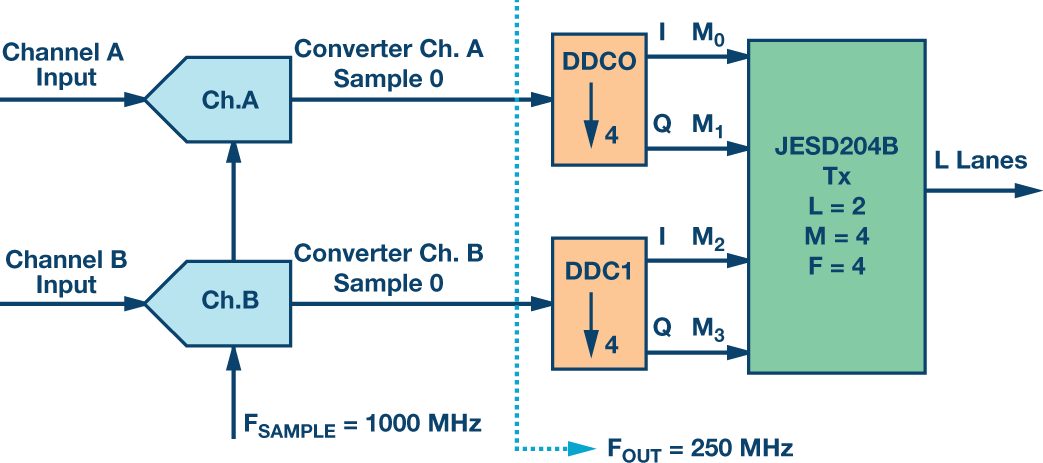

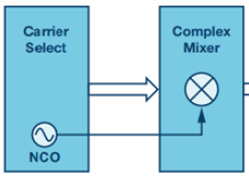

將其與AD9680在1 GSPS下的采樣進(jìn)行比較,但在本例中,在復(fù)雜(I/Q)設(shè)置中使用兩個(gè)數(shù)字下變頻器。圖2所示為AD9680,其中使用數(shù)字下變頻器將1 GSPS采樣的數(shù)據(jù)抽取<>倍。這會(huì)產(chǎn)生輸出采樣率 (F外) 的 250 MSPS。

圖2.設(shè)置AD9860-1000時(shí),兩個(gè)DDC設(shè)置為抽取4。

從圖2可以清楚地看出,AD9680使用內(nèi)部片內(nèi)數(shù)字下變頻器可以有效降低采樣速率。由于每個(gè)DDC輸出一個(gè)16位流,因此實(shí)際(物理)轉(zhuǎn)換器位流現(xiàn)在與JESD204B字母湯的“M”參數(shù)解耦。根據(jù)標(biāo)準(zhǔn),M 是每個(gè)鏈路的轉(zhuǎn)換器數(shù)量。在修改后的方案中,M 現(xiàn)在成為稱為虛擬轉(zhuǎn)換器的參數(shù)。盡管AD9680實(shí)際上只有兩個(gè)ADC通道(A和B),但DDC處于復(fù)數(shù)輸出模式時(shí),現(xiàn)在有四個(gè)不同的(16位)數(shù)據(jù)流連接到JESD204B接口。對(duì)于JESD204B接口,現(xiàn)在看起來(lái)有四個(gè)(虛擬)轉(zhuǎn)換器發(fā)送位流。因此,M = 4或轉(zhuǎn)換器乘法行為。在這種情況下,輸出線速率變?yōu)?/p>

AD9680的JESD204B接口的靈活性在這里變得顯而易見(jiàn),因?yàn)楦鶕?jù)接收邏輯(ASIC或FPGA)的線速可接受性,現(xiàn)在有兩種選擇。表1顯示了圖204所示AD9680設(shè)置中JESD2B接口的可用選項(xiàng)。

表 1.AD9680 ADC的JESD204B輸出接口的配置選項(xiàng)

|

# 虛擬 轉(zhuǎn)換器 M |

# 每個(gè)鏈路 L 的通道數(shù) | # 每幀八位字節(jié) F | 線速(千兆字節(jié)/通道) |

|

4 |

4 | 2 | 5 |

| 2 | 4 | 10 |

對(duì)于像AD9680這樣具有四個(gè)DDC的雙通道ADC,表2顯示了可用于各種配置的虛擬轉(zhuǎn)換器映射。

表 2.AD9680 ADC的JESD204B輸出接口的配置選項(xiàng)

|

支持的虛擬轉(zhuǎn)換器數(shù)量 |

芯片工作模式 | 芯片Q忽略 | 虛擬轉(zhuǎn)換器映射 | |||||||

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | |||

| 1 to 2 | Full Bandwidth Mode | Real or Complex | ADC A Samples |

ADC B Samples |

Unused |

Unused |

Unused |

Unused |

Unused | Unused |

| 1 | One DDC Mode | Real (I Only) |

DDC 0 I Samples |

Unused |

Unused |

Unused |

Unused |

Unused |

Unused |

Unused |

| 2 | One DDC Mode | Complex (I/Q) |

DDC 0 I Samples |

DDC 0 Q Samples |

Unused |

Unused |

Unused |

Unused |

Unused |

Unused |

| 2 | Two DDC Mode | Real (I Only) |

DDC 0 I Samples |

DDC 1 I Samples |

Unused |

Unused |

Unused |

Unused |

Unused | Unused |

| 4 | Two DDC Mode | Complex (I/Q) |

DDC 0 I Samples |

DDC 0 Q Samples |

DDC 1 I Samples |

DDC 1 Q Samples |

Unused |

Unused |

Unused |

Unused |

| 4 | Four DDC Mode | Real (I Only) |

DDC 0 I Samples |

DDC 1 I Samples |

DDC 2 I Samples |

DDC 3 I Samples |

Unused |

Unused |

Unused |

Unused |

| 8 | Four DDC Mode | Complex (I/Q) |

DDC 0 I Samples |

DDC 0 Q Samples |

DDC 1 I Samples |

DDC 1 Q Samples |

DDC 2 I Samples |

DDC 2 Q Samples |

DDC 3 I Sam |

8 |

-

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

8727瀏覽量

147437 -

驅(qū)動(dòng)器

+關(guān)注

關(guān)注

53文章

8259瀏覽量

146617 -

adc

+關(guān)注

關(guān)注

98文章

6513瀏覽量

545041

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

數(shù)據(jù)轉(zhuǎn)換器中的DDC和DUC通道如何工作?

MIMXRT1021和MIMXRT1024 ADC通道數(shù)

DDC114電流輸入型ADC的驅(qū)動(dòng)設(shè)計(jì)與實(shí)現(xiàn)

對(duì)于1對(duì)1觸發(fā)器,SAR通道是根據(jù)邏輯通道還是ADC通道數(shù)決定的?

使用DDC112時(shí),只使用其中一個(gè)通道,另外一個(gè)通道應(yīng)該如何處理?

labview魔術(shù)方陣小程序(一)

labview魔術(shù)方陣小程序(二)

說(shuō)變就變!讓您的ADC通道數(shù)翻倍

通過(guò)DDC魔法乘以ADC的虛擬通道數(shù)

高性能GSPS ADC為基于賽靈思FPGA的設(shè)計(jì)解決方案帶來(lái)板載DDC功能

淺析ADC的抽取

請(qǐng)問(wèn)DDC產(chǎn)生的余弦信號(hào)與ADC產(chǎn)生的數(shù)字信號(hào)相乘,經(jīng)過(guò)濾波和采樣后,怎么就得到相位數(shù)據(jù)了呢?

什么是DDC(顯示數(shù)據(jù)通道)/S-TFT

ADS54J66具有集成DDC的四通道、14位、500MSPS ADC數(shù)據(jù)表

具有集成DDC的ADC12J4000 12位4GSPS ADC數(shù)據(jù)表

將ADC的虛擬通道數(shù)與DDC魔術(shù)相乘

將ADC的虛擬通道數(shù)與DDC魔術(shù)相乘

評(píng)論