Tapped routing由Intel公司2015年3月份提出,主要用在處理器SKYLAKE平臺,DDR4的走線方式;

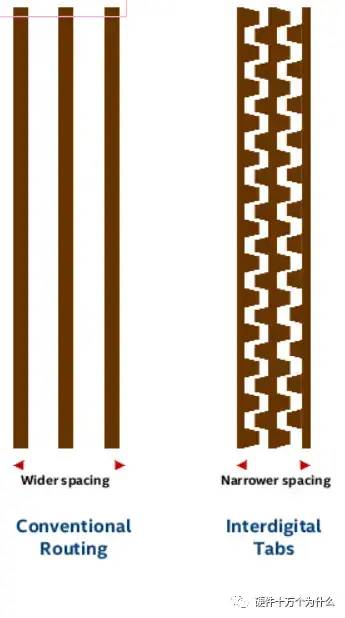

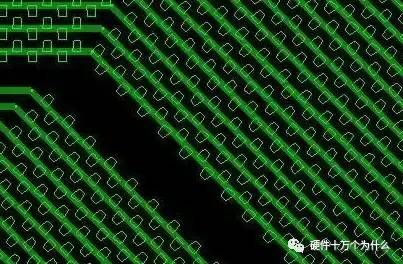

交叉手指狀的tabbed routing 使用面對相鄰差分線中tab之間空隙的交替梯形tab。這種tab可以壓縮走線,建立新的走線通道,并降低串擾,這可以走更長的線。這種tabbed routing專門針對外部層面。

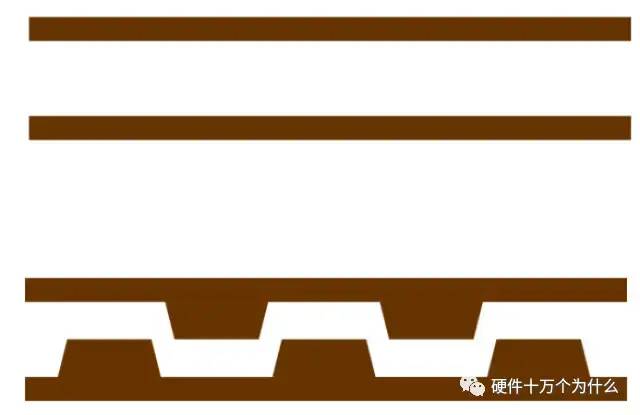

Tabbed Routing主要的方法是在空間比較緊張的區域(一般為BGA區域和DIMM插槽區域),減小線寬,而增加凸起的小塊(Tab),如下圖所示。

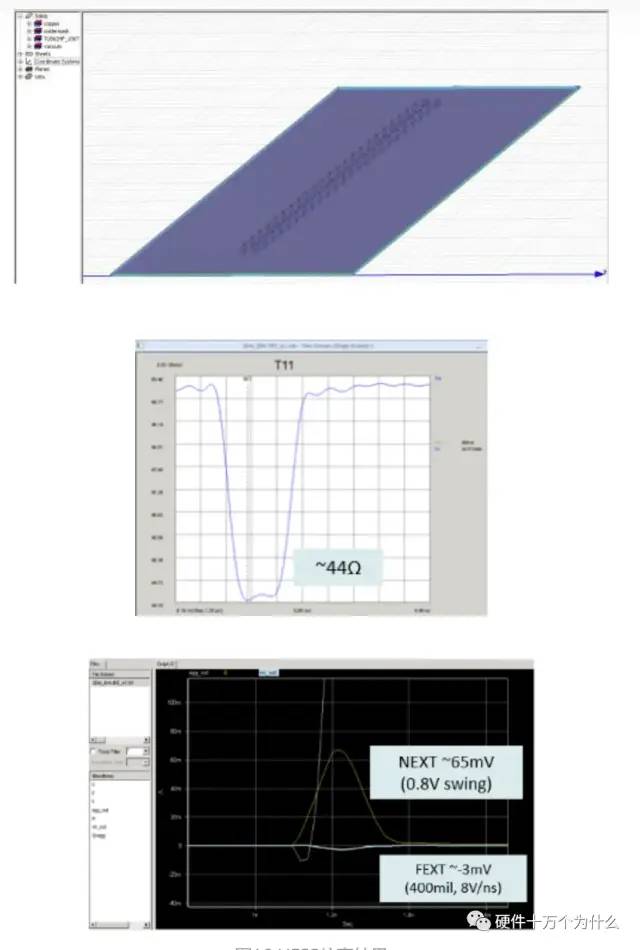

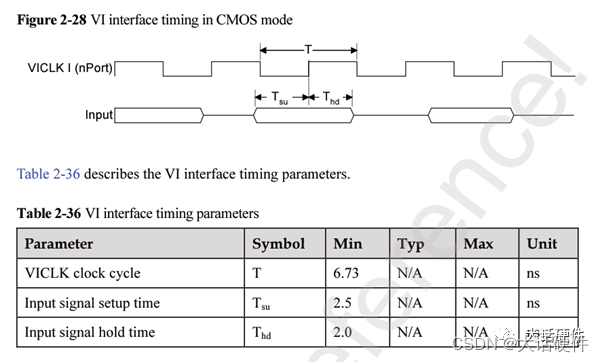

這種方法可以增加兩根線之間的互容特性而保持其電感特性幾乎不變,而增加的電容可以有效控制每一層的的阻抗,減小外層的遠端串擾。仿真結果如下圖所示。

由仿真結果可以看出來,該方法對阻抗和遠端串擾確實可以很好的平衡,當然,對于Tab的尺寸,需要根據實際PCB做詳細的仿真設計,Intel也提供了一些Tool可以參考。

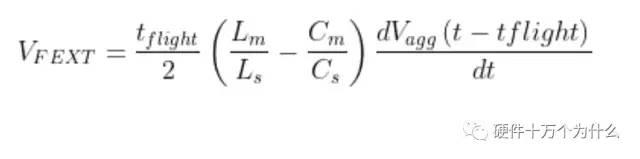

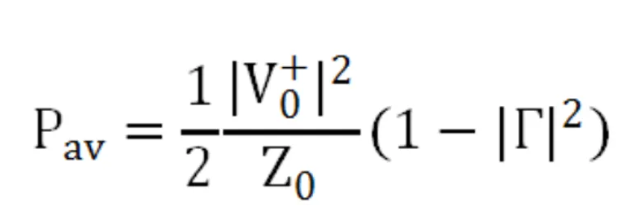

PCB走線必須傳輸電流和相關電磁場,場的傳輸受到PCB材料的介電特性的影響。在均勻介質中,場以相同的速度傳播(帶狀線),在非均勻結構中,場以不同的速度通過不同的介電材料傳播(微帶線)。這種傳播差異導致在非均勻結構中產生正向波,從而在遠端(接收器)處產生附加噪聲。這在均質結構中不會發生,這種影響的嚴重程度隨信號頻率的增加而增加。

接收端的遠端串擾就是奇模信號和偶模信號之間的傳播延時。對于互相耦合走線,遠端串擾的電壓由以下公式定義:

FEXT一般指遠端串音。遠端串音(Far-End Crosstalk)是串音的一種,指信號傳輸中平行的兩對線,干擾線對施加給被干擾線對遠端的串音。VFEXT是指源端串音導致的電壓變化。

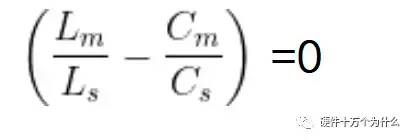

傳輸時間固定,為了消除前向串擾,可以讓感性容性關系為0,即:

因為感性已經固定,增加走線的tab(兩個線之間的距離和間距)可以調整容性。Cs是自容,Ls是自感,Cm是互容,Lm是互感。通過tab的調整,讓上面式子盡量為0。

所有的tabbed routing方案都會影響阻抗和噪聲。Pin Field區域的tab可以改善阻抗管控,可以用在所有層面,Pin field區域的tab看起來像是蛇形走線,實際的走線布局由pin field區域的實際需求決定。

Pin Field區域的Tabbed Routing不會管控阻抗到一個實際的值,它相當于提供了一個額外的電容元件,根據它來確定阻抗,以提供跨供應商的更一致的阻抗結果。對于傳統的pin field區域走線,阻抗會隨著板廠變化,板廠也不會管控此區域的走線阻抗。

交叉手指狀的tabbed routing 使用面對相鄰差分線中tab之間空隙的交替梯形tab。這種tab可以壓縮走線,建立新的走線通道,并降低串擾,這可以走更長的線

-

pcb

+關注

關注

4335文章

23237瀏覽量

402098 -

走線

+關注

關注

3文章

117瀏覽量

24041

原文標題:的走線方式;

文章出處:【微信號:LowHuangMakerSpace,微信公眾號:LowHuangMakerSpace】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

華邦電子安全閃存關鍵知識點

Kaggle知識點:7種超參數搜索方法

總結了8個常見的知識點

Docker-鏡像的分層-busybox鏡像制作

Aigtek功率放大器應用:電感線圈的知識點分享

后悔沒有早點看到:天線設計中的知識點!

Kaggle知識點:使用大模型進行特征篩選

硬件工程師面試基礎知識點

推拉力測試知識點介紹

汽車MCU芯片知識點梳理

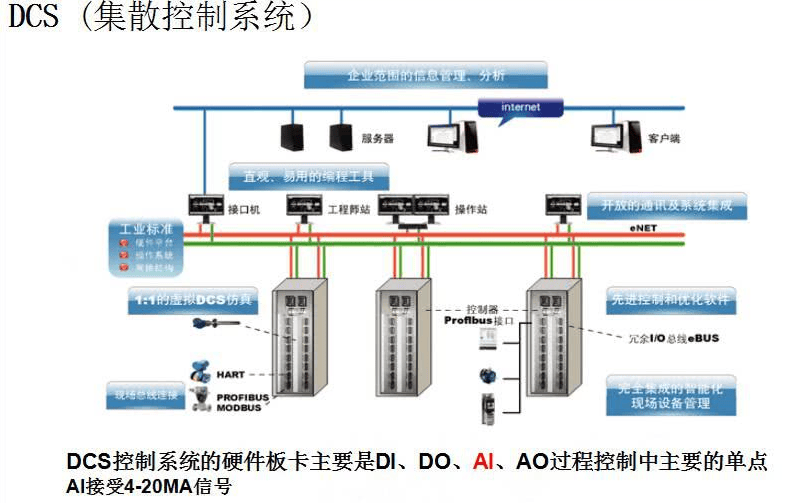

一篇搞定DCS系統相關知識點

評論