有沒有同學(xué)好奇,作為模擬芯片設(shè)計師,幾乎都在用CMOS工藝,大部分電路也是用的MOSFET,很少用BJT去設(shè)計大規(guī)模電路,那么,到底應(yīng)該對BJT這種device掌握到什么level呢?

其實我也不能下定論,我就說說我的掌握程度吧。

當然BJT基本的工作原理肯定要掌握的。

本文談一談BJT這個device、以及模擬IC設(shè)計師眼中對BJT的了解程度(只用過CMOS工藝的模擬IC設(shè)計師)。

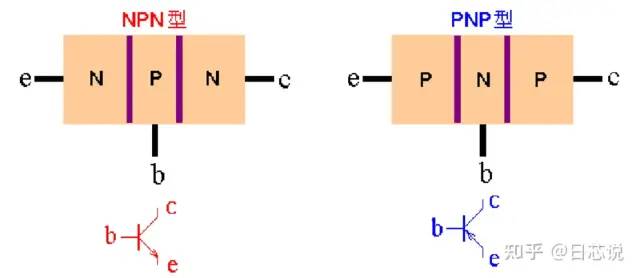

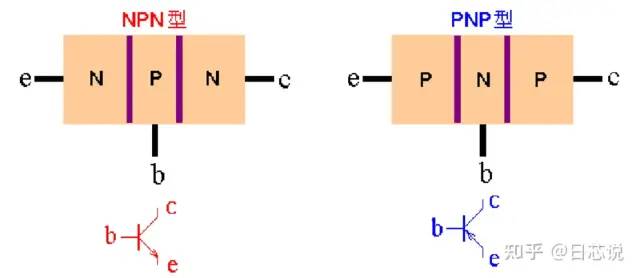

BJT即三極管,分為PNP和NPN型,簡單示意圖如下圖所示。

NPN和PNP

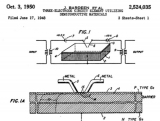

以NPN為例,其剖面圖如下圖,PNP的剖面圖想必你肯定也知道了。

NPN的剖面圖

說到這里,大家是不是好奇,具體到某一種工藝中,BJT的剖面圖會是什么樣子的?

讀研三年和工作幾個月,我只用過一種工藝,那就是大家都知道的CMOS工藝。

其實,“正宗”的BJT應(yīng)該是用Bipolar工藝制造的。但是現(xiàn)實用這種工藝不多,很多年前,確實會用這種工藝,由于Bipolar工藝process繁多,價格也比CMOS工藝貴,集成度也遠輸于CMOS,慢慢大家都不怎么用Bipolar工藝了。

在CMOS工藝中,BJT的制作和Bipolar不同,可以說,CMOS工藝中,不是“正宗”的BJT device,而是一種寄生的BJT。

不知道有沒有認真的同學(xué)發(fā)現(xiàn),你所用的單純的CMOS工藝中,只有PNP的BJT而沒有NPN的BJT?

在沒有DNW的CMOS工藝中,的確如此,且一般是縱向的寄生PNP三極管。why?

因為,沒有DNW的工藝中,只有全局P-sub是和P+是P型半導(dǎo)體,這里P-sub充當PNP的一個“P”,即集電極,P+充當PNP的另一個“P”,即發(fā)射極,n-well充當PNP的“N”,即基極,而不是Bipolar工藝真正意義上的N和P。

PS:至于為什么是縱向的而不是橫向的PNP,原因作者也布吉島啦。

這里,全局P-sub襯底永遠接VSS。

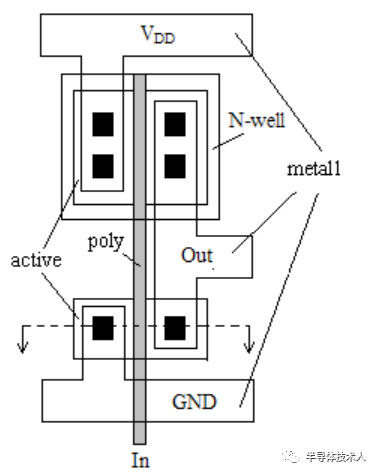

CMOS工藝中的縱向寄生PNP

看到這里,知道為什么普通CMOS工藝沒有NPN了嗎?

NPN正常工作的時候,基極發(fā)射極電壓Vbe應(yīng)大于其開啟電壓,也就是說基極電位大于0,但是CMOS工藝中p-sub永遠是VSS不可能大于0,因此p-sub是不能做NPN的基極的。

有同學(xué)會問了,能不能用兩個n-well做NPN的兩個“N”,用P+做NPN的“P”呢?

答案是不能。why?n-well外面的P+就是襯底接觸,也是接VSS的。

這里,建議有興趣的同學(xué)可以仔細畫一畫這些寄生BJT的剖面圖,結(jié)合CMOS工藝的特點進行分析,牢記BJT中遵循發(fā)射結(jié)正偏,集電結(jié)反偏的原理,看看在CMOS工藝中能否實現(xiàn)。

那么CMOS工藝中,就不能有PNP device了嗎?肯定不是。

在有DNW的CMOS工藝中或者有雙P-well的CMOS中,是可以有寄生的NPN的。

在DNW工藝中,DNW本身就是用來制造隔離的NMOS,DNW的存在使得NMOS的P襯底是”本地“的,即可以不接到全局p-sub上,因此就有了NPN中的基極"P"。

而在擁有雙P-well的CMOS的工藝中,多出來的P-well充當NPN的基極"P",如下圖:

淺阱NPN的剖面圖

但是,雙P-well,相比傳統(tǒng)CMOS,多了一層淺P阱mask,增加了成本。

在CMOS工藝中,縱向寄生PNP的β值不會很大,一般不會超過10,具體數(shù)據(jù)可查看PDK中關(guān)于Bipolar的擬合數(shù)據(jù)。為什么β很小,我們知道,基區(qū)的厚度越大,β越小。在CMOS工藝中,也就是n-well的厚度,是較大的,因此β會很小,然而這個厚度是我們designer不可控的,是由foundry決定的。

到現(xiàn)在為止,作為模擬IC設(shè)計師,我只在bandgap中用過BJT,而且用的也不是其對基極電流的放大作用,而是兩個BJT的Vbe差值與溫度成正比這個特性,如下圖。

PTAT電壓產(chǎn)生電路

mentor說,在ESD電路中,基本都是二極管和MOS,BJT幾乎不用。

因此,到現(xiàn)在為止,我對BJT的了解可以說很少,不多,但知道BJT的工作原理,足夠在CMOS工藝中進行電路設(shè)計,畢竟latch up效應(yīng)或者ESD中的GGNMOS和GGPMOS用到的寄生BJT的特性。

-

MOSFET

+關(guān)注

關(guān)注

147文章

7184瀏覽量

213459 -

BJT

+關(guān)注

關(guān)注

0文章

236瀏覽量

18197 -

模擬芯片

+關(guān)注

關(guān)注

8文章

629瀏覽量

51224

發(fā)布評論請先 登錄

相關(guān)推薦

怎么采用標準CMOS工藝設(shè)計RF集成電路?

《炬豐科技-半導(dǎo)體工藝》CMOS 單元工藝

采用CMOS工藝的射頻設(shè)計研究

基于CMOS下的像素陣列校正系統(tǒng)你了解多少呢?

淺談模擬IC設(shè)計師眼中的BJT

為什么BJT比CMOS速度要快?

什么是BCD工藝?BCD工藝與CMOS工藝對比

探索BJT、CMOS、DMOS等半導(dǎo)體工藝技術(shù)

HV-CMOS工藝制程技術(shù)簡介

CMOS工藝下的BJT你了解多少?

CMOS工藝下的BJT你了解多少?

評論