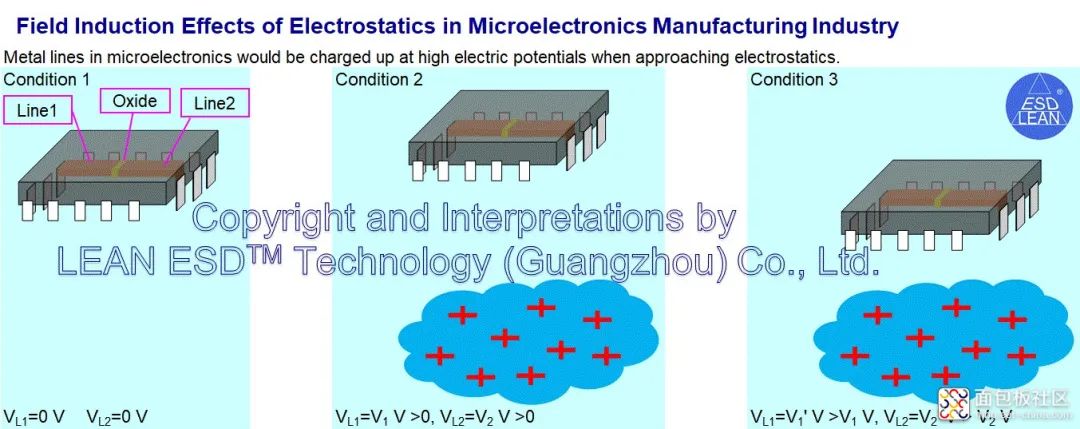

微電子制造中的靜電問題都是存在于眾多微小的細節之中。 微電子制造中存在大量的生產工序會產生并累積靜電。 靜電的直接影響之一就是通過靜電感應作用將臨近的微電子器件(確切而言,是其中的大量金屬線路)充電至高靜電位。

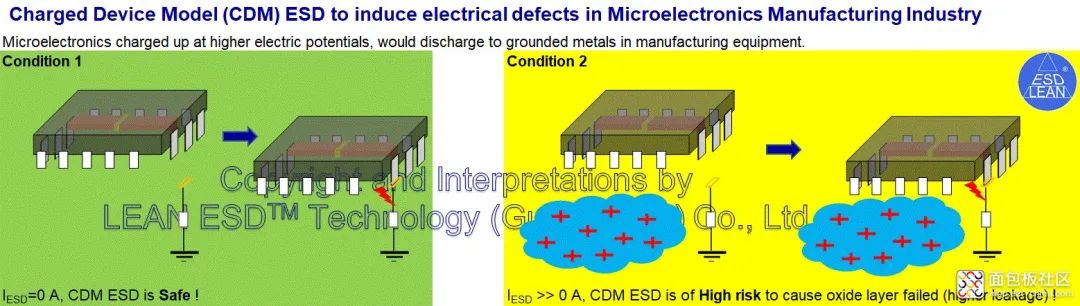

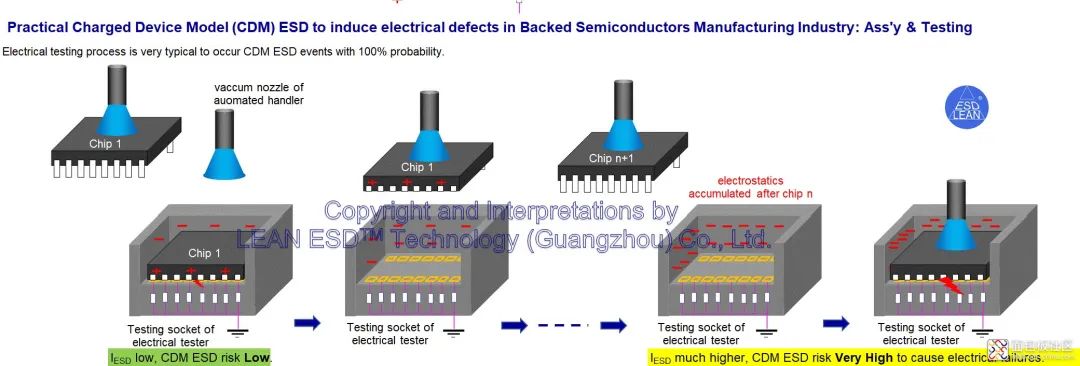

而微電子制造中涉及的許多電氣測試機臺(IC封測工廠就含有大量的電測工序),就是典型的CDM(Charged Device Model,器件帶電放電模型) ESD關鍵工序(100%會發生CDM ESD),由此導致微電子器件的電性不良風險(主要是器件中的絕緣膜層漏電流過大,如gate oxide)必須得到重視并采取有效的管控措施;

而電氣測試機臺中的testing socket(測試插座)尤其是其中的器件裝載導引機構大都采用絕緣塑膠或陶瓷材質,每顆器件的測試過程都會發生器件封裝體與testing socket導引機構件之間的摩擦靜電起電,隨著測試機臺測試越來越多的器件,如果testing socket上累積的靜電得不到及時的有效消除,越到后面測試的器件發生CDM ESD導致的電氣失效不良風險就越高。

當前基于28nm制程及以下的IC已經占比將近50%,其最高承受的CDM ESD電壓大部分不超過100V。其中,最新的7nm、5nm制程的5G IC,CDM耐壓更是降至50V以下,這種IC的設計與制程變化,給集成電路前段制造-Wafer Fab、集成電路后段制造-封裝與測試、以及SMT工廠的生產工藝中的ESD防護帶來了非常大的挑戰。

審核編輯 :李倩

-

ESD

+關注

關注

49文章

2062瀏覽量

173352 -

靜電

+關注

關注

1文章

508瀏覽量

36478 -

微電子

+關注

關注

18文章

388瀏覽量

41277

原文標題:現實中微電子制造領域的靜電問題[20230111]

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SCS 靜電管理計劃:用工業 4.0 解決方案克服電子行業的關鍵挑戰

求問帖!靜電消除器在電子半導體領域的具體應用與需求!

靜電對敏感電子元件的影響

靜電對電子設備的影響

微電子制造中的FIB-SEM雙束系統:技術應用與進展

現實中微電子制造領域的靜電問題

現實中微電子制造領域的靜電問題

評論